# Frequency Generation for ADPLLs in Automotive FMCW Radar using Nano-Scale CMOS

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

Lantao Wang,

M. Sc.

aus Lijiang, Yunnan, China

Berichter: Univ.- Prof. Dr.-Ing. Stefan Heinen Univ.- Prof. Dr.-Ing. Jürgen Oehm

Tag der mündlichen Prüfung: 25.04.2025

人生如逆旅,我亦是行人。

- 苏轼

Life is like a guest house; I, too, am but a traveler.

- Su Shi

#### **ACKNOWLEDGEMENT**

It has been such a long yet wonderful journey for me to finally be able to present this work. I come from a small city at an altitude of more than 2,400 m in the Hengduan Mountains of China. A mountain of around 5,600 m locates right at the doorstep of my hometown. Lying in the transitional area from the Yun-Gui Plateau to the Himalayas, despite the fame

for its spectacular landscape, my hometown remains till today very remote and non-industrialized. Surrounded by these high mountains, even visiting a county that is merely 100 km away would take more than 4 hours of driving on the twisted mountain road. It wasn't until 2010 that the first railway and, subsequently, in 2013, a motorway connected our town to the outer world. Growing up in such a remote area, being able to research cutting-edge topics in microelectronics alongside some of the brightest minds in the world was beyond anything I could have imagined.

First and foremost, I am deeply grateful to Prof. Dr.-Ing. Stefan Heinen for offering me the opportunity to work at the Integrated Analog Circuits and RF Systems Laboratory (IAS), and for generously sharing his remarkable experience and insights with me throughout my Ph.D. journey. I would also like to express my sincere appreciation to Dr.-Ing Ralf Wunderlich for his exceptional management at IAS, especially during the challenging time of the pandemic, which ensured the continuity of our research and teaching activities. Moreover, I would like to thank Prof. Dr.-Ing. Jürgen Oehm for his interest in my work and thorough review.

I would also like to thank my office colleague Markus Scholl, who not only guided me for the start of my journey at IAS, but also helped me settle smoothly in Aachen. My thanks go also to Michael Hanhart, who shared countless analog circuit design techniques and Cadence tricks. His enthusiasm for analog design has been, and will continue to be, an inspiration for me.

I would like to thank my tapeout teammates Jonas Meier, Tim Lauber, Johannes Bastl, Alexander Meyer, Kenny Vohl and Christopher Nardi. It was so much fun working with you guys: we learned together, proofread each other's manuscripts, and of course had so many interesting conversations

covering all kinds of topics. I am certain that I will never forget the beers we had together almost at midnight in the institute, right after the submission of the final GDS file of our first 28-nm tapeout.

Special thanks are due to Andreas Köllmann and Ulrich Möhlmann, who shared their profound experiences in all the aspects of PLL design with me. The discussion with them never failed to kindle new ideas. My thanks also go to Andreas Wichern who supported the crystal oscillator measurement.

I would like to extend my gratitude to Tobias Zekorn for his great work in the project coordination, to Fabian Speicher for solving tons of my tooling issues in the first year of this journey, and to Christoph Beyerstedt for sharing his expertise in simulation techniques.

I would also like to thank my colleagues Jan Grobe, Ricardo Heinen, Tim Lange, Erik Wehr, Léon Weihs, Johannes Kuhn and Jonas Zoche for all the enjoyable talks and countless unforgettable moments. Additionally, I would like to acknowledge our IT support team at IAS, especially Wladimir Oleschenko, Jonas Maubach and Dominik Makus, for solving all kinds of difficulties and maintaining an efficient work environment.

My thanks also go to my students Marc Fassbender, Running Guo, Adrian Arnold and Ozan Yildirim, who wrote their theses under my supervision. Their work has significantly contributed to the completion of this dissertation.

To my dear friends Xinghan Guo and Aohan Wang, thank you for the countless unforgettable adventures we had across Europe. Our trips together are the best stress relievers. Special thanks to Jiani Xiao, Xin Wang, Longwen Qin, Yuan Ji, and Dalin Sun for all the wonderful times and shared moments.

Last and most importantly, I would like to give my deepest thanks to my parents Rongxiang Wang and Yanling Li, for their unconditional love and support in every single choice I have made throughout my life.

I am always fascinated when I look back on the road, and not a single moment goes by without me feeling privileged to have so many wonderful people around me throughout this journey.

王澜涛 Lantao Wang Hamburg, Germany, September 2024

## **CONTENTS**

| Ac  | knov  | wledgement                                               | i    |

|-----|-------|----------------------------------------------------------|------|

| Li  | st of | Figures                                                  | vii  |

| Lis | st of | Tables                                                   | xiii |

| Lis | st of | Abbreviations                                            | xv   |

| Lis | st of | Symbols                                                  | xix  |

| 1   | Intr  | oduction                                                 | 1    |

|     | 1.1   | Research Contribution                                    | 3    |

|     | 1.2   | Thesis Organization                                      | 4    |

| 2   |       | damentals and System Consideration of Frequency Gen-     |      |

|     | erat  | tion Circuits                                            | 7    |

|     | 2.1   | Fundamentals of FMCW Radar                               | 7    |

|     |       | 2.1.1 Distance Measurement                               | 7    |

|     |       | 2.1.2 Velocity Measurement                               | 8    |

|     |       | 2.1.3 Fast-Chirp FMCW Radar Transceiver                  | 10   |

|     |       | 2.1.4 Frequency Synthesis with Phase-Locked Loops        | 11   |

|     | 2.2   | All-Digital Phase-Locked Loops                           | 15   |

|     | 2.3   | Noise                                                    | 17   |

|     | 2.4   | Phase Noise                                              | 20   |

| 3   | Lov   | v-Noise Digitally Controlled LC Oscillators              | 23   |

|     | 3.1   | Passive Devices                                          | 24   |

|     |       | 3.1.1 Inductor                                           | 24   |

|     |       | 3.1.2 Capacitor                                          | 28   |

|     | 3.2   | Phase Noise in LC Oscillator                             | 29   |

|     |       | 3.2.1 Theoretical Analysis of Phase Noise - LTI Approach | 29   |

|     |       | 3.2.2 LTV Approach for Phase Noise Calculation           | 32   |

|   |     | 3.2.3   | Brief Summary of Flicker Noise Upconversion Mech-         |

|---|-----|---------|-----------------------------------------------------------|

|   | 0.0 | C4      | anisms                                                    |

|   | 3.3 |         | ures of Oscillator Core                                   |

|   |     | 3.3.1   | Selection of Active Device Type                           |

|   |     | 3.3.2   | Selection of Tail Bias                                    |

|   |     | 3.3.3   | Class-B                                                   |

|   |     | 3.3.4   | Class-C                                                   |

|   |     | 3.3.5   | Class-D                                                   |

|   |     | 3.3.6   | Transformer-based LC Oscillator 40                        |

|   |     | 3.3.7   | Multi-Core LC Oscillator 47                               |

|   | 3.4 |         | hable Capacitors for DCO                                  |

|   |     | 3.4.1   | Resistor-biased SC                                        |

|   |     | 3.4.2   | CMOS-biased SC                                            |

|   |     | 3.4.3   | Constantly-conducting NMOS-biased SC 57                   |

|   |     | 3.4.4   | CCNMOS-biased SC for fine tuning 59                       |

|   |     | 3.4.5   | Design of SC Array                                        |

|   | 3.5 |         | ency Divider, Clock Distribution and Measurement Setup 63 |

|   | 3.6 | DCO I   | Prototypes                                                |

|   |     | 3.6.1   | Class-B DCO with 2nd Harmonic Tail Filter 67              |

|   |     | 3.6.2   | RC-biased Class-C DCO                                     |

|   |     | 3.6.3   | Summary of Experimental Results 80                        |

| 4 | Pow |         | pply for Low-Noise RF Applications 83                     |

|   | 4.1 | Funda   | mentals of Low-Dropout Regulator                          |

|   | 4.2 | Low-N   | Noise Linear Regulator                                    |

|   |     | 4.2.1   | Proposed LNLDO with On-chip Impedance Scaler 88           |

|   |     | 4.2.2   | Output Voltage Level Generator and Low-Pass Filter 90     |

|   |     | 4.2.3   | Error Amplifier                                           |

|   | 4.3 | Exper   | imental Results                                           |

| 5 | Cry |         | cillator with Start-up Acceleration 101                   |

|   | 5.1 | Mode    | ling of the Quartz Crystal                                |

|   | 5.2 | Oscilla | ator Architecture                                         |

|   |     | 5.2.1   | Pierce Oscillator                                         |

|   |     | 5.2.2   | Colpitts Oscillator                                       |

|   | 5.3 | Start-  | up Acceleration                                           |

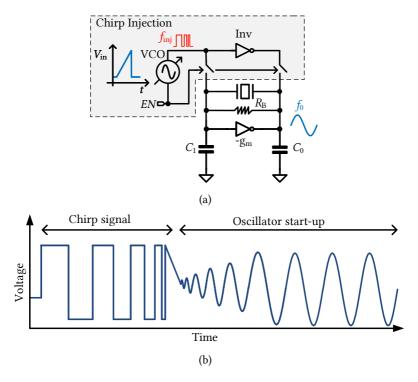

|   |     | 5.3.1   | Chirp Signal Injection                                    |

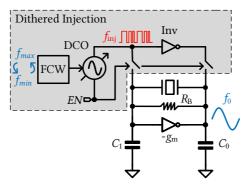

|   |     | 5.3.2   | Dithered Signal Injection                                 |

|   | 5.4 | Design  | n Prototypes                                              |

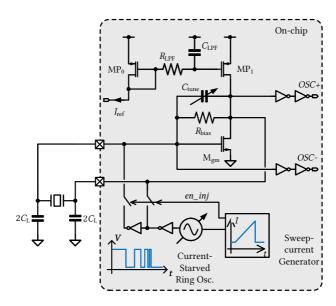

|   |     | 5.4.1   | Pierce Crystal Oscillator with Chirp Injection 109        |

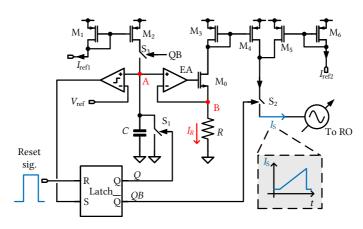

|   |     | 5.4.2   | Crystal Oscillator with Dithered Injection 113            |

| 6  | Con   | clusion and Outlooks                          | 121 |

|----|-------|-----------------------------------------------|-----|

|    | 6.1   | Conclusion                                    | 121 |

|    | 6.2   | Outlooks                                      | 122 |

|    |       | 6.2.1 Transformer-Based Regulated Class-C DCO | 123 |

|    |       | 6.2.2 Multi-Core DCO                          | 123 |

|    |       | 6.2.3 Fully Differential Crystal Oscillator   | 124 |

| Bi | bliog | raphy                                         | 127 |

| Α  | Pub   | lications                                     | 141 |

|    | A.1   | Peer-Reviewed Journal Papers                  | 141 |

|    | A.2   | Peer-Reviewed Conference Papers               | 141 |

|    | A.3   | Talk                                          | 142 |

| В  | CUF   | RRICULUM VITAE                                | 143 |

## LIST OF FIGURES

| 1.1  | Distance measurement using chirp signal                        | 2  |

|------|----------------------------------------------------------------|----|

| 1.2  | Micrographs of the 28 nm chips relevant to this thesis. (a)    |    |

|      | Project PANDA. (b) Project RedPANDA. (c) Project Cheetah       | 5  |

| 2.1  | Distance measurement using chirp signal                        | 7  |

| 2.2  | Chirp FMCW radar velocity and distance measurement             | 9  |

| 2.3  | Fast chirp FMCW radar waveform                                 | 10 |

| 2.4  | Architecture of a commercial fast-chirp FMCW radar transceiver |    |

|      | [28]                                                           | 11 |

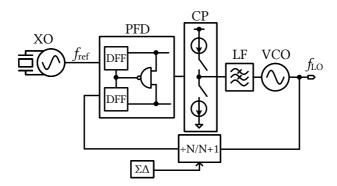

| 2.5  | Block diagram of an integer-N analog PLL                       | 12 |

| 2.6  | Structure of a fractional-N PLL                                | 13 |

| 2.7  | System overview of a commercial RF-CMOS fast-chirp fre-        |    |

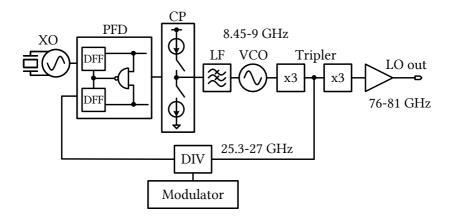

|      | quency synthesizer [33]                                        | 14 |

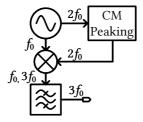

| 2.8  | Architecture of a self-mixed frequency tripler [34]            | 14 |

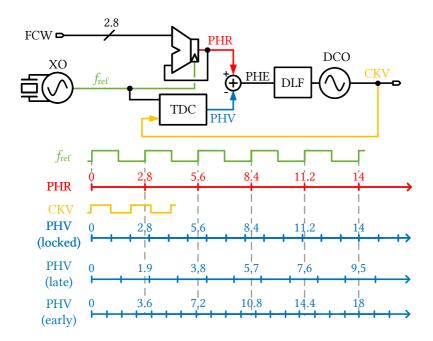

| 2.9  | Functioning principle of the ADPLL                             | 15 |

| 2.10 | Schematic and functioning principle of the TDC                 | 17 |

| 2.11 | Block diagram of the ADPLL implemented in this thesis work.    | 18 |

| 2.12 | Resistor thermal noise modeled by (a) voltage source and (b)   |    |

|      | current source                                                 | 18 |

| 2.13 | Thermal noise model of a MOSFET                                | 19 |

| 2.14 | Noise profile of a MOSFET                                      | 20 |

| 2.15 | Waveform and spectrum of an (a) ideal and (b) realistic LO     | 21 |

| 2.16 | Influence of LO phase noise: reciprocal mixing                 | 22 |

| 2.17 | Noise profile of a PLL                                         | 22 |

| 3.1  | 3D illustration of an integrated differential center-tapped O- |    |

|      | shape inductor                                                 | 25 |

| 3.2  | Model of a center-tapped inductor. (a) Simple model with       |    |

|      | series resistors. (b) Lumped model generated by Cadence EMX.   | 26 |

| 3.3  | Layout of an 8-shape inductor                                  | 27 |

|      |                                                                |    |

| 3.4  | Illustration of (a) current distribution due to skin effect and           |    |

|------|---------------------------------------------------------------------------|----|

|      | (b) simulated O-shape coil inductance and quality across fre-             |    |

|      | quency in room temperature in a 28 nm CMOS using EMX                      | 27 |

| 3.5  | (a) Symbol and cross-section of a n-type MOS capacitor. (b)               |    |

|      | 3-D illustration of a fringe MOM capacitor                                | 28 |

| 3.6  | General model of an LC oscillator                                         | 30 |

| 3.7  | Transfer function of an LC oscillator for the noise current               | 30 |

| 3.8  | LC oscillator phase noise profile                                         | 31 |

| 3.9  | Illustration of LC oscillator as a LTV system in terms of phase           |    |

|      | [58]                                                                      | 33 |

| 3.10 | Noise up-conversion [57]                                                  | 34 |

| 3.11 | Structures of (a) NMOS-only, (b) PMOS-only and (c) CMOS                   |    |

|      | LC oscillator core                                                        | 36 |

| 3.12 | (a) Tail current source and (b) tail resistor biased LC oscillators.      | 38 |

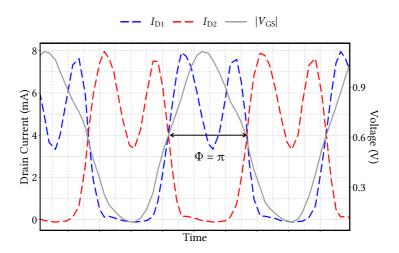

| 3.13 | Simulated gate-source voltage and drain current of g <sub>m</sub> devices |    |

|      | in a class-B LC oscillator                                                | 39 |

| 3.14 | (a) Illustration of one $g_m$ transistor entering deep-triode re-         |    |

|      | gion and (b) the equivalent tank schematic [44]                           | 40 |

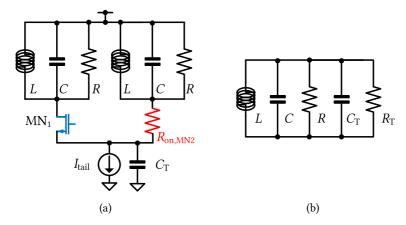

| 3.15 | Structure of an NMOS class-B LC oscillator with second har-               |    |

|      | monic tail filter.                                                        | 41 |

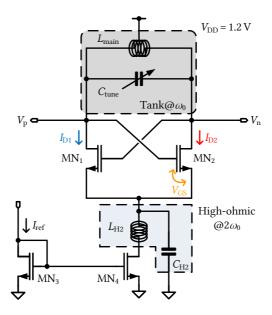

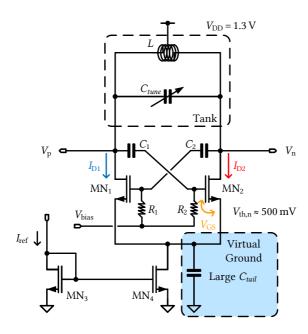

| 3.16 | Schematic of an RC-biased NMOS class-C LC oscillator                      | 42 |

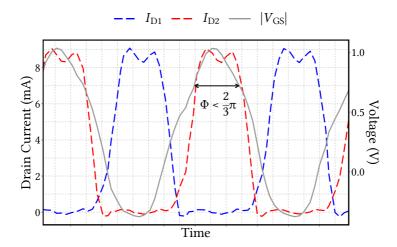

| 3.17 | Simulated gate-source voltage and drain current of g <sub>m</sub> devices |    |

|      | in a class-C LC oscillator                                                | 43 |

| 3.18 | Schematic of an NMOS class-D LC oscillator                                | 44 |

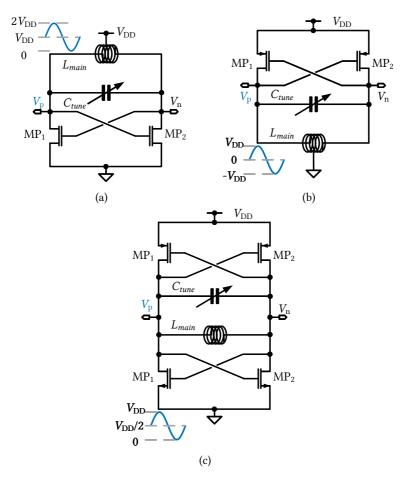

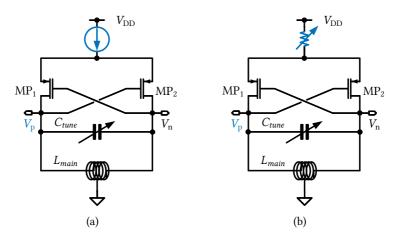

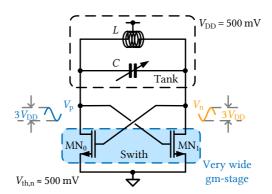

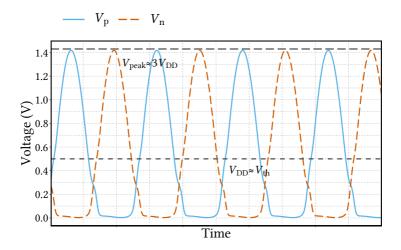

| 3.19 | 1 0                                                                       | 45 |

| 3.20 | Examples of transformer-based LC oscillators. (a) Implicit                |    |

|      | common-mode resonator [74] and (b) class-F VCO [75]                       | 46 |

| 3.21 | (a) Block diagram and (b) simplified layout floor-plan of a               |    |

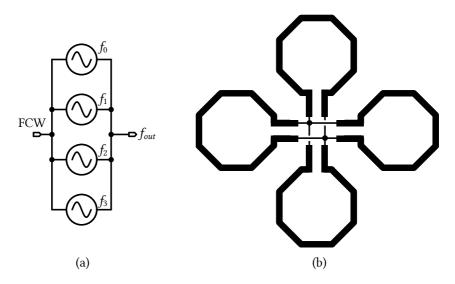

|      | quad-core LC oscillator                                                   | 47 |

| 3.22 | Equivalent circuits of (a) a general LC oscillator, and the               |    |

|      | switchable capacitor in (a) on state and (b) off state                    | 49 |

| 3.23 | Testbench of the switchable capacitor unit cell                           | 53 |

| 3.24 | (a) The schematic and (b) the simulated $\Delta C$ and quality factor     |    |

|      | of resistor-biased SC over the resistance                                 | 54 |

| 3.25 | Simulated oscillator transient response using resistor biased SC.         | 55 |

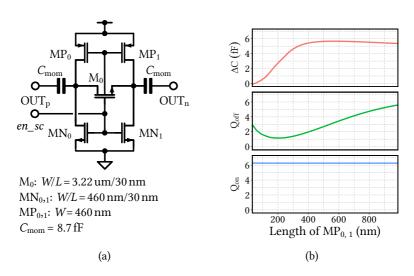

| 3.26 | (a) The schematic and (b) the simulated $\Delta C$ and quality factor     |    |

|      | of CMOS-biased SC over the length of PMOS pull-up transistors.            | 56 |

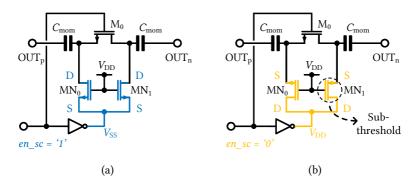

| 3.27 | Schematic and function principle of the proposed CCNMOS                   |    |

|      | biased SC. (a) On state and (b) off state                                 | 57 |

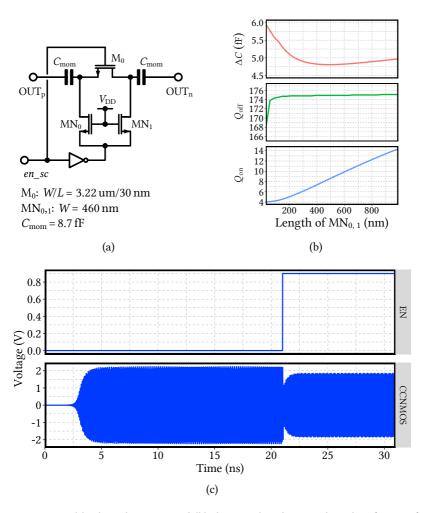

| 3.28 | (a) The schematic and (b) the simulated $\Delta C$ and quality factor     |    |

|      | of the proposed constantly-conducting NMOS biased SC                      | 58 |

| 3.29 | (a) Schematic, (b) on-state, (c) off-state equivalent circuits and |    |

|------|--------------------------------------------------------------------|----|

|      | (d) simplified layout of a fine-tuning SC cell                     | 61 |

| 3.30 | Illustration of switchable capacitor bank formation schemes.       |    |

|      | (a) Binary-Weighted. (b) Unitary-weighted                          | 62 |

| 3.31 | Potential non-monotonic frequency tuning behavior of a DCO         |    |

|      | with a binary-weighted SC array.                                   | 62 |

| 3.32 | Schematic of the squarer                                           | 64 |

| 3.33 | Schematic of the on-chip RF clock distribution                     | 64 |

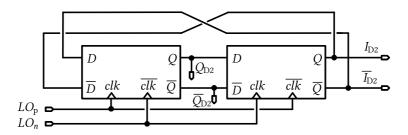

| 3.34 | Schematic of the divide-by-2 frequency divider                     | 65 |

| 3.35 | Schematic of the differential D-latch                              | 65 |

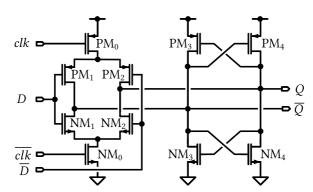

| 3.36 | Measurement setup with the open-drain buffer                       | 66 |

| 3.37 | Measurement board used in this work.                               | 66 |

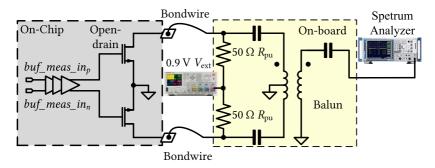

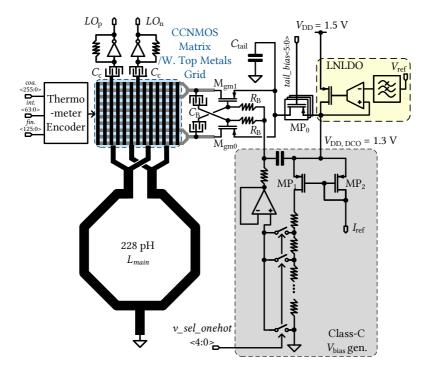

| 3.38 | Detailed schematic of the proposed class-B DCO using CCN-          |    |

|      | MOS SC bank                                                        | 67 |

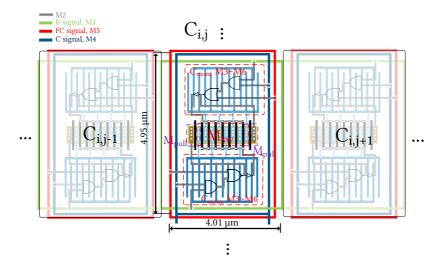

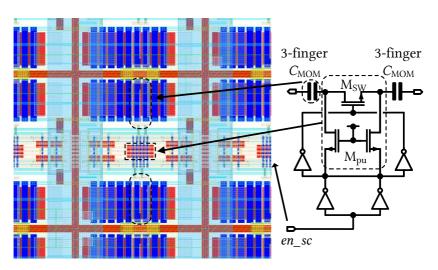

| 3.39 | Simplified layout of a coarse SC in the tuning bank matrix.        |    |

|      | Metal 1 and its interconnection are not shown for better visi-     |    |

|      | bility.                                                            | 68 |

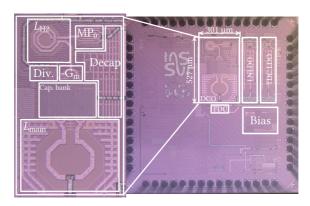

| 3.40 | Chip micrograph of the class-B DCO prototype, whose active         |    |

|      | area is $0.13 \text{ mm}^2$                                        | 69 |

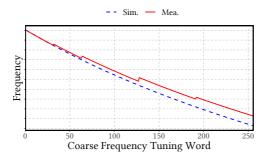

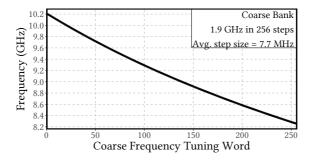

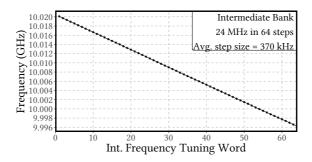

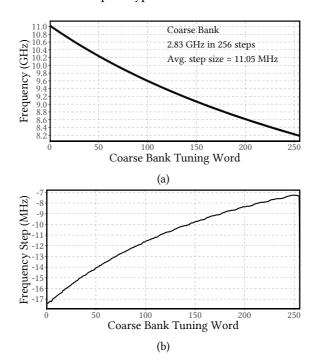

| 3.41 | Measured coarse bank frequency tuning                              | 70 |

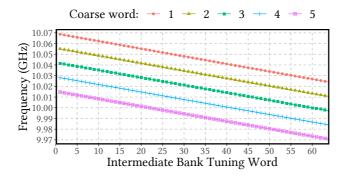

| 3.42 | Measured intermediate bank frequency tuning around 10 GHz.         | 70 |

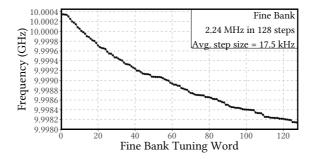

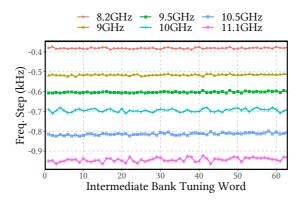

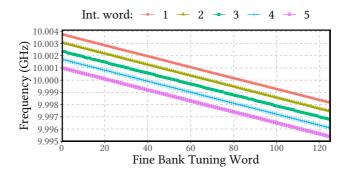

| 3.43 | Measured fine bank frequency tuning around 10 GHz                  | 71 |

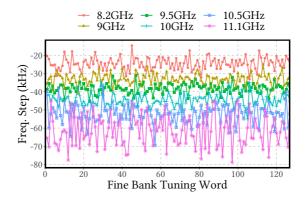

| 3.44 | Measured fine bank frequency tuning step                           | 71 |

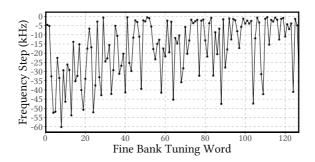

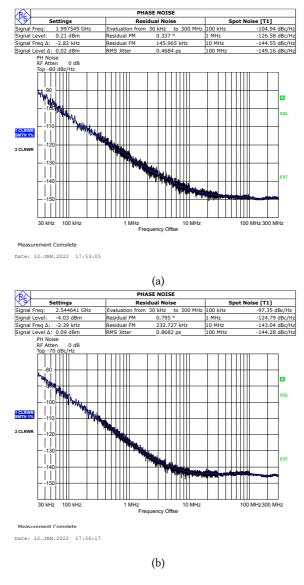

| 3.45 | Measured phase noise at carrier frequency of (a) 8 GHz (b)         |    |

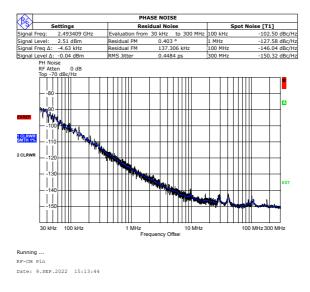

|      | 10.2 GHz, with frequency ÷4 output                                 | 72 |

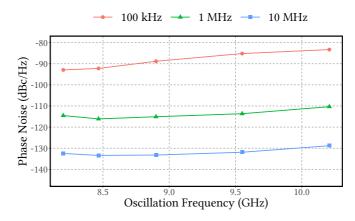

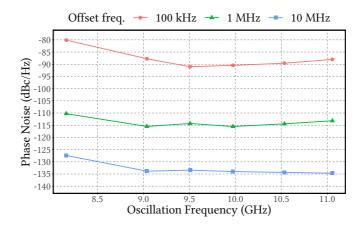

| 3.46 | Measured phase noise across the oscillator tuning range            | 73 |

| 3.47 | Simplified layout of the proposed class-C DCO, showing the         |    |

|      | blocks floorplan                                                   | 74 |

| 3.48 | Layout of SC cell for fine tuning using customized fringe          |    |

|      | capacitor                                                          | 75 |

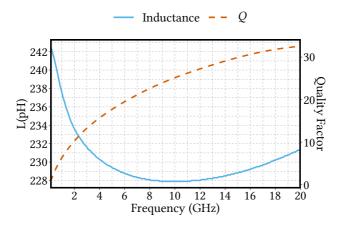

| 3.49 | Simulated inductance and quality factor of the coil                | 76 |

| 3.50 | Micrograph of the class-C DCO prototype                            | 76 |

| 3.51 | Measured class-C DCO prototype coarse frequency tuning.            |    |

|      | (a) Tuning range. (b) Coarse bank frequency tuning step            | 77 |

| 3.52 | Measured DCO intermediate bank tuning around 10 GHz,               |    |

|      | with 5 consecutive coarse bank steps                               | 78 |

| 3.53 | Measured intermediate bank tuning resolution across the            |    |

|      | DCO tuning range                                                   | 78 |

| 3.54 | Measured DCO fine bank tuning around 10 GHz, with 5 con-           |    |

|      | secutive intermediate bank steps.                                  | 79 |

| 3.55 | Measured fine bank tuning resolution across the DCO tuning range             | 79  |

|------|------------------------------------------------------------------------------|-----|

| 3.56 | Measured class-C DCO phase noise at 10 GHz, with the ÷4                      | ,,  |

| 3.30 | output                                                                       | 80  |

| 3.57 | Measured phase noise across the class-C oscillator tuning range.             | 81  |

| 4.1  | Power domain separation of an ADPLL using LDO                                | 83  |

| 4.2  | (a) The schematic and (b) the simulated $\Delta C$ and quality factor        | -   |

| 1.2  | of resistor-biased SC over the resistance.                                   | 84  |

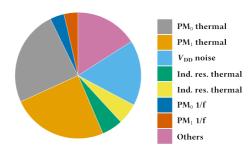

| 4.3  | Simulated major phase noise contributors in a well-designed                  |     |

|      | tail voltage-biased LC oscillator.                                           | 85  |

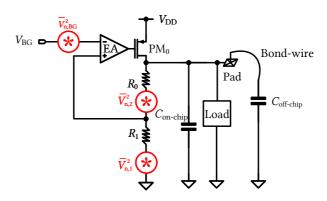

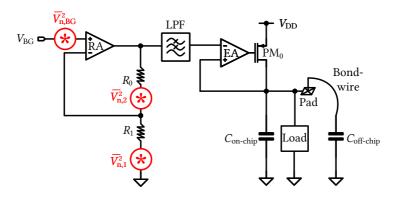

| 4.4  | Schematic of a traditional LDO including noise sources                       | 86  |

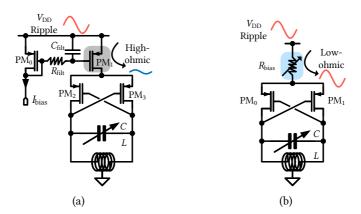

| 4.5  | Structure of a low-noise LDO                                                 | 88  |

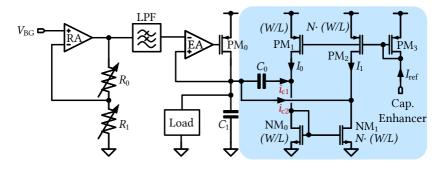

| 4.6  | Structure of the LNLDO with on-chip capacitance enhancer.                    | 89  |

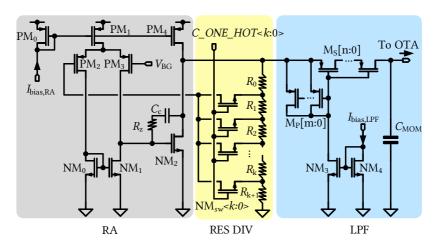

| 4.7  | Detailed schematic of the LNLDO output voltage level gener-                  |     |

|      | ator and low-pass filter                                                     | 90  |

| 4.8  | Schematic of the LNLDO folded-cascode error amplifier with                   |     |

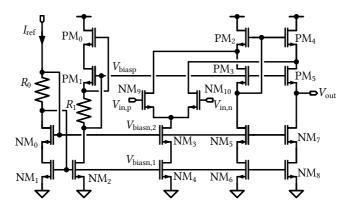

|      | self biasing                                                                 | 92  |

| 4.9  | Chip micrographs of the LNLDO prototypes with (a) class-B                    |     |

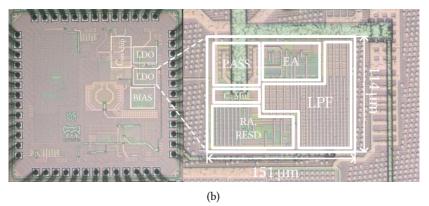

|      | DCO and (b) class-C DCO                                                      | 93  |

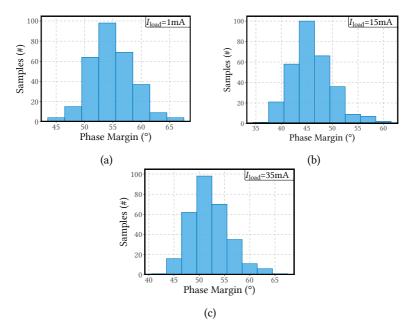

| 4.10 | Global and local mismatch of the phase margin of OTA-PM <sub>0</sub>         |     |

|      | loop based on simulation using schematic. (a) $I_{load}$ =1 mA. (b)          |     |

|      | $I_{\text{load}}$ =15 mA. (c) $I_{\text{load}}$ =35 mA                       | 94  |

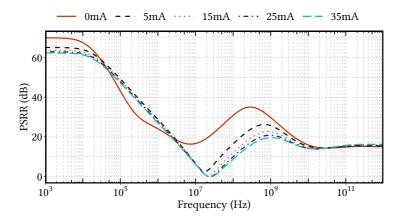

| 4.11 | Post-layout simulated PSRR with different load current values.               | 95  |

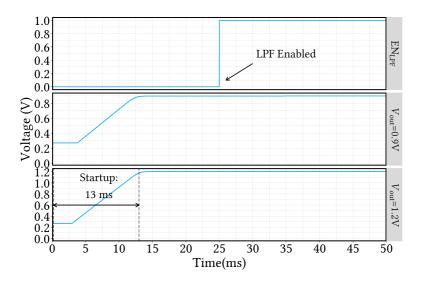

| 4.12 | Post-layout simulated LNLDO startup behavior                                 | 96  |

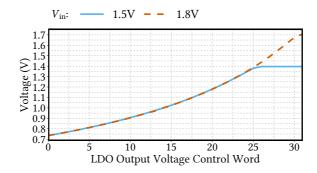

| 4.13 | Measured output voltage tunning range                                        | 97  |

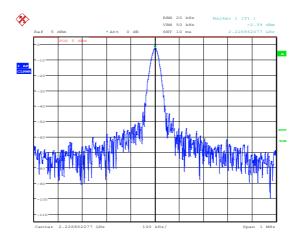

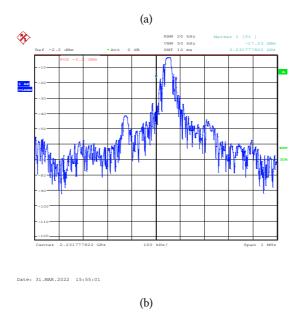

| 4.14 | Measured DCO output signal spectrum(a) with the LNLDO                        |     |

|      | and (b) with an external clean power supply                                  | 99  |

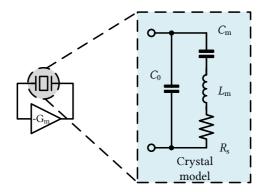

| 5.1  | Equivalent circuit of a quartz crystal                                       | 102 |

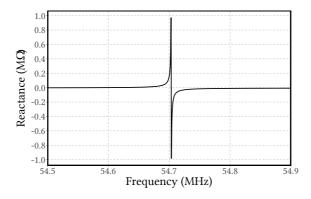

| 5.2  |                                                                              | 103 |

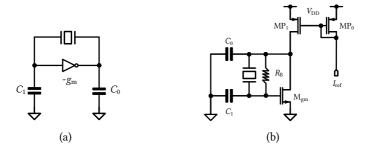

| 5.3  | Pierce crystal oscillator. (a) General configuration. (b) A                  |     |

|      |                                                                              | 104 |

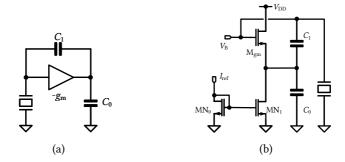

| 5.4  | Colpitts crystal oscillator. (a) General configuration. (b) A                |     |

|      |                                                                              | 105 |

| 5.5  | $Pierce\ crystal\ oscillator\ with\ constant\ frequency\ signal\ injection.$ | 106 |

| 5.6  | (a) General schematic and (b) startup waveform of a Pierce                   |     |

|      | ,                                                                            | 107 |

| 5.7  | 1 , 5 ,                                                                      | 108 |

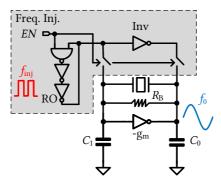

| 5.8  | Top-level schematic of the proposed Pierce crystal oscillator                |     |

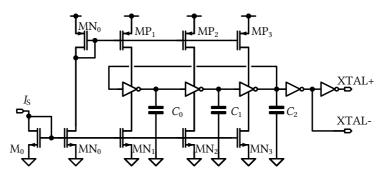

|      | with chirp signal injection                                                  | 109 |

| 5.9  | Schematic of the sweep-current generator                        | 110 |

|------|-----------------------------------------------------------------|-----|

| 5.10 | Schematic of the current-starved ring oscillator                | 111 |

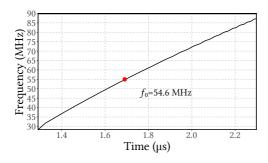

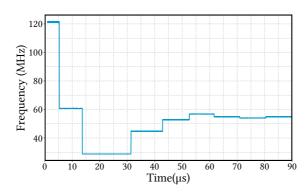

| 5.11 | Simulated frequency of the current-starved oscillator during    |     |

|      | injection phase                                                 | 112 |

| 5.12 | Simulated crystal oscillator phase noise (a) at tt corner and   |     |

|      | (b) with global and local mismatch                              | 112 |

| 5.13 | Simulated startup acceleration with chirp injection             | 113 |

| 5.14 | Top-level of the proposed Pierce crystal oscillator with shaped |     |

|      | dithered injection and negative resistance boost                | 114 |

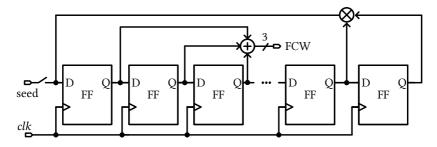

| 5.15 | Schematic of the Gaussian-shaped pseudo-random control          |     |

|      | word generator.                                                 | 115 |

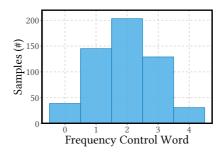

| 5.16 | Simulated Gaussian-shaped FCW distribution                      | 115 |

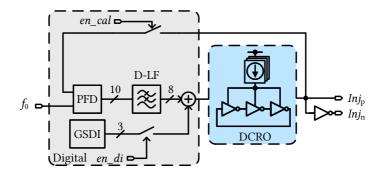

| 5.17 | Control scheme for the digitally controlled ring oscillator     | 116 |

| 5.18 | Simulated DCRO calibration                                      | 116 |

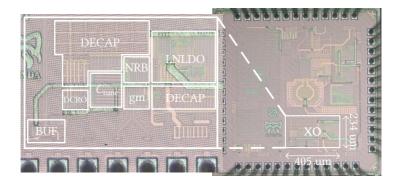

| 5.19 | Chip micrograph of the proposed crystal oscillator              | 117 |

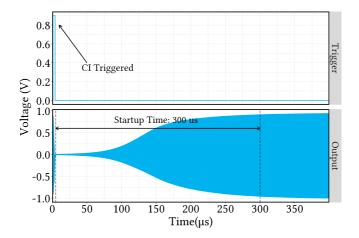

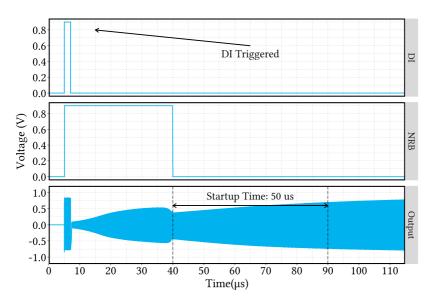

| 5.20 | Simulated startup behavior of the proposed crystal oscilla-     |     |

|      | tor with Gaussian-shaped dithered injection and negative        |     |

|      | resistance boost                                                | 118 |

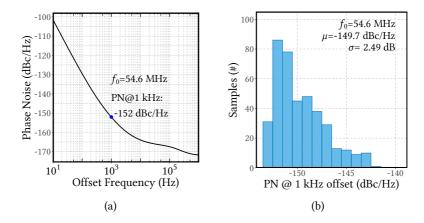

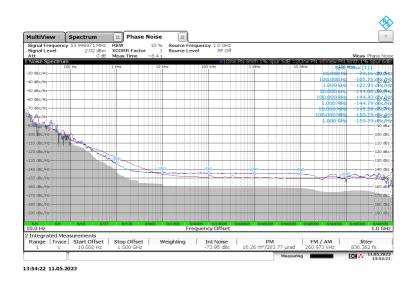

| 5.21 | Measured crystal oscillator phase noise                         | 118 |

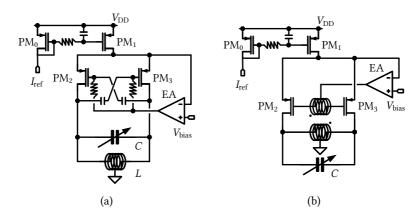

| 6.1  | Schematic of class-C DCO with regulation using (a) RC feed-     |     |

|      | back and (b) transformer feedback [77]                          | 123 |

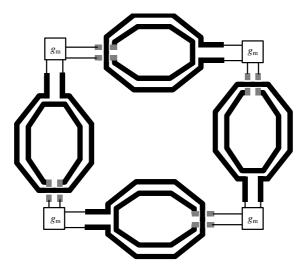

| 6.2  | A quadcore transformer based DCO [107]                          | 124 |

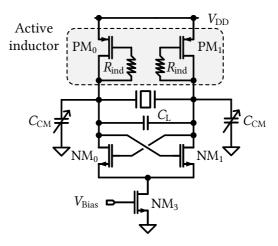

| 6.3  | A fully differential crystal oscillator using active inductors  |     |

|      | [106]                                                           | 125 |

|      |                                                                 |     |

### LIST OF TABLES

| 3.1 | Performance comparison of state-of-the-art multi-gigahertz DCO  | 82  |

|-----|-----------------------------------------------------------------|-----|

| 4.1 | Post-layout Simulated LNLDO Output Noise                        | 97  |

| 4.2 | Low-noise LDO performance comparison                            | 98  |

| 5.1 | Typical parameters of a 54 MHz quartz crystal                   | 102 |

| 5.2 | Model parameters of the used quartz crystal                     | 104 |

| 5.3 | Performance comparison of state-of-the-art crystal oscillators. | 119 |

### LIST OF ABBREVIATIONS

ACC autonomous cruise control

ADC analog-to-digital converter

ADPLL all-digital phase-locked loop

AM amplitude modulation

**ASIC** application-specific integrated circuit

**CCNMOS** constantly-conducting NMOS

**CI** chirp signal injection

CKV frequency-variable DCO clock CMF carrier mobility fluctuation

**CMOS** complementary metal-oxide semiconductor

**CNF** carrier number fluctuation

**CP** charge pump

DAC digital-to-analog converterDCO digitally-controlled oscillatorDCRO digitally-controlled ring oscillator

DDS direct digital synthesizer

DFLL digital frequency-locked loop

DI dithered signal injection

**DLF** digital loop filter

**DSP** digital signal processing

**EA** error amplifier

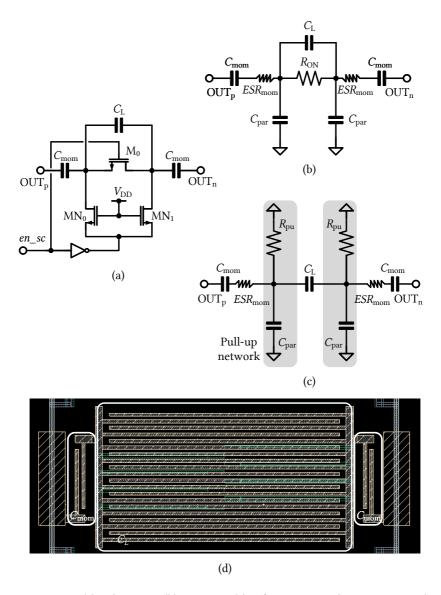

ESR equivalent series resistance

EVM error vector magnitude

FCW frequency control word

FFT fast Fourier transform

FMCW frequency-modulated continuous-wave

**FoM** figure-of-merit

IF intermediate frequency ISF impulse sensitivity function

**LDO** low-dropout regulator

**LF** loop filter

**LFSR** linear feedback shift register

**LNA** low-noise amplifier

LNLDO low-noise low-dropout regulator

LO local oscillator

LPF low-pass filter

LSB least significant bit

LTI linear time-invariant

LTV linear time-variant

**MEMS** micro-electro-mechanical systems

MIM metal-insulator-metal

MIMO multiple-input and multiple-output

MOM metal-oxide-metal

MOS metal-oxide-semiconductor

MSB most significant bit

NRB negative resistance boost

**OTA** operational transconductance amplifier

PA power amplifier

PCB printed circuit board

PFD phase frequency detector

PHE phase error **PHR** reference phase **PHV** variable clock phase PLL phase-locked loop PM phase modulation **PSD** power spectral density **PSR** power supply rejection PSRR power supply rejection ratio **PVT** process, voltage and temperature

**RA** reference amplifier

radar radio detection and ranging

**RF** radio frequency

**RFIC** radio-frequency integrated circuit

RMS root mean square RO ring oscillator  $\mathbf{R}\mathbf{X}$ receiver

SC switchable capacitor SNR signal-to-noise ratio SoC system-on-chip

SPI serial peripheral interface

SSB single-sided band

TDC time-to-digital converter

TR tuning range TXtransmitter

VCO voltage controlled oscillator **VGA** variable gain amplifier

#### LIST OF SYMBOLS

**B** bandwidth of a chirp signal

$c_0$  speed of light

**C**<sub>mom</sub> capacitance of MOM capacitor

$C_{off}$  off-state capacitance  $C_{on}$  on-state capacitance  $Q_{off}$  off-state quality factor  $Q_{on}$  on-state quality factor  $R_{on}$  on-state resistance

$egin{array}{ll} C_{

m ox} & {

m capacitance~per~unit~area~of~the~gate~oxide} \ \Delta C & {

m difference~of~on-~and~off-state~capacitance} \ ESR_{

m mom} & {

m equivalent~series~resistance~of~MOM~capacitor} \ \end{array}$

$f_0$  carrier frequency

$f_{

m beat}$  beat frequency in FMCW radar receiver  $f_{

m r}$  range caused frequency shift in the radar echo

signal

$C_{par}$  parasitic capacitance  $f_{res}$  oscillator tuning resolution  $f_{T}$  transit frequency of a transistor

$f_{

m v}$  Doppler effect frequency shift in the radar echo

signal

γ noise coefficient of MOSFET

$V_{

m th}$  threshold voltage

#### **CHAPTER 1**

#### INTRODUCTION

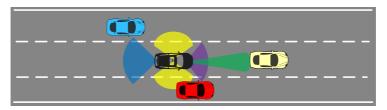

Since the early 1970s, applications of radio detection and ranging (radar) in automobiles have drawn significant attention from both industry and academia, as it is a highly effective method to avoid collisions and reduce the accident rate. However, because of the bulky size, it was very difficult to integrate radar in a commercial product [1]. In 1999, Mercedes-Benz became the first automobile company to equip a radar-based autonomous cruise control (ACC), so-called *DISTRONIC*, in its S-class, and other car companies, such as Nissan and BMW, quickly followed up in 2000 [2, 3]. Since then, radar sensor technology has advanced rapidly, aided by down-scaling technologies that have made these systems more affordable and easier to integrate. Today, automotive radar systems are widely employed across various products and manufacturers. Fig. 1.1 shows the general categories of the automotive radars used in a modern vehicle. Based on their different maximum detectable range, they are classified as long-range radar, medium-range radar and short-range radar, each suited for different driving scenarios [4].

Modern radar systems have undergone a significant shift in operating frequency, moving from the 24/26 GHz band to the 77-81 GHz band. One of the primary reasons for this shift is that antennas operating in the 77 GHz band are considerably smaller compared to those in the 24/26 GHz band, enabling the installation of larger arrays of 77 GHz radar antennas to achieve better angular measurement resolution. Additionally, the 77-81 GHz band offers a wider bandwidth of 4 GHz, which significantly enhances the resolution of distance and velocity measurements, whereas the narrow 24 GHz band provides only a 200 MHz bandwidth. Furthermore, regulatory standards set by the European Telecommunications Standards Institute (ETSI) [5] and the Federal Communications Commission (FCC) [6] have restricted the use of the ultra-wide-band from 21.65-26.65 GHz in both Europe and the U.S. effective 01. January 2022 [7].

However, designing a system in 77-81 GHz is more challenging and has stricter requirement on the technology. Conventionally, automotive semiconductor companies use compound technologies such as GaAs or SiGe BiCMOS

- Long Range Radar: ACC, Automatic Emergency Braking, Forward Collision Warning

- Short Range Radar: Park Assist, Junction Assist

- Medium Range Radar: Cross Traffic Alert

- Medium Range Radar: Blind Side Detection, Rear Collision Warning

Figure 1.1: Distance measurement using chirp signal.

to design and fabricate their radar transceivers, e.g. NXP [8] and Infineon [9]. But the cost of fabrication in these technologies is very high and 77 GHz radar could therefore only be equipped in the premium or luxury vehicles. On the other hand, the fabrication cost in a complementary metal-oxide semiconductor (CMOS) technology is much more affordable due to its high yield and a much higher level of integration. Hence, implementing automotive radar systems in a complementary metal-oxide semiconductor (CMOS) technology is of great value in expanding the usage of radars across all traffic participants to reduce casualties in the accident.

However, unlike in a e.g. SiGe technology, when designing in a CMOS technology, designers do not have the luxury to apply high voltage on the devices to obtain high output power. Moreover, the transit frequency of the active devices in a CMOS technology is also relatively lower, limiting the maximum operating frequency. But with the rapid scaling down of processes to the era of 90 nm, researchers have started to report highly integrated 77 GHz radar transceivers, e.g. in [10–12], proving it is a feasible solution. Yet, the radar system design in CMOS has become increasingly complicated with the continuously shrinking technology and the challenges it brings [13], e.g. the supply voltage headroom is becoming much smaller, but the threshold voltage remains unscaled. In addition, in a nano-scale technology, the process, voltage and temperature (PVT) variations are more severe and has much more impact on the performance. Thus only very recently, companies have started

to release such products [14, 15] in an advanced CMOS technology node. Automotive radar design in an advanced CMOS technology hence remains till today a very hot topic both in academia and industry.

In an automotive frequency-modulated continuous-wave (FMCW) radar transceiver, using a phase-locked loop (PLL) to generate the modulated chirp signal whose frequency increases linearly with time, is a common solution to achieve a good linearity. The traditional analog phase-locked loop (PLL), however, has the disadvantage of a larger area occupation due to the analog loop filter constructed by passive devices. Moreover, the loop bandwidth is not adjustable in an analog PLL, making it less flexible to support various functions.

With the continuous down-scaling of the CMOS technology, an all-digital phase-locked loop (ADPLL) is becoming increasingly interesting as it can potentially address the challenges in the conventional analog PLL. Moreover, this type of PLL has better scalability, thus reducing the potential re-design effort. Nevertheless, the strict specifications of automotive radar applications induce harsh requirements on the design of an all-digital phase-locked loop (ADPLL). First, the digitization of the voltage controlled oscillator (VCO), i.e. digitally-controlled oscillator (DCO) in an ADPLL introduces quantization noise, which does not exist in the analog counterpart, which requires a very fine tuning resolution of the digitally-controlled oscillator (DCO). Secondly, at the same time, the tuning range of the DCO must be expansive enough to cover the widening PVT spread inherent in a nano-scale technology and to ensure a large bandwidth for the modulated chirp signal. Furthermore, the shrinking technology, resulting in narrower metal tracks, leads to a decline in the quality factor of passive devices, thereby limiting the phase noise performance of oscillators. These requirements pose design challenges on the implementation of the frequency generation circuits in an ADPLL and call for innovative solutions. The goal of this thesis is thus to explore frequency generation circuit topologies, primarily the DCO and the crystal oscillator, to push the performance limits further.

#### 1.1 Research Contribution

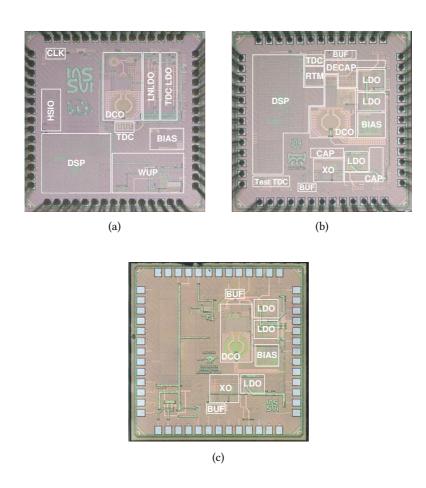

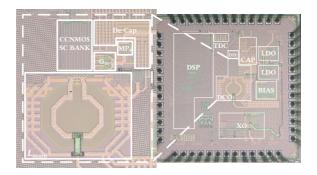

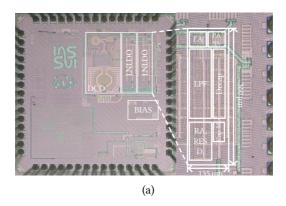

Throughout the work of this thesis, the author proposed several design innovations in the frequency generation circuits with the potential to enhance the overall performance of the ADPLL. Three prototypes were designed and fabricated in a 28 nm CMOS technology. Fig. 1.2 provides the micrographs of the developed chips. These innovations, validated with silicon measurement results, were also presented by the author in various peer-reviewed papers [16–21].

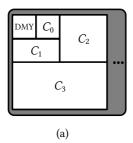

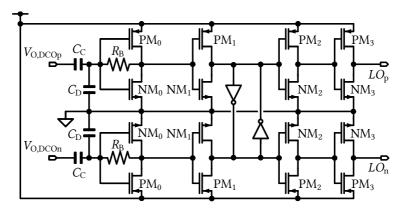

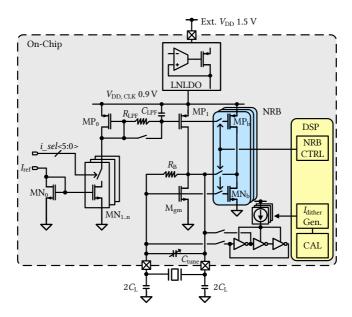

In the initial prototype, identified as project *PANDA* and taped out in November 2020, whose micrograph is shown in Fig. 1.2(a), the author introduced an innovative switchable capacitor (SC) architecture utilizing constantly-conducting NMOS (CCNMOS) to increase the tuning resolution and improve the transient performance of the oscillator [16]. A class-B DCO was implemented using this novel switchable capacitor (SC) architecture, demonstrating excellent phase noise and frequency tuning performance. With a comparable figure-of-merit (FoM) to the state-of-the-art solutions, the proposed DCO exhibits an inherent frequency tuning and very fine resolution, making it particularly advantageous in the application of ADPLL. Moreover, a low-noise low-dropout regulator (LNLDO) was designed by the author to serve as the power supply for the noise-sensitive RF blocks including the DCO and the time-to-digital converter (TDC) [16, 17, 19, 20, 22]. The author also made significant contributions to the implementation of the digital clock and buffer module of this chip.

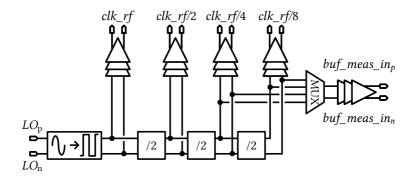

The second chip, designated as project *RedPANDA* and taped out in November 2021, as shown in Fig. 1.2(b), featured a crystal oscillator with fast start-up implemented by the author [18]. The DCO on this chip employed a class-C architecture to reduce the area occupation. Furthermore, the SC bank underwent a redesign, aiming to achieve a higher DCO frequency and wider tuning range [19]. Notably, the author took charge of the physical implementation of the retiming module and the top-level integration of this chip.

The contribution of the author to the third chip, named project *Cheetah*, taped out in July 2023 and depicted in Fig. 1.2(c), encompassed the implementation of bias voltage regulation for the class-C DCO and auxiliary circuitry for better measurability of the crystal oscillator.

#### 1.2 Thesis Organization

Chapter 2 starts with a brief review of the fundamentals of FMCW radar and then moves into the system architecture and the requirements of the FMCW transceiver. Subsequently, the demand on the frequency generation circuits and the design challenges are explained in this chapter.

Figure 1.2: Micrographs of the 28 nm chips relevant to this thesis. (a) Project *PANDA*. (b) Project *RedPANDA*. (c) Project *Cheetah*.

The scope of Chapter 3 covers various design aspects of LC oscillators. This chapter starts with basics of passive devices, followed by the introduction and comparison of different oscillator core structures. Thereafter, switchable capacitor (SC) architectures are discussed in detail, and this chapter also illustrates the design methodology of the SC array. Lastly, two LC oscillators with an innovative SC architecture, fabricated in a 28 nm CMOS technology are presented and the measurement results are compared with the state-of-the-art.

Chapter 4 discusses how the power supply influences the noise performance of the frequency generation circuits. Design and implementation of a low-noise low-dropout regulator (LNLDO) in a 28 nm CMOS technology is then presented and the measurement results demonstrate the necessity to include such a block in the high-demand and noise sensitive application.

Chapter 5 focuses on the design and analysis of crystal oscillators. First, characteristics of quartz crystal and its electrical mode are introduced. Thereafter, structures of crystal oscillators are briefly reviewed. Crystal oscillators featuring two different start-up acceleration schemes are then introduced.

Chapter 6 summarizes the thesis and provides an outlook for future developments.

#### **CHAPTER 2**

## FUNDAMENTALS AND SYSTEM CONSIDERATION OF FREQUENCY GENERATION CIRCUITS

In this chapter, the basics of automotive radar are briefly introduced. Thereafter, we dive deeper into the architectures of 77-81 GHz radar transceivers and explain the system requirements for the frequency generation blocks.

#### 2.1 Fundamentals of FMCW Radar

#### 2.1.1 Distance Measurement

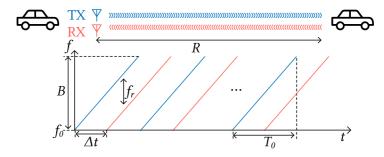

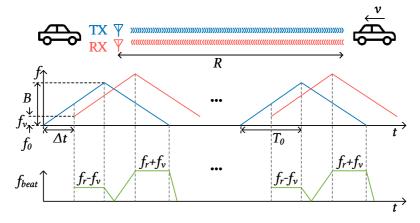

The distance measurement using FMCW radar is carried out by sending modulated electromagnetic chirp signal ,whose frequency increases from  $f_0$  by a bandwidth of B linearly within the signal period  $T_0$ . Fig. 2.1 illustrates the FMCW radar measurement. The chirp signals transmitted from the radar transmitter (TX) are reflected by the vehicle in front and received by the radar receiver (RX).

Figure 2.1: Distance measurement using chirp signal.

As the signal traveled a distance of 2R, a delay  $\Delta t$  is generated by the time

of flight, which can be represented by:

$$\Delta t = \frac{2R}{c_0} \tag{2.1}$$

where  $c_0$  is the speed of light. The frequency difference  $f_r$ , introduced by the distance R, is constant at each measure time point as the chirp signal is linear. In practice,  $f_r$  can be easily derived by mixing the received signal with the transmitted signal. The frequency of this down-converted signal is also called beat frequency  $f_{\text{beat}}$ . In the case of measuring a motionless object,  $f_{\text{beat}}$  equals to  $f_r$ . The distance information is carried by  $f_r$  that can be written as:

$$f_r = \frac{B}{T_0} \Delta t \tag{2.2}$$

The distance *R* can thus be obtained by

$$R = \frac{c_0}{2} \Delta t$$

$$= \frac{c_0}{2} \frac{T_0}{R} f_{\rm r}$$

(2.3)

The maximum measurable range is then

$$R_{\text{max}} = \frac{c_0 T_0 f_{r_{\text{max}}}}{2B} \tag{2.4}$$

where  $f_{r_{max}}$  is limited by the sampling rate of the receiver chain  $f_s$ , and according to Nyquist sampling theorem, the following equation holds:

$$f_{r_{\text{max}}} = \frac{1}{2} f_{\text{s}} \tag{2.5}$$

The range measurement resolution  $R_{\min}$  is determined by the modulation bandwidth B, as in

$$R_{\min} = \frac{c_0}{2B} \tag{2.6}$$

#### 2.1.2 Velocity Measurement

If the measured object is moving, the reflected chirp signal experiences a frequency change due to the *Doppler effect*. Fig. 2.2 depicts the velocity measurement using a chirp FMCW radar, where  $f_{\rm v}$  is the frequency offset introduced due to Doppler effect. The beat frequency  $f_{\rm beat}$  varies depending

Figure 2.2: Chirp FMCW radar velocity and distance measurement.

on whether the chirped signal is ramping up or down. In the frequency increasing phase, the following equations holds:

$$f_{\text{beat,up}} = f_{\text{r}} - f_{\text{v}} \tag{2.7}$$

and for the frequency decreasing phase:

$$f_{\text{beat,down}} = f_{\text{r}} + f_{\text{v}}$$

(2.8)

The distance R and the velocity v can thus be obtained as [23]:

$$R = \left(\frac{c_0 T_0}{4B}\right) \times \left(\frac{f_{\text{beat,up}} + f_{\text{beat,down}}}{2}\right)$$

$$v = \left(\frac{c_0}{2f_0}\right) \times \left(\frac{f_{\text{beat,up}} - f_{\text{beat,down}}}{2}\right)$$

(2.9)

Despite its simplicity, the traditional slow-chirp FMCW scheme has several disadvantages. First, if the radar needs detect multiple object, it lacks a definitive solution, i.e. some "ghost objects" will be detected by the receiver. Second, both the range shift frequency  $f_{\rm r}$  and the Doppler frequency shift  $f_{\rm v}$  are in a range of kilo-hertz, which is susceptible to flicker noise from the devices. This significantly limits the range detection resolution [23]. As a result, fast-chirp FMCW method, first introduced in [24], has become the preferred solution for most automotive radar applications [25–27].

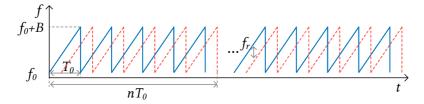

Figure 2.3: Fast chirp FMCW radar waveform.

As shown in Fig. 2.3, fast-chirp FMCW radar utilizes a sawtooth waveform to avoid ambiguity, i.e. the ghost targets problem in traditional chirp radar. The period of the sawtooth signal  $T_0$  is designed to be in a range of several microsecond. From Eq. 2.3,  $f_{\rm r}$  can be written as

$$f_r = \left(\frac{2R}{c_0}\right) \left(\frac{B}{T_0}\right) \tag{2.10}$$

The designed  $T_0$  results in a much larger  $f_r$  in comparison to the Doppler frequency shift  $f_v$ . As a result, the Doppler frequency shift is neglected and the beat frequency  $f_{\rm beat}$  can be purely used for distance measurement. In fact, in a modern fast chirp FMCW system, the distance is measured by performing a fast Fourier transform (FFT) to the down-converted  $f_{\rm beat}$ . The velocity information, however, is embedded in the phase shift of the received signal, which is extracted by a second-dimension FFT. In this way, the velocity and distance measurement can be separated and  $f_r$  is moved away from devices' flicker noise region [23].

#### 2.1.3 Fast-Chirp FMCW Radar Transceiver

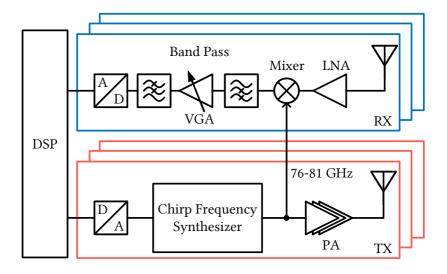

Fig. 2.4 depicts the architecture of a commercial 77-81 GHz radar transceiver [28]. In general, the radar is a multiple-input and multiple-output (MIMO) with transceiver array.

In the transmitter path, a digital-to-analog converter (DAC) and chirp frequency synthesizer or the local oscillator (LO) generate the fast-chirp FMCW signal at around 76-81 GHz as discussed in 2.1. The chirp signal is directly connected to a power amplifier (PA), which amplifies the signal for transmission. On the receiver side, the antenna captures the reflected chirp radio frequency (RF) signal, which is then amplified by a low-noise amplifier (LNA). The intermediate frequency (IF) signal is obtained by the mixing the

Figure 2.4: Architecture of a commercial fast-chirp FMCW radar transceiver [28].

received RF and the local oscillator (LO) signal. The combination of the band-pass filter and variable gain amplifier (VGA) further amplifies the IF signal for the processing of analog-to-digital converter (ADC).

## 2.1.4 Frequency Synthesis with Phase-Locked Loops

One of the most critical components in the FMCW radar transceiver is the frequency synthesizer, as it directly determines the noise level of the chirp signal. Despite the existence of several possibilities for frequency synthesis, the indirect frequency synthesizer using a phase-locked loop (PLL) is the most popular solution due to its superior spectral purity and robustness in comparison to direct synthesizers such as direct digital synthesizer (DDS) [29].

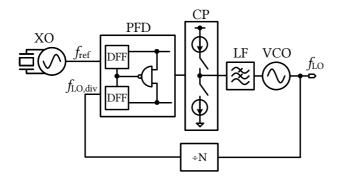

Fig. 2.5 shows the structure of the classic charge-pump based analog PLL. This type of PLL uses a phase frequency detector (PFD) to compare the phase and frequency relationship between the voltage controlled oscillator (VCO) frequency  $f_{\rm LO}$  and the reference frequency  $f_{\rm ref}$ , which is normally derived from a crystal oscillator. The following charge pump translates the signals

from PFD to a signal indicating the phase error between  $f_{\rm LO}$  and  $f_{\rm ref}$ . A low-pass filter, also called loop filter (LF), is incorporated to smooth the repetitive pulses generated by PFD and charge pump (CP) to eliminate the generation of large sidebands in the  $f_{\rm LO}$ . The DC signal after the LF is introduced into a voltage controlled oscillator (VCO), whose output frequency is proportional to the applied voltage. The PLL is a negative feedback system, achieving the phase alignment of the LO clock with the reference clock when locked. This alignment implies equality in the frequencies of the two inputs of the PFD:

$$f_{\text{ref}} = f_{\text{LO,div}}$$

$$= \frac{f_{\text{LO}}}{N}$$

(2.11)

Given that the output frequency of the PLL is N times the reference clock frequency, this configuration is commonly referred to as an integer-N PLL. By programming the divider factor N, the  $f_{LO} = N \times f_{ref}$  can be synthesized.

Figure 2.5: Block diagram of an integer-N analog PLL.

Despite its simplicity, the integer-N PLL exhibits several limitations. First, the frequency of the reference clock is limited by the channel spacing because the integer-N PLL can only generate  $N \times f_{\rm ref}$ . A higher  $f_{\rm ref}$  introduces a large quantization step in the chirp, which could affect the phase noise performance. On the other hand, reducing  $f_{\rm ref}$  restricts the bandwidth of the LF, resulting in a prolonged PLL settling time and substantial footprint of resistor and capacitor in the LF.

These disadvantages can be mitigated by introducing a fractional divider. Fig. 2.6 shows the architecture of a fractional-N PLL, where the fractional divider is implemented by a  $\pm$ N/N+1 divider controlled by a dithered sig-

nal. As long as the frequency of dithered signal considerably surpasses loop bandwidth, the *effective* divide ratio for the PLL becomes an average value between N and N+1. Adjustment of the divide ratio is accomplished by tuning the percentage of time allocated to dividing  $f_{LO}$  by N and N+1. To address the generation of spurs in the output spectrum due to periodic signals, a  $\Sigma\Delta$  modulator is commonly integrated into a fractional-N PLL to introduce randomness to the dither signal, converting the spurs into noise at higher frequency offsets, which is then regulated by the loop.

Figure 2.6: Structure of a fractional-N PLL.

The fractional-N PLL is widely used for the frequency band of 77-81 GHz of the FMCW radar application [4, 11, 30]. However, for a monolithic CMOS technology, despite the  $f_{\rm T}$  of the transistors reaching around 200 GHz in an advanced technology, the quality factor of on-chip passive devices, particularly the inductor, often remains suboptimal due to the skin effect. This deteriorates the phase noise performance of the LC oscillator, typically serving as the VCO in a noise-critical application. Additionally, at such high frequencies, the oscillation period is on the order of tens of picoseconds, making the design of the PFD very challenging. For the optimal phase noise performance of the synthesizer, a good compromise is to select the operating frequency of the VCO to be multi-gigahertz and subsequently multiply the frequency to reach the FMCW radar band, as shown in works such as [31, 32].

Fig. 2.7 shows the architecture of a commercial RF-CMOS fast-chirp frequency synthesizer. This synthesizer employs a fractional-N PLL with a VCO frequency of 8.45-9 GHz. Following the VCO stage in the PLL loop, a frequency tripler is utilized, resulting in a frequency of 25.3-27 GHz. Subsequently, a second frequency tripler is connected after the PLL, converting the frequency to 76-81 GHz. The tripler can be implemented using a mixer,

Figure 2.7: System overview of a commercial RF-CMOS fast-chirp frequency synthesizer [33].

Figure 2.8: Architecture of a self-mixed frequency tripler [34].

as illustrated in Fig. 2.8. In this configuration, the VCO output frequency is mixed with its common-mode voltage, which represents the second harmonic. The output of the mixer contains first and third harmonic components. A band-pass filter is then used to isolate the tripled frequency [34, 35]. Alternative architectures include a frequency selection scheme for the broad-band operation [36], or directly extract the third harmonic from the VCO using a transformer [37–39].

## 2.2 All-Digital Phase-Locked Loops

Despite the analog PLL's ability to provide good performance and its popularity, it cannot fully exploit the benefits of continuously down-scaling CMOS technology due to the bulky LF. For example, in a typical analog chirp PLL, the LF is implemented using an RC low-pass filter. The resistor in this filter significantly contributes thermal noise to the overall phase noise of the PLL, limiting the value of the resistor. Consequently, the capacitors in the LF need to be very large, typically in the nano-farad range, which is very costly to implement in deep sub-micron technology. Moreover, the shrinking technologies lead to a reduced supply voltage, making it more difficult to design an analog charge pump, which dominates the in-band phase noise of the PLL.

Figure 2.9: Functioning principle of the ADPLL.

On the other hand, digital circuits can perform much more complicated functions at a higher speed, making it advantageous to shift the RF system towards a digital-assisted approach in a nano-scale regime. In addition, the digital designs can scale down further with advancing technologies with less

effort, leading to long-term cost reductions.

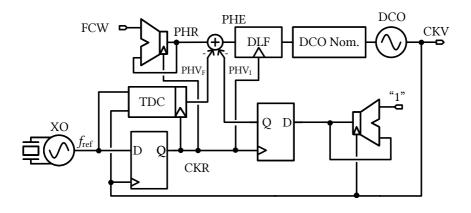

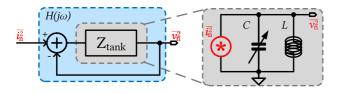

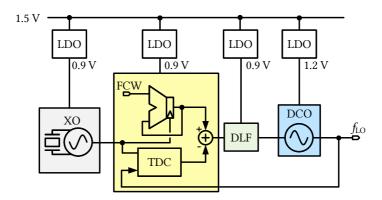

To address these issues and better exploit the advantage of down-scaling CMOS technologies, an all-digital phase-locked loop (ADPLL) is introduced. By processing the phase difference between the reference and high-frequency oscillator in the digital domain, the analog LF can be replaced by a digital LF, implemented using logic gates and registers. Fig. 2.9 depicts the structure and illustrates the principles of an ADPLL. The ADPLL consists of a counter, a time-to-digital converter (TDC), a digital LF, and a digitally-controlled oscillator (DCO). The reference clock is provided by a crystal oscillator.

In the example shown in Fig. 2.9, the ADPLL aims at generating a phase-locked signal with the reference clock, where the frequency is 2.8 times higher. The frequency control word (FCW) is thus set to 2.8. At each rising edge of the reference clock, the counter accumulates the FCW into the reference phase (PHR). Meanwhile, the TDC compares the phase difference between the reference clock and the frequency-variable DCO clock (CKV), generating the variable clock phase (PHV). When the DCO frequency ( $f_{\rm DCO}$ ) equals FCW times the reference frequency ( $f_{\rm ref}$ ), PHV matches PHR. Consequently, the subtractor generates a phase error (PHE) of 0, indicating that the PLL is locked.

If the DCO frequency is lower than FCW times the reference frequency, the cycle number of CKV between two rising edges of the reference clock is smaller than FCW. In this case, PHV is 1.9 for a slower DCO. The subtractor calculates the difference between PHR and PHV, generating a positive PHE. The digital loop filter (DLF) accumulates the PHE and tunes up the frequency of the DCO. Conversely, when the DCO frequency is higher than FCW times the reference frequency, PHV will be larger than PHR, such as 3.6 in this example, resulting in a negative PHE, which eventually tunes down the frequency of the DCO. The feasibility of the utilizing an ADPLL to generate the chirp signal for a FMCW radar has been demonstrated in e.g. [40]. In comparison to the conventional analog counterpart, these ADPLL-based designs offer enhanced flexibility including improved configurability of loop bandwidth and superior linearity.

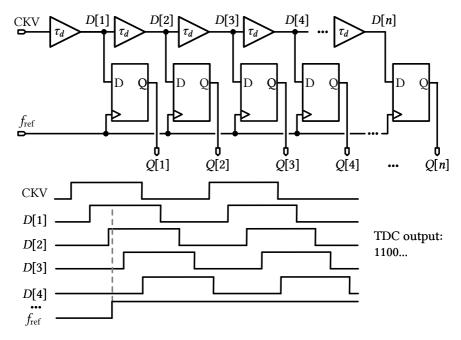

The TDC is a device that converts the time difference between the reference signal and CKV into digital codes. Fig. 2.10 illustrates the schematic of a basic delay-line based TDC and its functioning principle. The TDC consists of a chain of delay buffers with the CKV as the input. D-flip-flops are connected to the output of each buffer and sample the state of the outputs with the reference clock. Apparently, the resolution of the TDC is determined by the delay of the buffer for this basic delay-line based TDC. In order to further

increase the resolution, a 2-D structure, i.e. a Vernier TDC is implemented for the ADPLL of this work [22]. The complete schematic of the ADPLL<sup>1</sup> related to this dissertation is demonstrated in Fig. 2.11 [41].

Figure 2.10: Schematic and functioning principle of the TDC.

## 2.3 Noise

A major performance metric of any RF systems is its noise performance. The signal-to-noise ratio (SNR) is often used to describe the quality of the signal. Due to the random nature of noise, its analysis commonly involves modeling using power spectral density (PSD).

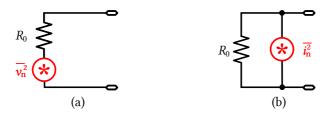

In Fig. 2.12, the thermal noise model of a resistor is depicted. For a resistor with a value of  $R_0$  and at an ambient temperature of T, the noise can be

<sup>&</sup>lt;sup>1</sup>The system and digital design of the ADPLL was first undertaken by Jonas Meier and the design of the TDC was conducted by Tim Lauber. The author's contribution encompassed the design of XO, DCO and LDO as well as the physical implementation of the retiming circuitry.

Figure 2.11: Block diagram of the ADPLL implemented in this thesis work.

represented by a voltage source, as shown in Fig. 2.12(a), with the PSD given by

$$\overline{v_n^2} = 4k_{\rm B}TR_0 \tag{2.12}$$

Alternatively, the noise of a resistor can be modeled by a parallel-connected current source, as illustrated in Fig. 2.12(b). The PSD of the current source is expressed as

$$\overline{i_n^2} = \frac{4k_{\rm B}T}{R_0} \tag{2.13}$$

Figure 2.12: Resistor thermal noise modeled by (a) voltage source and (b) current source.

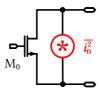

For a MOSFET in saturation, the channel exhibits the characteristic of a resistor, which also generates thermal noise [42]. The noise can be approximately modeled by a current source connected in parallel with the MOSFET

as shown in Fig. 2.13. The PSD of this current source is expressed by

$$\overline{i_n^2} = 4k_{\rm B}T\gamma g_{\rm m} \tag{2.14}$$

Here,  $\gamma$  represents the noise coefficient of the MOSFET, a parameter influenced by the process and channel length of the transistor, while  $g_m$  denotes the transconductance of the MOSFET in saturation. Determining the specific value of  $\gamma$  often requires experimental measurement [43]. For a long-channel device,  $\gamma$  is typically 2/3 [44, 45], with this value increasing as the channel length decreases. As an example, in a 40 nm CMOS technology, the value is 1 for a MOSFET with the minimum channel length [42].

Figure 2.13: Thermal noise model of a MOSFET.

Another type of noise that is generated in MOSFET is the flicker noise. In contrast to thermal noise that is constant over the frequency or *white*, flicker noise exhibits frequency dependence. As the flicker noise's PSD is inversely proportional to frequency, it is also called 1/f noise or *pink* noise. The exact mechanism underlying flicker noise generation remains incompletely understood. A widely accepted hypothesis attributes this noise to the random fluctuations of electrons or holes in the channel [46], known as carrier number fluctuation (CNF). These fluctuations arise due to imperfections in the Si-SiO<sub>2</sub> lattice, causing random trapping and releasing of electrons or holes near the Si-SiO<sub>2</sub> interface in the MOSFET. Additionally, changes in charge within the channel can lead to variations in carrier mobility, a phenomenon known as carrier mobility fluctuation (CMF), which also contributes to noise and becomes more significant as technologies scale down [47]. The flicker can be modeled by a voltage source in series with the gate of the MOSFET, whose PSD is written as

$$\overline{v_n^2} = \frac{K}{WLC_{\text{ox}}} \frac{1}{f} \tag{2.15}$$

where K denotes a process-dependent constant,  $C_{\rm ox}$  represents the capacitance per unit area of the gate oxide, and W and L are the width and length of the transistor, respectively. In CMOS technologies, PMOS transistors in general exhibit a smaller K than compared to NMOS transistors. The reason is that

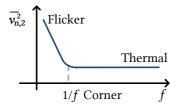

holes generated in a p-type channel are typically further away from the Si-SiO $_2$  interface than electrons in an n-type channel [44]. As indicated in Eq. 2.15, increasing the area of the MOSFET proves to be an effective approach to reduce the transistor's flicker noise. The combination of thermal and flicker noise results in the noise profile depicted in Fig. 2.14. A corner frequency in the PSD of MOSFET noise indicates the frequency range where flicker noise predominates the overall noise characteristics of the MOSFET. In advanced CMOS technologies, this corner frequency is typically in the tens to hundreds of megahertz range [44]. Flicker noise from the MOSFET can be up-converted to the oscillator's carrier frequency, becoming one of the major contributors to noise in oscillators.

Figure 2.14: Noise profile of a MOSFET.

#### 2.4 Phase Noise

An ideal LO output signal can be represented as

$$v_o(t) = V_{\text{peak}} \cdot \cos(2\pi f_0 t) \tag{2.16}$$

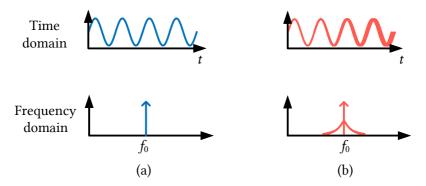

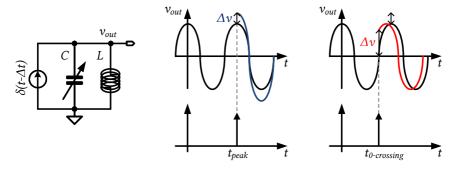

where  $V_{\rm peak}$  is the amplitude of the LO signal and  $f_0$  is the carrier frequency. The waveform and spectrum of an ideal LO is depicted in Fig. 2.15(a), where a single pulse at  $f_0$  is present. However, due to the noise from the devices, the instantaneous phase of the LO is affected, as illustrated in the waveform of Fig. 2.15 (b). The non-ideal LO output can thus be expressed by:

$$v_o(t) = V_{\text{peak}} \cdot \cos(2\pi f_0 t + \phi_n(t))$$

(2.17)

where  $\phi_n(t)$  is the denoted as *phase noise*. Fig .2.15 (b) also shows the spectrum of a noisy LO, where the frequency demonstrates a random fluctuation around  $f_0$ . The phase noise of the LO is normally quantified by integrating the power of 1 Hz bandwidth at a frequency  $\Delta f$ , departed from the carrier  $f_0$ . This value

is then normalized to the carrier power, resulting in a unit of dB referred to the carrier per hertz, or dBc/Hz as abbreviation.

Figure 2.15: Waveform and spectrum of an (a) ideal and (b) realistic LO.

At the transmitter side, phase noise degrades signal quality, which can be quantified by error vector magnitude (EVM). The EVM can be approximately given by:

EVM

$$\approx \sqrt{10^{IQ} + 10^{LOFT} + 10^{PN}}$$

(2.18)

where IQ represents I/Q mismatch, LOFT is LO feed-through, and PN denotes phase noise of the LO [42].

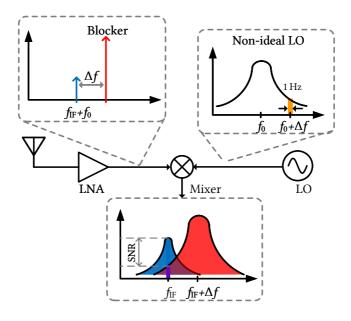

At the receiver side, phase noise significantly affects performance through reciprocal mixing, as illustrated in Fig. 2.16. This effect of reciprocal mixing occurs when a strong blocker exists in an adjacent channel, and due to the LO's phase noise, the blocker is down-converted into the signal band, degrading the SNR. The LO's phase noise requirement for the receiver is expressed as:

$$\mathcal{L}(\Delta f) = P_{\text{sig}}|_{\text{dB}} - SNR - P_{\text{B}}|_{\text{dB}} - 20\log(BW) \tag{2.19}$$

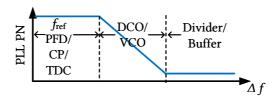

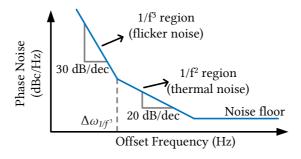

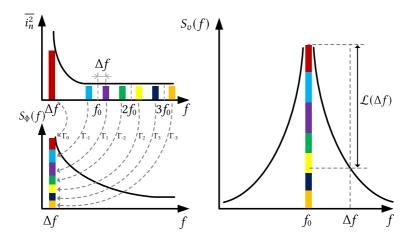

Thus, the phase noise of the LO is critical to the overall performance of RF systems. For a typical LO implemented by a PLL, the phase noise profile is shown in Figure 2.17. It has a skirt-like shape with three distinct regions. For offset frequencies lower than the loop bandwidth, the profile is flat, mainly determined by the noise of the reference frequency and PLL loop control units, such as the PFD and CP in an analog PLL, or the TDC in an ADPLL.

Figure 2.16: Influence of LO phase noise: reciprocal mixing.

Beyond this region, the profile exhibits a slope where the noise decreases by approximately 20 dB/dec. In advanced technologies with a higher flicker noise corner, a region with a slope decreasing by 30 dB/dec may also be observed. In this region, noise performance is primarily determined by the VCO or DCO. In the far-out region from the carrier frequency, the noise floor is set by the divider and buffer in the signal chain. Hence, optimizing the noise performance of frequency generation circuits, such as the crystal oscillator and DCO, is crucial.

Figure 2.17: Noise profile of a PLL.

## **CHAPTER 3**

# LOW-NOISE DIGITALLY CONTROLLED LC OSCILLATORS

The strict performance requirements of the frequency synthesizer in a modern FMCW radar transceiver pose harsh challenges on design of low-noise oscillators. Among various oscillator architectures, LC oscillator have become the *sole* option of radio-frequency integrated circuit (RFIC) designers in many applications because it can achieve a much lower phase noise than other structures such as a ring oscillator, due to the higher frequency selectivity of an LC resonator. In addition, an LC oscillator can operate at a much higher frequency in comparison to e.g. a crystal oscillator, whose frequency is limited by the quartz resonate frequency.

However, LC oscillator also has its drawbacks. First, the integrated inductor occupies a very large area and thus increases the chip fabrication cost. Second, the magnetic coupling and radiation due to the inductor could decreases the noise performance [48] and hence special care has to be taken in isolation and decoupling. In addition, the integrated coil experiences a poorer quality compared to its off-chip counterpart due to the limited metal track width, especially in a nano-scale technology. As a result, LC oscillator designers must study the topologies of LC oscillators intensively to achieve a better phase noise performance [44].

With the trend into digital assisted RF circuits or all-digital RF circuits, such as all-digital phase-locked loop (ADPLL) thanks to the continuous scaling down of CMOS technology, a high-performance digitally-controlled oscillator (DCO) has become of more interest than ever. However, as the DCO utilize a fully discrete frequency tuning, it suffers from more quantization noise than its analog counterpart, i.e. a voltage controlled oscillator (VCO). An intuitive method to mitigate this is to increase the DCO tuning resolution, i.e. minimize the frequency tuning step. In the same time, the large tuning range of a DCO is also preferred due to the requirement on the wider bandwidth of fast chirp signal FMCW to increase the distance measurement resolution, as discussed in 2.1.1. Moreover, the transient behavior of a DCO can greatly

influence the lock time of a ADPLL. These requirements call for innovations in design of DCO.

Because of its the importance and design challenges, this chapter is devoted to study the different aspects and give practical design considerations on digitally controlled LC oscillators in an advanced CMOS technology. Two design examples with measurement results are also demonstrated.

#### 3.1 Passive Devices

The integration of passive devices, e.g. inductor and transformer, is one of the main contributors to the success of modern RF integrated circuits, especially in CMOS technologies. For example, an RF amplifier can achieve a much higher gain at center frequency when using an inductive load stage without spending the supply voltage overhead, which is already very small in an ultra-scaled-down technology.

Despite the fact that on-chip passive devices exhibit worse characteristics than the off-chip ones, e.g. smaller quality factor of an inductor that could lead to a poorer phase noise of an LC oscillator, integrated passive devices have many advantages. First, to use an off-chip passive device, designers must take the parasitic inductance introduced by the long bond wire into consideration. A typical inductance value of a bond wire is in range of 1-2 nH, which is obviously too large for a RF circuit for radar applications that operate in giga-hertz. Second, it is difficult to achieve fully symmetrical structure due to the insufficient control on the bond wire inductance value. Last, the bond wires could have a very strong coupling with other part of the system, degrading the noise performance of the circuit of interest [44].

As integrated passive devices have a very large influence on the performance of LC oscillators, this section discuss the practical considerations on the basics, design and selection of these devices.

#### 3.1.1 Inductor

Monolithic integrated inductors are commonly implemented by metal spiral coils. For the purpose of a high quality factor, the design of inductors typically use top thick metal due to its smaller resistivity. Fig. 3.1 illustrates the 3-D layout of a 1-turn O-shape spiral coil implemented using top thick metals.

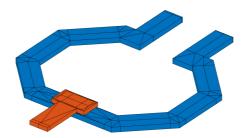

Figure 3.1: 3D illustration of an integrated differential center-tapped O-shape inductor.

Author in [49] gave a mathematical model that can be used to estimate the inductance of an on-chip spiral

$$L \approx 1.37 \times 10^{-7} \times \frac{l_{\text{tot}}^{5/4}}{\left(\frac{l_{\text{tot}}}{4N} + W + (N-1)(W+S)\right)^{1/3} W^{0.083}(W+S)^{0.25}}$$

(3.1)

where  $l_{\text{tot}}$  is the total length of the metal trace, N stands for the number of turns, W is the metal trace width and S is the spacing between trances. Fig. 3.2(a) gives a simple model for the integrated inductor. The series resistance is calculated by

$$R_{\rm s} = R_{\rm \square} \frac{l_{\rm tot}}{W} \tag{3.2}$$

where  $R_{\square}$  is the square resistance of the used metal and determined by the technology. The quality factor of the inductor can thus be expressed by

$$Q = \frac{\omega_0 L}{R_s} \tag{3.3}$$

The accuracy of the model presented in Eq. 3.1 for inductor characterization is reported to have an error ranging from 10% to 20% according to several references [48–50]. To improve upon this, researchers have explored more advanced inductor modeling techniques as documented in [50–53]. Nevertheless, during practical design processes, it is often necessary to employ specific electromagnetic solvers to accurately characterize integrated spiral inductors. In this thesis, the EMX from Cadence has been chosen for this purpose. Fig. 3.2(b) illustrates a more sophisticated lumped model obtained

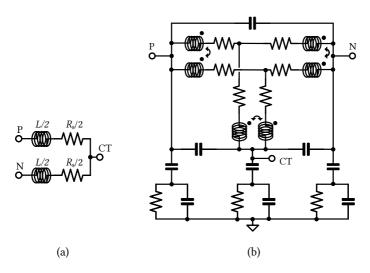

Figure 3.2: Model of a center-tapped inductor. (a) Simple model with series resistors. (b) Lumped model generated by Cadence EMX.

through EMX for a differential center-tapped coil, reflecting the enhanced accuracy achieved through this approach.

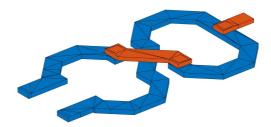

In modern transceivers, such as the FMCW radar transceiver depicted in Fig 2.4, it is often desirable to minimize the magnetic coupling between the LC oscillator and other circuits in order to mitigate the pulling effect, particularly from the strong PA. Although the PA operates at a much higher frequency than the oscillator, as shown in Fig. 2.7, the presence of strong harmonics can still negatively impact the performance of both the PA and the oscillator. To address this issue, a simple yet effective solution is to employ an 8-shaped coil, as illustrated in Fig. 3.3. The concept behind the 8-shaped coil is to utilize two symmetrical spirals in the inductor, which results in the cancellation of electromagnetic emissions. This configuration helps to reduce the unwanted magnetic coupling between the LC oscillator and other circuits.

However, when comparing the 8-shaped inductor to its O-shaped counterpart, it is observed that the 8-shaped inductor generally exhibits a relatively lower Q. This decrease in Q is a trade-off for achieving better isolation and reduced magnetic coupling between the LC oscillator and other circuits. In a study conducted by authors in [54], it was reported that the 8-shaped inductor had approximately 30% lower quality factor compared to the O-shaped induc-

Figure 3.3: Layout of an 8-shape inductor.

tor. However, it is worth noting that in the 90 nm technology used in their research, the achieved Q value was still sufficiently large to not significantly limit the performance of the LC oscillator.

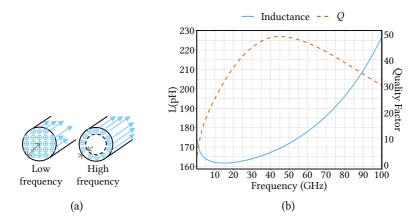

Figure 3.4: Illustration of (a) current distribution due to skin effect and (b) simulated O-shape coil inductance and quality across frequency in room temperature in a 28 nm CMOS using EMX.

Another important aspect that designers need to account for is the impact of operating frequency on both inductance and quality factor. At very high frequencies, the phenomenon known as the *skin effect* becomes significant. The skin effect refers to the concentration of current towards the surface of the conductor when carrying high-frequency AC current, as depicted in Fig. 3.4(a). This occurrence leads to an effective increase in resistance, resulting in a lower quality factor for the inductor. To illustrate this effect, Fig. 3.4(b) presents the results of EM simulations showing the quality factor and

inductance of an O-shaped integrated inductor implemented using a 28 nm CMOS process at room temperature. The plot demonstrates that beyond a frequency of approximately 45 GHz, the quality factor of the inductor starts to decrease. This behavior is contrary to the linear dependence of the Q on the  $\omega_0$  as predicted by Eq. 3.3. This result further emphasizes the necessity of not having the LC oscillator operate at a very high frequency such as the radar band of 77 GHz, as discussed in 2.1.4, for optimal LC tank quality factor, which significantly impacts the phase noise performance.

An integrated inductor can also be used as a variable element to tune the frequency of an LC oscillator, e.g. in [55]. However, a variable inductor is normally associated with special fabrication technology such as microelectro-mechanical systems (MEMS). As a result, the use of variable inductors is beyond the scope of this thesis.

#### 3.1.2 Capacitor

The capacitor is a crucial component, fulfilling various essential functions in RFICs. Firstly, capacitors play an important role in adjusting the resonance of the LC circuit, enabling the oscillator's frequency tuning. Secondly, capacitors serve as efficient AC couplers, facilitating the interconnection of different RF blocks. Lastly, they can function as the decoupling capacitance between significant nets and ground [44].

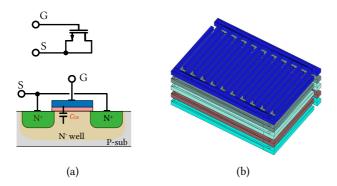

Figure 3.5: (a) Symbol and cross-section of a n-type MOS capacitor. (b) 3-D illustration of a fringe MOM capacitor.

Fig. 3.5 illustrates two commonly utilized capacitor types in CMOS technology. The n-type metal-oxide-semiconductor (MOS) capacitor, shown in

Fig. 3.5(a), consists of an NMOS transistor embedded within a lightly doped N-well. By applying a voltage higher than that of the source to the gate electrode, an electric field is generated, attracting electrons, and establishing a conducting channel beneath the oxide layer, thus forming a capacitor. The MOS capacitor exhibits the advantage of very high density, particularly in nano-scale technologies where the oxide thickness is significantly reduced. However, this capacitor type suffers from certain limitations, such as a relatively small quality factor due to the substantial resistance of the channel. Moreover, achieving large capacitance with MOS capacitors is associated with a considerable oxide area, leading to increased leakage current. These disadvantages make MOS capacitor unsuitable for LC tank or coupler between RF blocks. Nevertheless, these capacitors can serve effectively as decoupling capacitance for the power supply rail.

The fringe metal-oxide-metal (MOM) capacitor, as depicted in Fig. 3.5(b), typically consists of narrow metal lines with small gaps. This design aims to maximize the capacitance density by utilizing the available area efficiently. Similar to a metal-insulator-metal (MIM) capacitor, it employs metal layers as capacitor plates, with an oxide layer serving as the dielectric. However, unlike MIM capacitor, the fringe MOM capacitor does not require specialized fabrication technology, making it a more affordable and generally available option. The primary advantage of fringe MOM capacitors is their relatively high quality factor due to the low resistance of the metal traces compared to that of the channel. However, as all the metal traces are utilized to increase the capacitance, they obstruct routing possibilities for the entire area they occupy.

## 3.2 Phase Noise in LC Oscillator

## 3.2.1 Theoretical Analysis of Phase Noise - LTI Approach

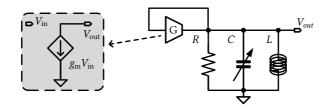

The phase noise of an LC oscillator can be analyzed by a linear time-invariant (LTI) approach [56]. The transfer function of an LC oscillator under the assumption that the negative resistance introduced by the  $g_{\rm m}$  stage cancels out the tank resistance R can be straightforward derived by

$$|H(j\omega)|^2 = \left| \frac{\omega L}{1 - \omega^2 LC} \right| \tag{3.4}$$

as also shown in Fig. 3.7.

Figure 3.6: General model of an LC oscillator.

Figure 3.7: Transfer function of an LC oscillator for the noise current.

At the frequency of  $\omega_0 \pm \Delta \omega$ , where  $\Delta \omega \ll \omega_0$ , the expression of noise transfer function holds

$$|H(j(\omega_0 + \Delta\omega))|^2 \approx \left| \frac{1}{2\Delta\omega C} \right|^2$$