# Neuro-inspired Hardware Acceleration for Efficient Biomedical Signal Processing in Mobile Sensing Devices

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen

Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der

Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

Johnson Loh, M.Sc.

aus Aachen, Deutschland

Berichter: Univ.-Prof. Dr.-Ing. Tobias Gemmeke

Univ.-Prof. Dr.-Ing. Anke Schmeink

Tag der mündlichen Prüfung: 20.03.2025

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

## **Abstract**

The processing of biomedical signals in mobile sensing devices enables the continuous monitoring of health parameters for early detection of threatening arrhythmia in the population through convenient wearable devices, such as smartwatches. The design of processing modules, which are feasible in this resource-constrained environment, is subject to multiple constraints for their deployment in-field. High quality classification is desired for accurate detection to trigger treatment by trained personnel. Robust classification beyond available training data is necessary to generalize system feasibility across the general population. Low-power operation is necessary for long-term screening for sparse features indicating abnormal health conditions. The co-optimization of neuro-inspired algorithms on dedicated hardware shows the promise to address all desired specifications in an application-specific device.

This work explores neuro-inspired concepts for low-power digital processing of biomedical signals. Artificial neural networks has shown superior classification capabilities in the machine learning domain. Using an artifical neural network as a baseline, a systematic design space exploration methodology is applied to design an ECG classifier and co-optimize the system from the algorithm level down to a hardware design for ultra-low power consumption and high classification quality. Then, the system is extended with a domain generalization method for robust classification across multiple datasets. The method is designed for direct integration into a pre-trained neural network with low overhead regarding inference and training. At last, the temporal coding of information in spikes is adopted from the human brain as a data processing mechanism for low power processing. The investigated temporal coding method shows equivalent numerical values after processing with reduced operations compared to conventional fixed-point arithmetic. In the end, the neuro-inspired concepts show promising directions to improve specialized ANN hardware accelerators for biomedical signal processing both for low-power processing and robust high-quality classification.

# Acknowledgements

First, I would like to thank my advisor Prof. Tobias Gemmeke for the opportunity to get an insight into academic research and all its diverse components.

Then, I am grateful for the thesis jury for their time and comments to critically review this work and discuss its contents.

During my PhD journey, I could always count on the support of my family and friends, without whom this journey would not have been possible. In particular, I would like to thank my mother for being my constant motivator through my professional career, and my sister for giving me the help and support in critical times of need.

# **Contents**

| Αl | bstrac | :t       |                                                                          | iii   |

|----|--------|----------|--------------------------------------------------------------------------|-------|

| A  | cknow  | vledgen  | nents                                                                    | v     |

| Αι | ıthor' | 's Publi | cation List                                                              | xxiii |

| 1  | Intr   | oductio  | on.                                                                      | 1     |

|    | 1.1    | Thesis   | Contributions                                                            | 3     |

| 2  | Prer   | equisit  | es for Efficient Real-Time Processing of Low Data Rate Streams           | 5     |

|    | 2.1    | Applic   | cation Context of ECG Monitoring                                         | 6     |

|    |        | 2.1.1    | Cardiac Electrophysiology                                                | 6     |

|    |        | 2.1.2    | Mobile ECG Monitoring                                                    | 7     |

|    |        | 2.1.3    | Application Scope of This Work                                           | 8     |

|    | 2.2    | Pre-pr   | ocessing on the Edge with ANNs                                           | 8     |

|    |        | 2.2.1    | State-of-the-art ECG Classification Using ANNs                           | 8     |

|    |        | 2.2.2    | State-of-the-art Digital Processing of ECG Classifiers                   | 10    |

|    |        | 2.2.3    | Cascaded Classification of ANN classifiers                               | 14    |

|    |        | 2.2.4    | System Scope of This Work                                                | 15    |

|    | 2.3    | Design   | n and Evaluation Strategy                                                | 17    |

|    |        | 2.3.1    | State-of-the-Art of Energy Estimation of Batched ANN Workloads           | 17    |

|    |        | 2.3.2    | Exploration of Dataflow Sequences for Convolution Operations             | 19    |

|    |        | 2.3.3    | Design Space Exploration Methodology for Stream Processing Architectures | 27    |

|    | 2.4    | Summ     | nary                                                                     | 33    |

| 3  | Co-C   | Optimiz  | zation of an ANN Accelerator for ECG Monitoring                          | 35    |

|    | 3.1    | Algori   | ithm Design                                                              | 35    |

|    |        | 3.1.1    | Discrete Wavelet Transform for Feature Extraction                        | 37    |

|   |     | 3.1.2   | Subsampling-based Classification of Temporal Sequences using TCNs   | 37 |

|---|-----|---------|---------------------------------------------------------------------|----|

|   |     | 3.1.3   | Algorithm Fitting                                                   | 41 |

|   | 3.2 | Hardw   | vare Design                                                         | 41 |

|   |     | 3.2.1   | Hardware Mapping                                                    | 42 |

|   |     | 3.2.2   | Digital Implementation                                              | 48 |

|   |     | 3.2.3   | Design Evaluation                                                   | 53 |

|   | 3.3 | Summ    | ary                                                                 | 56 |

| 4 | Har | dware-  | Aware Domain Generalization for ANN-Based Feature Alignment         | 59 |

|   | 4.1 | Applic  | cation Context of Domain Generalization                             | 60 |

|   | 4.2 | State-o | of-the-art Domain Generalization for ECG Classification             | 61 |

|   | 4.3 | Low C   | Complexity DG Algorithms                                            | 62 |

|   |     | 4.3.1   | Complexity Exploration in State-of-the-Art DG Methods               | 63 |

|   |     | 4.3.2   | Correction Layer (CL)                                               | 65 |

|   | 4.4 | Evalua  | ation of Correction Layer Performance                               | 66 |

|   |     | 4.4.1   | CL Classification Performance                                       | 66 |

|   |     | 4.4.2   | CL Integration into an ECG Inference Engine                         | 68 |

|   |     | 4.4.3   | CL Evaluation for Backpropagation On-Chip                           | 69 |

|   | 4.5 | Summ    | ary                                                                 | 71 |

| 5 | Tem | poral C | Coding for Numerically-Equivalent Conversion of ANNs to SNNs        | 73 |

|   | 5.1 | Applic  | cation Context of SNN Algorithm and Hardware Design                 | 73 |

|   | 5.2 | State-o | of-the-art ANN-SNN Conversion                                       | 76 |

|   | 5.3 | Lossle  | ss Temporal Coding for Fixed-Point Numbers                          | 77 |

|   | 5.4 | Algori  | thm Design of a Temporally Encoded ECG Classifier                   | 82 |

|   |     | 5.4.1   | Activation Normalization of the Reference Classifier                | 82 |

|   |     | 5.4.2   | Distribution of Spike Timings After Normalization                   | 84 |

|   |     | 5.4.3   | Toggle Activity of the Membrane Potential                           | 86 |

|   |     | 5.4.4   | Impact of Temporal Resolution on Latency and Classification Quality | 90 |

|   | 5.5 | Hardw   | vare Design of a Temporally Encoded ECG Classifier                  | 91 |

|   |     | 5.5.1   | System-level Hardware Mapping                                       | 91 |

|   |     | 5.5.2   | Temporal Encoding Logic for Activations                             | 92 |

|   |     | 553     | Temporal Decoding Logic in PE Unit                                  | 93 |

| Bi | Bibliography 10 |         |                   |  |  |  |  | 101 |  |      |  |  |  |  |  |  |    |

|----|-----------------|---------|-------------------|--|--|--|--|-----|--|------|--|--|--|--|--|--|----|

| 6  | Con             | clusion |                   |  |  |  |  |     |  |      |  |  |  |  |  |  | 97 |

|    | 5.6             | Summ    | ary               |  |  |  |  |     |  |      |  |  |  |  |  |  | 95 |

|    |                 | 5.5.4   | Design Evaluation |  |  |  |  |     |  | <br> |  |  |  |  |  |  | 94 |

|    |                 |         |                   |  |  |  |  |     |  |      |  |  |  |  |  |  | ix |

# **List of Figures**

| 2.1  | Overview of cardiac stimuli for the heart and the first three electrocardiogram (ECG)          |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | leads and corresponding electrode positions at the extremities adapted from [15]. $$ .         | 6  |

| 2.2  | Example distribution of quality metrics for ECG classifiers derived from references            |    |

|      | in [28]                                                                                        | 9  |

| 2.3  | System overview of ECG classifier with a modified split-learning mechanism from [42].          | 11 |

| 2.4  | Energy and area efficiency for digital computing architectures scaled to 130-nm CMOS           |    |

|      | technology [67]                                                                                | 14 |

| 2.5  | Structure of cascaded classifier for balanced datasets and machine learnings (MLs)             |    |

|      | classifiers, here artificial neural networks (ANNs), with increasing computational             |    |

|      | complexity (CC) [JL2]                                                                          | 15 |

| 2.6  | Hardware accelerator as gating mechanism for post-processing steps                             | 16 |

| 2.7  | Loop nest representation of computational workload of a 2D-convolution operation               |    |

|      | for a batch of input feature maps [76]                                                         | 18 |

| 2.8  | Simplified memory model to estimate data access costs for elementary dataflow schemes          |    |

|      | (adapted from [78]). A cell indicates the processing element (PE) and the data held            |    |

|      | within it until all corresponding partial sums are calculated                                  | 21 |

| 2.9  | Diagram of a memory state for a weight stationary 2D-convolution with a filter kernel          |    |

|      | $3\times3,2$ input/output channels, an output feature map size of $5\times5$ and a convolution |    |

|      | stride 1. The crosses and circles mark data from two separate states. The weight               |    |

|      | marked in bold is held stationary inside the PE memory until all partial sums has              |    |

|      | been calculated for its input.                                                                 | 23 |

| 2.10 | Concept of the genetic algorithm                                                               | 24 |

| 2.11 | Execution sequence of weights in a weight stationary dataflow assuming 1 PE for                |    |

|      | processing.                                                                                    | 25 |

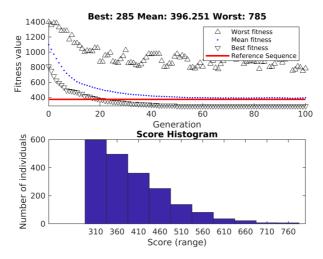

| 2.12 | Best and mean fitness values during generations of genetic algorithm optimization                           |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | (above). Fitness value distribution of final generation (below).                                            | 26 |

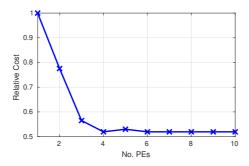

| 2.13 | Sweep across number of parallel PEs for cost optimal sequences in a weight stationary                       |    |

|      | dataflow using genetic algorithm optimization                                                               | 26 |

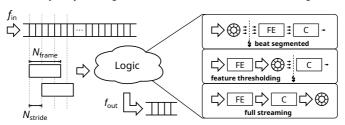

| 2.14 | Design specifications for the continuous ECG monitoring use case [JL7]. The input is                        |    |

|      | sampled continuously and buffered intermediately for processing, where frames are                           |    |

|      | selected for further analysis. Data is either processed using raw frames or extracted                       |    |

|      | features or in a full streaming fashion.                                                                    | 28 |

| 2.15 | test                                                                                                        | 30 |

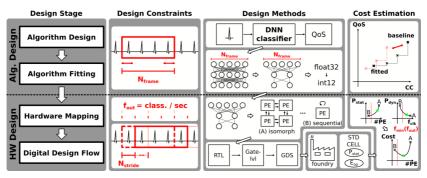

| 2.16 | Top-down design methodology proposed in [JL7]. The design constraints, specific                             |    |

|      | to streaming ECG data, are used to guide both the algorithm and hardware design.                            |    |

|      | Costs, which map to power and quality of service (QoS), are continuously assessed                           |    |

|      | to guarantee the convergence towards a cost-optimal design.                                                 | 31 |

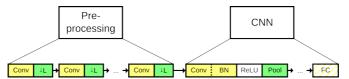

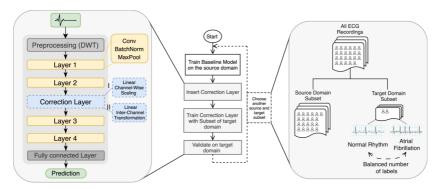

| 3.1  | ECG classifier structure adapted from [JL3]. The yellow blocks are performing con-                          |    |

|      | volution operations and the green blocks perform subsampling operations                                     | 36 |

| 3.2  | Block diagram of wavelet transformation with level 4 decomposition adapted from                             |    |

|      | [JL1]. Lowpass filters $h(n)$ are used in the early levels to generate approximation                        |    |

|      | coefficients $A_x$ from input $x(n)$ for deeper levels. The highpass filters $g(n)$ are only                |    |

|      | used in the final level to generate the detail coefficients $D_x$                                           | 37 |

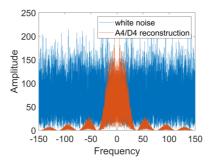

| 3.3  | Frequency spectrum of white noise and reconstruction using only A4/D4 coefficients                          |    |

|      | after discrete wavelet transform (DWT).                                                                     | 38 |

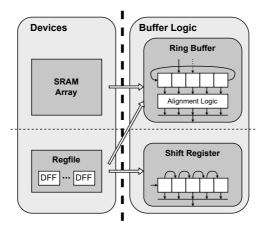

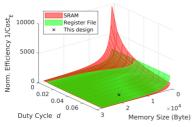

| 3.4  | Memory devices and logic level implementation of activation buffers [JL3]                                   | 43 |

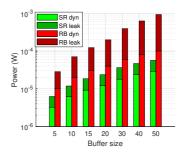

| 3.5  | Cost comparison for memory devices and simulation results for logic level implemen-                         |    |

|      | tations [JL7].                                                                                              | 44 |

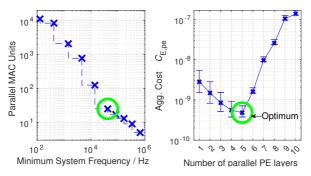

| 3.6  | Pareto-optimal front (left) and aggregated cost (right) for parallelized layers using a                     |    |

|      | DFF as the template cell. Variations of $P_{{ m leak},i}$ and $E_{{ m op},i}$ for rise/fall transitions are |    |

|      | resulting in cost uncertainties [JL3].                                                                      | 47 |

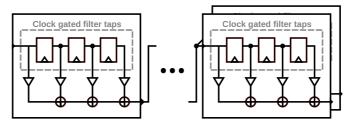

| 3.7  | Flat mapping of cascaded FIR filters DWT pre-processing                                                     | 48 |

| 3.8  | Data rate reduction in flat mapped DWT components and number of cycles for partial                          |    |

|      | temporal convolutional network (TCN) inference over the number of input samples                             |    |

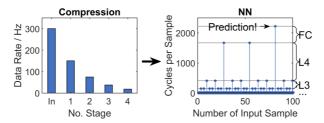

|      | from the DWT layer [JL3]                                                                                    | 49 |

| 3.9  | Data movement in a serial-in parallel-out (SIPO) buffer, which provides self-aligned            |    |

|------|-------------------------------------------------------------------------------------------------|----|

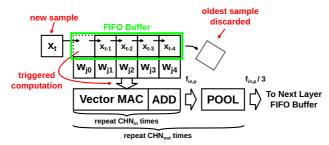

|      | input feature maps for the channel-wise convolution subroutine [JL3]. $\hdots$                  | 49 |

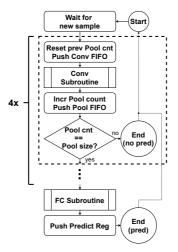

| 3.10 | Flow chart of the data-driven TCN inference [JL3]                                               | 50 |

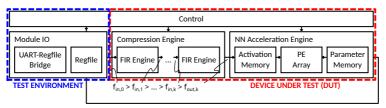

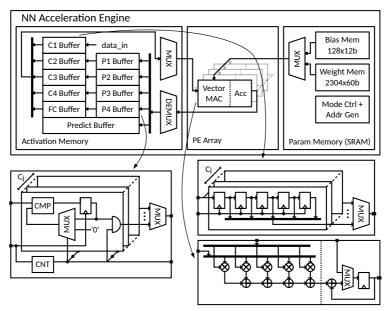

| 3.11 | $System-level\ architecture\ of\ the\ WVCNN\ design\ including\ the\ test\ environment\ [JL3].$ | 51 |

| 3.12 | Block diagram of the neural network acceleration engine in the WVCNN design [JL3].              | 52 |

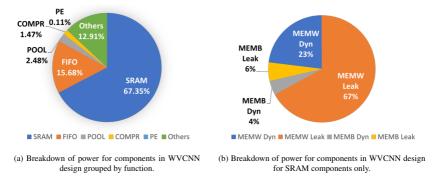

| 3.13 | Power breakdown of WVCNN design based on back annotated post-synthesis netlists                 |    |

|      | [JL3]                                                                                           | 53 |

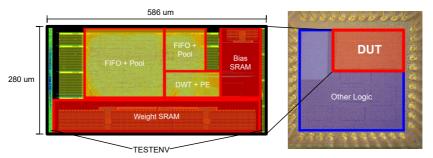

| 3.14 | Layout level view of the WVCNN design and the chip micrograph [JL3]                             | 54 |

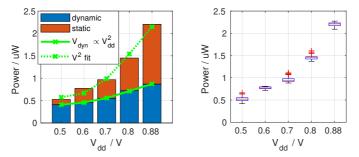

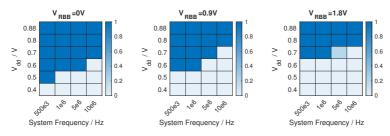

| 3.15 | Measurement results of the fabricated WVCNN design operating at 500 kHz [JL7].                  |    |

|      | The left diagram shows the average power consumption split into static and dynamic              |    |

|      | power and the right diagram shows the distribution of total power over 5 measure-               |    |

|      | ments across multiple dies                                                                      | 55 |

| 3.16 | Shmoo plot for three different levels of reverse body bias [JL3]. $\dots \dots$                 | 56 |

| 4.1  | Summary of the classification problem of data dependent on the availability of data             |    |

|      | during training (Tr) and testing (Te). For the robust classification of ECG data in a           |    |

|      | practical setting the aim is to generalize over out-of-distribution (OOD) data with a           |    |

|      | domain shift between source domain (SD) and target domain (TD) [JL10]                           | 60 |

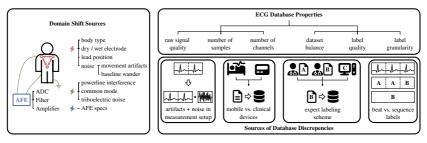

| 4.2  | Summary of domain shift sources in ECG data acquisition. The discrepancy is databases           |    |

|      | does not result only from deviations in the measurement setup, but also the labeling            |    |

|      | scheme [JL10]                                                                                   | 61 |

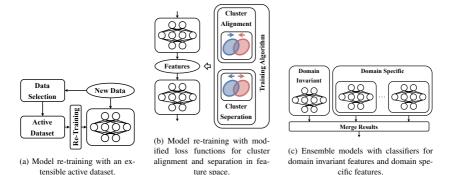

| 4.3  | State-of-the-art domain generalization (DG) methods applied for the classification of           |    |

|      | ECG signals [JL10]                                                                              | 62 |

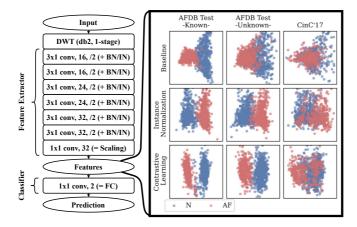

| 4.4  | Fully convolutional neural network for the evaluation of instance normalization and             |    |

|      | contrastive learning. Features before the final dense layer are visualized in the 2D            |    |

|      | plane after principle component analysis [JL10]                                                 | 64 |

| 4.5  | Experimental setup for the insertion of correction layers (CLs) in a deep neural net-           |    |

|      | work (DNN). The training and validation is performed in two distinct steps. First, the          |    |

|      | DNN is trained without the CL on the source domain. Second, the CL is trained on                |    |

|      | a subset of the target domain. Both stages are cross validated for statistically robust         |    |

|      | results [JL10]                                                                                  | 66 |

|      |                                                                                                 |    |

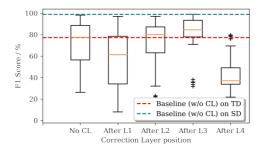

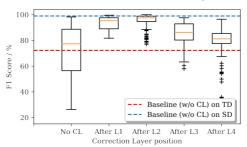

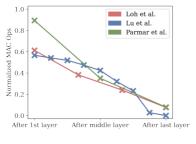

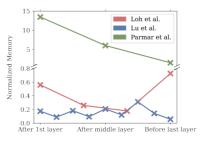

| 4.6 | CL performance based on correction layer position and type. The blue and red dot-        |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | ted lines indicate the average performance on source and target domain without CL        |    |

|     | training, respectively [JL10].                                                           | 67 |

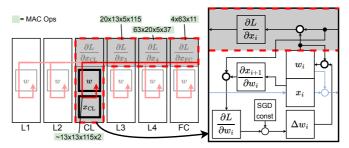

| 4.7 | Theoretical concept of CL training. In contrast to DNN fine-tuning, the training of      |    |

|     | CL only requires partial memory resources (bold solid box) and a fraction of compu-      |    |

|     | tations (grey area in red dashed line) [JL10]                                            | 69 |

| 4.8 | estimated multiply-and-accumulate (MAC) operations and memory necessary for CL           |    |

|     | training based on different DNN architectures and CL position. The costs are normal-     |    |

|     | ized against the reference case, in which the DNN is fine-tuned [JL10]                   | 70 |

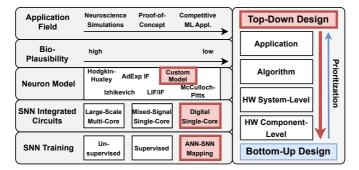

| 5.1 | Simplified overview of SNN design concepts in context of custom neuron model pro-        |    |

|     | posed in [JL4].                                                                          | 74 |

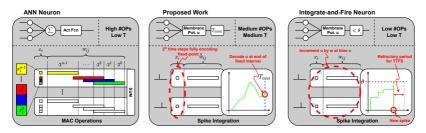

| 5.2 | Concepts of the conventional ANN neuron (left), the IF neuron (right) and the neuron     |    |

|     | model with proposed temporal coding (center) [JL4]                                       | 78 |

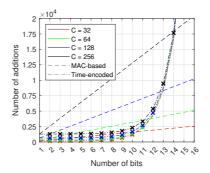

| 5.3 | Number of additions for a 1D-convolution with kernel size $k = 5$ and $C$ input channels |    |

|     | [JL4]                                                                                    | 80 |

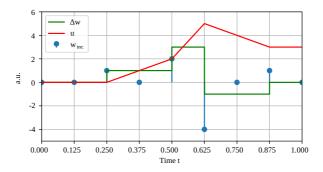

| 5.4 | Example encoding of a scalar product with four elements and normalized time axes         |    |

|     | [JL4]                                                                                    | 81 |

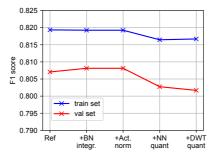

| 5.5 | Ablation study on the normalization steps as preparation for the temporal encoding       |    |

|     | scheme [JL4].                                                                            | 84 |

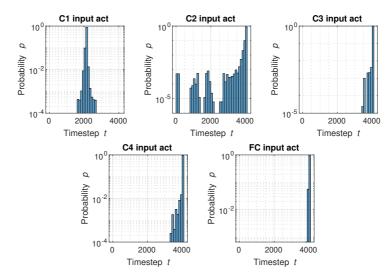

| 5.6 | Histogram of spike timings after normalization for the inference of 86 ECG samples.      |    |

|     | Each ECG sample results in multiple computation sequences per layer and neuron, as       |    |

|     | multiple frames per ECG sample are selected using the sliding window approach            | 85 |

| 5.7 | Probability distribution over time of the activation value in the accumulation register  |    |

|     | of the WVSNN design. A strong color depth indicates a high probability.                  | 86 |

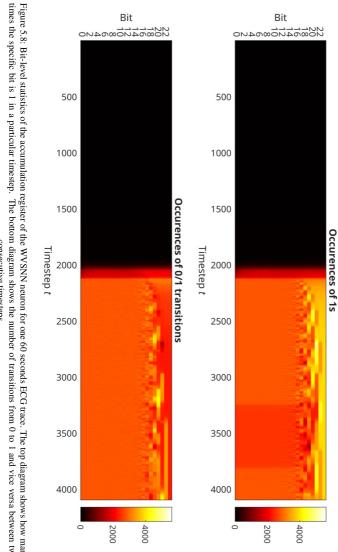

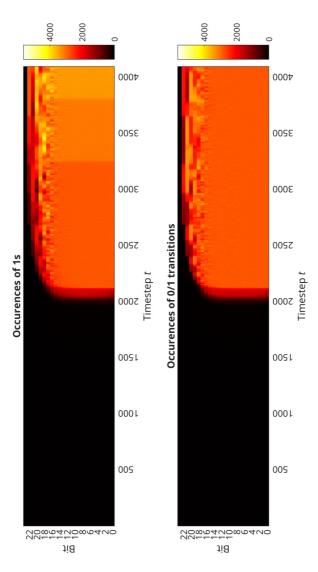

| 5.8 | Bit-level statistics of the accumulation register of the WVSNN neuron for one 60         |    |

|     | seconds ECG trace. The top diagram shows how many times the specific bit is 1 in a       |    |

|     | particular timestep. The bottom diagram shows the number of transitions from 0 to 1 $$   |    |

|     | and vice versa between two consecutive timesteps.                                        | 88 |

| 5.9  | Bit-level statistics of the accumulation register of the WVSNN neuron after L1-norm. |    |

|------|--------------------------------------------------------------------------------------|----|

|      | The top diagram shows how many times the specific bit is 1 in a particular timestep. |    |

|      | The bottom diagram shows the number of transitions from $0$ to $1$ and vice versa    |    |

|      | between two consecutive timesteps.                                                   | 89 |

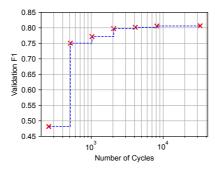

| 5.10 | Pareto-optimal front for SNN quality and the number of cycles required to calculate  |    |

|      | one layer [JL4]                                                                      | 91 |

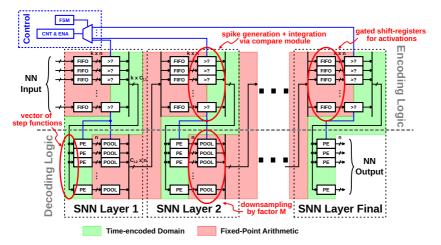

| 5.11 | System-level architecture of the mapped spiking neural network (SNN) accelerator     |    |

|      | [JL4]. The convolution is performed using the time-encoding scheme and can be        |    |

|      | exchanged with conventional PEs with fixed-point MAC units for comparison            | 92 |

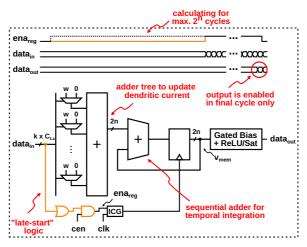

| 5.12 | Block diagram of PE unit for the time-encoded convolution [JL4]. The encoded signal  |    |

|      | is inserted for the sequential decoding within the membrane potential. $\hdots$      | 93 |

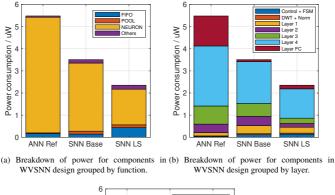

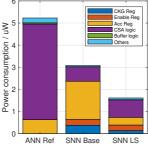

| 5.13 | Power breakdown of the WVSNN design grouped into functional units, layers and        |    |

|      | the components inside the computational neuron units [JL4]                           | 95 |

# **List of Tables**

| 3.1 | TCN structure from [JL3]                                                           | 40 |

|-----|------------------------------------------------------------------------------------|----|

| 4.1 | Validation F1 score of DG techniques on the inter-patient AFDB and CinC'17 dataset |    |

|     | using 5-fold cross-validation                                                      | 64 |

| 4.2 | Post-synthesis results of reference ECG accelerator with and without integrated CL |    |

|     | [JL10]                                                                             | 68 |

## List of Abbreviations

ADC analog-to-digital converter

AF atrial fibrillation

AFE analog front-end

ANN artificial neural network

**ASIC** application specific integrated circuit

BLE Bluetooth Low Energy

CC computational complexity

CL correction layer

CMOS complementary metal-oxide-semiconductor

CNN convolutional neural network

CVD cardiovascular disease

CWT continuous wavelet transform

**DG** domain generalization

**DNN** deep neural network

**DSP** digital signal processing

**DUT** device under test

**DWT** discrete wavelet transform

ECG electrocardiogram

EDA electronic design automation

fdSOI fully-depleted silicon-on-insulator

FIFO first-in first-out

FIR finite impulse response

**FPGA** field programmable gate array

**FSM** finite state machine

GPU graphics processing unit

GRU gated recurrent unit

HDL hardware description language

IF integrate-and-fire

IC integrated circuit

ICG integrated clock gating

ICM implantable cardiac monitoring

**IID** idependent and identically distributed

**IoT** internet of things

**KPI** key performance indicator

LSB least significant bit

LSTM long-short term memory

MAC multiply-and-accumulate

MEMS micro-electromechanical systems

ML machine learning

MLP multi-layer perceptron

OOD out-of-distribution

PCA principle component analysis

PE processing element

PPA power-performance-area

QoS quality of service

RAM random-access memory

ReLU rectified linear unit

RISC reduced instruction set computer

RMSE root mean square error

ROM read-only memory

RTL register-transfer level

SGD stochastic gradient descent

SIMD single instruction multiple data

SIPO serial-in parallel-out

**SNN** spiking neural network

SoC system-on-chip

SRAM static random-access memory

TCN temporal convolutional network

TTFS time-to-first-spike

## **Author's Publication List**

- [JL1] J. Loh, J. Wen, and T. Gemmeke, "Low-cost DNN hardware accelerator for wearable, high-quality cardiac arrythmia detection," in 2020 IEEE 31st International Conference on Application-specific Systems, Architectures and Processors (ASAP), IEEE, Jul. 2020. DOI: 10.1109/asap49362.2020.00042.

- [JL2] C. Latotzke, J. Loh, and T. Gemmeke, "Cascaded classifier for pareto-optimal accuracy-cost trade-off using off-the-shelf ANNs," in *Machine Learning, Optimization, and Data Science*, Springer International Publishing, 2022, pp. 423–435. DOI: 10.1007/978-3-030-95470-3 32.

- [JL3] J. Loh and T. Gemmeke, "Dataflow optimizations in a sub-uW data-driven TCN accelerator for continuous ECG monitoring," in 2022 IEEE Nordic Circuits and Systems Conference (NorCAS), IEEE, Oct. 2022. DOI: 10.1109/norcas57515.2022.9934591.

- [JL4] J. Loh and T. Gemmeke, "Lossless sparse temporal coding for SNN-based classification of time-continuous signals," in 2023 Design, Automation and Test in Europe Conference and Exhibition (DATE), IEEE, Apr. 2023. DOI: 10.23919/date56975.2023.10137112.

- [JL5] C. Lanius, J. Lou, J. Loh, and T. Gemmeke, "Automatic generation of structured macros using standard cells application to CIM," in 2023 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), IEEE, Aug. 2023. DOI: 10.1109/islped58423. 2023.10244608.

- [JL6] Y. Chen, J. Lou, C. Lanius, F. Freye, J. Loh, and T. Gemmeke, "An energy-efficient and area-efficient depthwise separable convolution accelerator with minimal on-chip memory access," in IFIP/IEEE 31st International Conference on Very Large Scale Integration (VLSI-SoC), IEEE, Oct. 2023, DOI: 10.1109/vlsi-soc57769.2023.10321918.

- [JL7] J. Loh and T. Gemmeke, "Stream processing architectures for continuous ecg monitoring using subsampling-based classifiers," *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, pp. 1–11, 2023, ISSN: 1557-9999. DOI: 10.1109/tvlsi.2023.3329360.

- [JL8] A. Ayad, M. Barhoush, J. Loh, T. Gemmeke, and A. Schmeink, "PEACE: Private and energy-efficient algorithm for cardiac evaluation on the edge using modified split learning and model quantization," in 2023 14th International Conference on Information and Communication Systems (ICICS), IEEE, Nov. 2023. DOI: 10.1109/icics60529.2023. 10330472.

- [JL9] M. Lahr, J. Loh, M. Schwarz, M. C. Lemme, and T. Gemmeke, "Vehicle surroundings perception using micro-electromechanical systems inertial sensors," *Advanced Intelligent* Systems, Apr. 2024, ISSN: 2640-4567. DOI: 10.1002/aisy.202300679.

- [JL10] J. Loh, L. Dudchenko, J. Viga, and T. Gemmeke, "Towards hardware supported domain generalization in dnn-based edge computing devices for health monitoring," *IEEE Trans*actions on Biomedical Circuits and Systems, pp. 1–10, 2024, ISSN: 1940-9990. DOI: 10. 1109/tbcas.2024.3418085.

## **Chapter 1**

## Introduction

Futuristic scenarios in science fiction envision high cognitive abilities in compact form factor. One example is an exoskeleton armor, the so-called "Iron Man Suit", which possesses the capability to monitor the health parameter of its wearer and the environment in real-time. The captured data, such as blood toxicity or flight acceleration, are analyzed instantaneously for accurate interpretation and corresponding reaction. Although this example describes an ideal system interaction in a fictitious story, the core element of continuous data stream analysis in mobile devices is highly desirable in many application fields, especially the domain of healthcare. In this case, the monitoring of vital parameters enable automated detection of asymptomatic heart anomalies, such as atrial fibrillation (AF) [1], and, potentially, save lives with early treatments by healthcare professionals. Recent studies already aim to incorporate this functionality in wearable devices, e.g. smartwatches [2].

When we imagine the idealistic scenario of vital parameter monitoring, one essential component to realize the desired cognitive ability is the data processing component. It receives data from sensors and processes it into an interpretation of the data. The challenges involved with the design of such data processing component for mobile devices usually revolve around two opposing targets: High QoS and low power consumption [JL1]. One the one hand, high quality analysis require high complexity [3] and, therefore, high power consumption. Low power devices, on the other hand, feature long device operation, but are severely limited in terms of task complexity and quality [4]. Especially, biomedical signal processing requires robustness for the classification algorithm, since distinctive features in the data are very subtle and sensitive to noise. As the characteristic electrophysiological signal is measured indirectly through surface potentials of the patients body [5], the variety of noise sources is diverse and can impact data analysis significantly.

ANN provide the capability to solve highly complex tasks. One prominent example is the classification of predefined and labeled datasets, in which it achieves remarkable performances even exceeding humans in several data domains, such as images [6] or ECG data [3]. Nevertheless these state-of-the-art networks come with a significant cost. Best performing ANN models require massive amounts of memory and computational resources in traditional hardware [7]. Based on the trends over the last decade the computational requirements are increasing in an exponential rate [8]. In the context of mobile ECG monitoring, this trend poses significant challenges on multiple abstraction levels of the device design process. In essence, the design of the ANN model as well as the hardware component performing its inference need to be rethought from scratch to provide "the best of both worlds".

To push the limits of state-of-the-art data processing components, the research field of *Neuromorphic Computing* draws inspiration from its biological reference - the human brain [9]. Optimized over countless generations in evolution, the human brain is able to achieve cognitive tasks not yet in reach for conventional computing systems, whilst only consuming little power [10]. Although the field of neuromorphic computing started with the emulation of analog implementations of neural features in silico [11], it evolved into a wider domain focusing on non-von Neumann computers with neuroinspired functions and structures [9]. In the context of vital parameter monitoring in mobile devices, these neuro-inspired features promise to achieve both high QoS and low power consumption at the same time. One prominent neuro-inspired principle is the communication with sparse activations, or more specifically spikes [12]. SNNs embody the core feature of many state-of-the-art neuromorphic systems on both a large and small scale [13]. While these systems face different challenges and target different objectives, a major desired feature of spiking communication is the compact representation of information. In the end, this representation is expected to provide the same information content for less energy compared to traditional methods. For practical applications like ECG classification, a SNN model can be acquired with different approaches.

To summarize, the continuous monitoring of biomedical signals with high diagnostic quality pose a significant challenge for specialized hardware in mobile devices. Within this domain, neuro-inspired concepts, such as neural networks and even more biologically inspired features, promise high quality classification, which need to be fitted for real-time application case. In this application, the low data-rate of the input signal compared to the clock frequency of modern digital circuits [14] introduces a unique design constraint to be considered in the optimization process.

### 1.1 Thesis Contributions

The target of this thesis is to answer the following research question:

What neuro-inspired concepts enable low-power digital processing of real-time, low data rate signals?

First, a suitable application task, i.e. ECG classification is defined for exploration. Especially, the prerequisites need to be clarified for a systematic selection and optimization of available methods. In essence, the state-of-the-art design methodologies and evaluation methods are discussed in the context of the target application (see Section 2). Then, the adapted design methodology and evaluation method is applied in the design of an ANN accelerator. The co-design of the resulting ECG classification systems spans across multiple abstraction levels of a digital design flow. The design steps include algorithm design, e.g. training and optimization of an ANN classifier, over the mapping to hardware components in system level and RTL down to the structured placement of standard cells (see Section 3). The ANN accelerator is used as a baseline to incorporate two features, which are observed in a biologically plausible system. Firstly in Section 4, domain-invariant feature representations are incorporated into the ANN classification system. These are realized with hardware friendly correction layers inserted into a pre-trained ANN, such that the features are aligned across domains with low hardware overhead. Secondly in Section 5, the ANN classification system is converted into an equivalent SNN. Its quality of the classification is undistinguishable to the fixed-point reference, while the sparse activation representation as well as its corresponding temporal computation result in less addition operations than the ANN baseline. In the end, this thesis shows that systematic selection of neuro-inspired concepts can ensure high-quality classification, robust classification and low power real-time processing of low data rate signals.

### Chapter 2

# **Prerequisites for Efficient Real-Time Processing of Low Data Rate Streams**

Considering the overarching research question from Section 1.1 the investigation needs to cover following items:

- Representative Application: The chosen application benchmark needs to reflect the expected

target features. A well fitting use case is ECG monitoring as it is commonly sampled with a

low data rate and benefits from the real-time processing in the digital domain. In Section 2.1,

the properties of ECG signals, the corresponding processing task and their benchmarking is

discussed in the context of recent literature.

- System Scope: The state-of-the-art in neuro-inspired concepts, especially neural networks, exhibit different granularities of bio-plausible features as well as digital processing concepts.

To enable a structured exploration over existing and novel methods, the scope of the exploration needs to be defined to a promising subset within a global application context. Section 2.2 discusses the suitability of ECG processing on the edge, in particular ANNs, as an effective early warning system and design concepts, which target this setup for pre-processing on the edge.

- Design and Evaluation Strategy: Despite an existing pool of valid methods, which can be

used for a design space exploration, a methodology is required to systematically select methods

to converge against high quality designs. Especially, the co-optimization of both algorithm

model and hardware requires design steps across multiple abstraction levels, which need to be

guided by application specific constraints. Section 2.3 outlines a methodology for design space

exploration specialized for streaming input data and discusses an energy estimation policy for ANN workloads

### 2.1 Application Context of ECG Monitoring

An *electrocardiogram* (*ECG*) is a time-continuous signal representing the electrical activity from the human heart and is used for the diagnosis of life-threatening heart conditions [15]. Surface potentials on the skin are picked up over electrodes and the difference between two electrodes is measured over time. These measurements are used to derive the electrical stimuli responsible for heart contraction. Potential deviations from standard cardiac rhythms indicate abnormal function of the heart and, thus, a cardiovascular disease (CVD).

### 2.1.1 Cardiac Electrophysiology

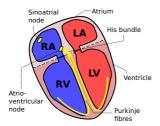

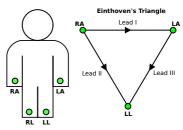

(a) Pacemaker cells automatically generate stimuli for propagation in specialized conduction tissue to trigger the contraction of the heart muscle sections in a specific order.

(b) Position of electrodes for standard limb leads I (LA  $\to$  RA), II (LL  $\to$  RA) and III (LL  $\to$  LA)

Figure 2.1: Overview of cardiac stimuli for the heart and the first three ECG leads and corresponding electrode positions at the extremities adapted from [15].

Figure 2.1 shows a minimal overview of cardiac electrophysiology. The heart muscle is automatically stimulated by electrical signals generated by pacemaker cells and their spread through special conduction tissue (see Fig. 2.1a). The resulting contraction of the heart muscle leads to blood pumping through the cardiovascular system. A non-invasive method to capture these electrical stimuli is to attach electrodes on the surface of the skin and derive directions between the attached electrodes, i.e. leads. A standard ECG consists of 12 leads to capture the electrical propagation front from a wide variety of angles and planes. The first three leads are visualized in Fig. 2.1b. In principle, they capture three different angles within frontal plane of the human body. Since the propagation front of

the electrophysiological signal is three dimensional, 12 leads should provide sufficient information for analysis in all directions.

### 2.1.2 Mobile ECG Monitoring

Although the 12 lead ECG is preferable in a clinical setting for maximum amount of information, it is not practical to realize in a mobile setting. An effort to develop wearable cardiac monitoring devices started in the early 1950s, i.e. the Holter monitor [16], and still persist today to achieve the "ultimate" monitoring device without restrictions for the wearer. While classical Holter monitors consists of a recording device taped to the patient and attached to a reduced number of leads, modern heart monitors even go down to single lead heart monitors. These feature different form factors and user interfaces such as a heart patch [17], a smartwatch [2] or a dry electrode pair for fingers [18]. The influence of the device form factor is even more pronounced in implantable cardiac monitoring (ICM) devices [19].

As evident simply from the diverse set of device form factors, the setup to capture ECG data is not always coherent. One example is the position of electrodes, which differs from device to device, i.e. finger-to-finger vs. two adjacent patches. The variety of measurement setups is reflected in the variety of ECG datasets in popular databases, such as PhysioBank [20]. Furthermore, external noise is also influencing ECG data quality through e.g. baseline wander, power-line interference or muscle artifacts [21]. Evidently, the influence of noise is more pronounced in a mobile application setting than a stationary setup. As noise sources can be mitigated in a known environment, one challenge in a mobile monitoring setting is the handling of noise in an unknown environment.

Since a variety of CVD is associated with characteristics within the ECG beat, it is essential to distinguish those features from noise. In the continuous monitoring use case, the arrhythmia types are typically asymptomatic, i.e. do not exhibit explicit symptoms. One of the most common cardiac arrhythmia is AF. In 2023, the European Union is anticipated to have an estimated amount of 14-17 million people diagnosed with AF [1]. This trend is increasing every year and these patients are likely to exhibit life-threatening diseases, which is often missed due to the lack of proper monitoring methods deployable in daily life. It has been shown that screening at-risk population with conventional single-lead measurements is already cost-effective [1]. Further improvements in terms of coverage of population can be achieved by automating the screening process using already prevalent wearable devices.

### 2.1.3 Application Scope of This Work

Within this work, the PhysioBank database, in specific datasets with AF as a classification task is selected as a benchmark for the classification systems. For instance, the *Computing in Cardiology Challenge 2017 (CinC'17)* [18] is chosen, since it features single lead measurements in a large-scale, i.e. roughly 8500 samples, and comprises one of the largest collection of labeled AF data at its time of creation. Further, it mimics a real-world conditions by using the commercially available AliveCor device for classification with a special focus on AF detection. It is ideal as an application baseline as it necessitates long-term ECG monitoring in a low-power mobile device. Not only is the detection of AF complex due to its sparse sensitive features, but it also is a real-world problem highly relevant to the general public. Further, it poses challenges in the algorithm-hardware co-design of the specialized hardware to enable high quality processing capabilities on the edge.

### 2.2 Pre-processing on the Edge with ANNs

The co-design of digital processing modules requires both fine-tuned classification algorithms and tailored hardware to satisfy objectives for both high-quality classification and low-power processing.

### 2.2.1 State-of-the-art ECG Classification Using ANNs

Classification with ANNs reaches back more than two decades starting with multi-layer perceptrons (MLPs) [22], [23]. Publicly available datasets, such as the MIT-BIH Arrhythmia Database [24] or CinC'17 [18] within the PhysioBank database [20], accelerated ANN research. In combination with better access to better graphics processing unit (GPU) acceleration for training and supporting machine learning frameworks, like PyTorch [25] and TensorFlow [26], a large variety of classifiers emerged.

State-of-the-art ECG classification is summarized in various surveys, e.g. [27]–[29]. The predecessors of ANN models are traditional machine learning approaches such as support vector machines, decision trees/random forest, etc. Given well-selected expert features they already perform very well on even complex datasets, such as CinC'17 [18]. Within early machine learning classification, simple ANN models such as MLPs are also utilized, often for early ECG datasets, i.e. MIT-BIH arrhythmia, or as a baseline for hardware implementations. One prominent type of an ANN is the convolutional neural network (CNN). In the case of one dimensional temporal data, such as ECG, the network is also often described as a TCN [30]. In general, many ANN topologies have been tested for ECG

classification, such as recurrent neural networks (e.g. long-short term memory [31], gated recurrent units [32] etc.), deep belief networks [33] and exotic archetypes with probabilistic features or fuzzy logic [27]. The combination of different models is also common, further increasing the variety of architectures.

The classification process is mainly split into two consecutive stages: data pre-processing and the classification. The former deals with the extraction of relevant information in terms of features, which include e.g. interesting frequency components in the signal or morphological features etc. [34]. Alternatively, the features are extracted using trained feature extractors along with the classifier [35]. The latter deals with the analysis of extracted features into the prediction of a label. This usually involves a training process using labeled data from the benchmark dataset.

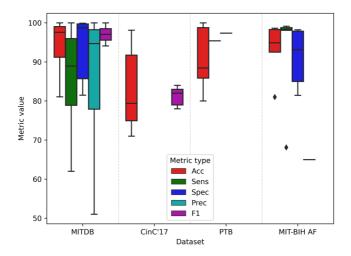

Figure 2.2: Example distribution of quality metrics for ECG classifiers derived from references in [28].

In this process, the target metric is decisive to determine the quality of the classification task, i.e. quality of service (QoS). Figure 2.2 shows an excerpt from the key performance indicator (KPI) of recent ECG classifiers. While the performance of the classifiers is seemingly very high, not only the data specifications vary in terms of above mentioned parameters, but also the classification task is redefined. For instance, the tasks include user authentication, i.e. classifying patients, specific sets of beat types, beat grouping schemes, i.e. ISO [36] or custom, or global labels for signal segments. The consequence is that there are low complexity ANNs, which can solve low complexity tasks

down to no error, and there are high complexity ANNs, which solve high complexity tasks with larger error compared to the same metric. The metric usually revolve around derivations from the confusion matrix, e.g. accuracy (Acc), sensitivity or recall (Sens), specificity (Spec), precision or positive predictive value (Prec), F1 score or harmonic mean of precision and recall (F1). In the exploration in Sections 3 to 5, the AF classification benchmarks are chosen as the target application, as the corresponding datasets, e.g. the CinC'17, require more complicated models and are not yet solvable with near perfect QoS. Thus, the resulting classifiers are expected to scale to realistic test cases

### 2.2.2 State-of-the-art Digital Processing of ECG Classifiers

Despite significant advances in the quality of ECG classifiers, the deployment of those classifiers on edge devices, i.e. smartphone or wearable devices [37], is highly desirable. The motivation is clear: security risks are inherent in the transmission of critical personal data, such as vital parameters, for cloud processing [38]. Local data processing eliminates those security risks and also enables direct and personalized feedback on your own device. Nevertheless, these edge devices are limited in terms of battery capacity and their computational resources, since they are designed to be convenient in daily life. Hence, the overall deployed system needs to adapt these advanced ECG classification algorithms, i.a. ANN models, towards energy constrained devices and these devices need to consume low power in a continuous operation mode.

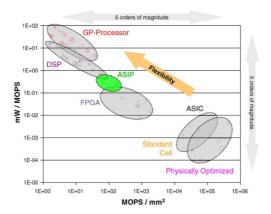

When considering the options to realize the digital back-end of the ECG classification device, the range of digital computing architectures is diverse. Conceptually, the architectures can be categorized in terms of flexibility and include, for instance, programmable processor architectures, field programmable gate arrays (FPGAs) and application specific integrated circuits (ASICs).

### State-of-the-art Edge Processing of ECG classifiers using General-Purpose Processors

For instance, Kim et al. uses a single instruction multiple data (SIMD) processor to execute the ECG signal processing workload [39]. The algorithmic operations are translated into available instructions of the processor architecture, e.g. through a compiler. The degree of parallelism achieved is dependent on the instruction set available. Typically the processor comprises a reduced instruction set computer (RISC) architecture, such as an ARM processor [40], for less complex core logic and specialized instruction set. The optimization of program code for the specific processor architecture

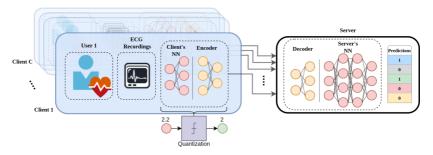

is essential to reduce the latency and program memory. This software-hardware co-optimization process already leads to highly efficient designs consuming power down to tenths of a microwatt [39], [41] for low complexity ECG processing algorithms. Another method is to use the programmable processor architecture on the edge to execute a reduced classification model resulting from the *split learning* technique. For instance, Ayad et al. [42] uses the split learning technique to split an ANN model into two separately inferrable models: a large model on the server and a small model on the edge. NVIDIA Jetsons are used to deploy the reduced model on the client side. Figure 2.3 shows

Figure 2.3: System overview of ECG classifier with a modified split-learning mechanism from [42].

the overall concept of the split learning mechanism. This concept allows to adjust the size of the ANN model, which is inferred on the edge. The general quality of the classification remains high, as intermediate features are transferred to the server side for further processing. From the perspective of the client, the computational workload and the memory required to store the model is adjusted on the algorithm level. The size of the resulting client side model after training will influence both the memory consumption and the computational efficiency on the client processor. The deployment of the model on the processor architecture is well supported ML frameworks like TensorFlow [26] and PyTorch [25]. Further reductions is achieved through ANN model quantization from a floating-point to fixed-point. It is shown that the energy consumption of one MAC operation is extremely reduced. Taking a 32-bit floating-point number representation as a reference, the post-training quantization of the ANN model can consume just 0.5% of the original energy in 4-bit fixed-point executing otherwise the same operation. However, a minor quality reduction needs to be tolerated due to the reduced representable range of numbers.

### State-of-the-art Edge Processing of ECG classifiers using FPGAs

In contrast to programmable processor architectures, FPGAs are not limited to several processing cores with a fixed hardware architecture. Instead, it consists of programmable logic blocks and interconnects. During the design time the logic blocks and interconnect is configured with a hardware description language (HDL). The circuit design can be designed to feature arbitrary logic level designs within the available resources of the FPGA. In the case of ECG classification systems, Lu et al. designed a CNN accelerator for ECG classification of MIT-BIH Arrhythmia Database [43], [44]. It features dedicated weight, bias and activation memory and buffers as well as an array of processing units. As logic optimizations are available, larger algorithm designs could be inferred with a larger amount of parallel processing units, therefore achieving remarkable hardware resource efficiency of up to 16.71 [44] GOPS/kLUT. Even though FPGAs are very powerful in the prototyping phase of the hardware design, the reconfigurable hardware requires trade-offs in terms of available resources, such as number of logic blocks, memory blocks, component sizing, power partitioning etc. Thus, the utilization of available resources is key for the efficiency of the deployed system. For instance, it is unlikely that all available resources are actually used for a specific design, as the FPGA is not designed with specific architecture with specific amount of hardware modules in mind. In this case, the idling components are still contributing to power consumption, e.g. through leakage, and, hence, significantly influence the efficiency of the overall system.

#### State-of-the-art Edge Processing of ECG Classifiers using ASICs

In contrast to FPGA implementations, ASICs are intended to be task-specific instead of a general purpose design. A HDL description is directly mapped to transistor layouts, which is fabricated in a foundry, e.g. in a complementary metal-oxide-semiconductor (CMOS) technology node. Early ASIC implementations for ECG processing focus on sample-and-send type devices, i.e. the edge device's function comprises the sampling of the ECG only and sends the data to another device for further processing [45], [46]. Another task with limited processing on the digital back-end is the delineation of the ECG signal. This task deals with the extraction of biomarkers in characteristic waves, which are diagnostic for heart arrhythmia [34]. Although early low complexity algorithms, such as the Pan-Tompkins algorithm [47] or others [48], already achieve sufficient detection quality, they are further investigated for more robustness across datasets and input data. One example is the ECG delineation using CNNs, in specific a U-Net architecture with around 12 convolution blocks [49]. It

is evident, that computational complexity (CC) is increased significantly to achieve greater capacity for generalization and QoS. Dedicated HW implementations for ECG delineation, however, focus on the efficient implementation of early algorithms, i.e. wavelet-based [50], [51] or Pan-Tompkins [52]. The trend towards low complexity algorithms in the hardware design domain extends into the task of ECG classification using ANNs. For instance, MLPs are used to extract features to compare with similarity functions [53], [54] or directly as the classifier using extracted features as input [55]–[57]. Interestingly, the complexity of the implemented MLP computations spreads over two orders of magnitude for classes like premature ventricular contraction, i.e. 3 neurons [55], in comparison to clinical AF, i.e. 156 neurons [57].

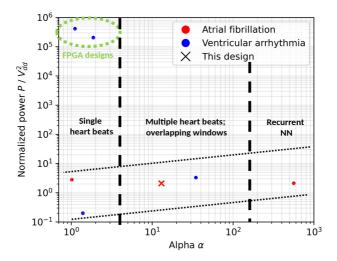

In contrast to MLP architectures, there are more complex ANN topologies for ECG classification on ASICs, such as CNNs [JL1], [JL3], [58], [59], gated recurrent unit (GRU) [35] and long-short term memory (LSTM) [60]. Typically, these architectures classify the raw input either sampled equidistantly over time [58] or using a level-crossing analog-to-digital converter (ADC). Other methods pre-process the signal using digital filters. For instance, discrete wavelet transforms [JL1], [JL3] or trainable filter kernels [35] are used to extract features e.g. in the frequency domain. More biologically inspired ASIC implementations utilize SNNs for ECG monitoring. These include large-scale multi-core [61], [62], mixed-signal single-core [63], [64] and digital single-core solutions [65], [66]. These works target the design of a SNN accelerator using a bottom-up approach. For instance, variants of the integrate-and-fire (IF) neuron are implemented in dedicated circuits to support the model behavior [63]–[66]. Then, the accelerator is designed with the composition of those fixed modules. Other works utilize existing neuromorphic solutions such as Loihi [62] or DYNAP [61] to reconfigure the architecture towards the ECG classification application.

#### Comparison of Computing Architectures for Ultra-Low Power Processing

Figure 2.4 shows the quantitative evaluation of different digital computing architectures scaled to an example technology node. The programmable general purpose processors feature a low energy and area efficiency. Special purpose circuits, such as full-custom ASICs or standard cell-based design, show superior energy and area efficiency, but feature only limited amount of programmability and/or reconfigurability. In the shown example the difference in efficiency spans across multiple orders of magnitude. It is evident that ultra-low power requirements are most likely to be achieved by ASIC designs.

Figure 2.4: Energy and area efficiency for digital computing architectures scaled to 130-nm CMOS technology [67].

## 2.2.3 Cascaded Classification of ANN classifiers

From a system perspective, a monitored ECG does not contain an equally distributed amount of traces with different labels. In an optimal case, the system only records normal sine signals in a healthy patient. In a realistic setup, noise artifacts and uncritical heart conditions can influence the recording such that some segments need to be identified as such in irregular intervals. Further, the appearance of CVD is usually sporadic [1] and occupies a low percentage of the recorded data stream.

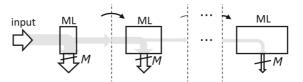

Contemporary systems utilize preliminary wake-up stages to reduce the overall system power consumption. The concept leverages skewed data distributions and complexity necessary to classify certain classes to concentrate the major computational workload on low complexity classifiers [68]. High complexity classifiers or eventually a human expert are "activated" in problematic cases, where the preliminary classification stage is expected to fail.

Preliminary investigations show that the CC, i.e. the number of operations necessary to compute the ANN model, can be adjusted over multiple orders of magnitude, while QoS, i.e. the quality of the classification, remains the close to the high complexity model [JL2]. A detailed analysis of pass-on-criteria is performed for off-the-shelf classifiers to investigate the impact on QoS and CC for configurations of 2- and 3-staged cascades. Figure 2.5 shows the concept of the cascaded classifier. All input samples first pass through an initial classifier of lowest complexity, i.e. lowest number of computation, to "filter" high confidence samples. When samples do not exceed a certain confidence threshold, the sample is passed on to the next classifier with higher complexity. The complexity of

Figure 2.5: Structure of cascaded classifier for balanced datasets and MLs classifiers, here ANNs, with increasing CC [JL2].

the classifiers are chosen in such a way, that a classifier with higher CC also results in a higher QoS. Consequently, the last classifier is the best performing classifier with highest QoS, but also highest CC In the case of image classification, the quality metric is the prediction accuracy. Confidence values are calculated on the output vector of each classifier, which contains prediction probability  $p_i$  of each class i. The L1 norm of this vector should be guaranteed to be 1, such that probabilistic metrics can be applied on the vector. This is achieved by linear normalization or the softmax function. The confidence metrics, which are investigated within [JL2], are the absolute value of the prediction, "best versus second best", variance, kurtosis, entropy and Kullback-Leibler divergence. It is observed, that the first four confidence metrics perform similarly well on the MNIST dataset achieving a trade-off between accuracy and CC (normalized MAC operations). The range, in which the CC can be adjusted gracefully is five orders of magnitude for MNIST and two orders of magnitude for CIFAR10. With only small error tolerances of 1 %, a CC reduction of 263.17  $\times$  and 2.55  $\times$  is possible for MNIST and CIFAR10, respectively.

In the end, this investigation shows that a low complexity ANN classifiers are capable to achieve high QoS for a majority of samples. The split of the classifier into multiple stages proves especially useful, if the preliminary stage is used to effectively filter "easy" samples. In the case of an ECG monitoring system, the target is to design this preliminary stage well, such that only relevant or rare indecisive events are forwarded to reliable ANN models or trained experts.

## 2.2.4 System Scope of This Work

As seen in state-of-the-art solutions, the efficient monitoring of ECG signals can be tackled from a variety of perspectives. In the following, a use case is sketched to provide a context for the implemented classifier system. The use case provides proper requirements for the optimization of the system.

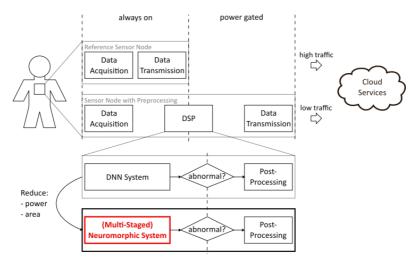

Figure 2.6 shows an application scenario, where the continuous monitoring of ECG data can be utilized. The target classification system is applied in a sensor node, where the ECG data is acquired

Figure 2.6: Hardware accelerator as gating mechanism for post-processing steps.

and processed for subsequent analysis. The top row of the diagram shows a typical sample-and-send setup. In this setup, the data is sampled on the mobile device and directly transferred to an expert for further processing or manual monitoring. Evidently, there is no digital processing on the device resulting in high data rates. The second scenario processes the raw data inside a digital processing module, such that compressed information about the monitored system, here a patient with a ECG trace, is sent to the expert. The compressed information is, for instance, classified labels or snippets of an ECG trace, which is found to be abnormal. This highly reduces the data transmitted resulting in less time spend by the expert. The challenge is to design an efficient pre-processing system to detect the abnormal classes with high quality and low power. A high quality classification guarantees that only relevant samples are selected for expert diagnosis and no critical samples are neglected. A low power operation is necessary for long monitoring durations as is necessary for critical sparse features as AF. Considering the energy budget of battery cells, which are available today, the target consumption for several weeks of operation is in the region microwatt for the whole system.

The scope of this work aims to design the digital signal processing module for this use case. In this use case, we assume a digital data stream as an input and a classified label as an output. An assumption is that the continuous input data stream is directly processed by the classification system in an always-on manner, such that the coverage of the whole stream is guaranteed. Possible post-processing steps can be activated based on the acquired label. A DNN classifier is designed

such that it can be computed on dedicated hardware components targeting the always-on processing of this data stream. Ultra-low power requirements for limited energy budgets are achievable in an dedicated ASIC design. For a long-term monitoring setup, an operation of multiple weeks with a battery charge is assumed as the target for the ECG classification system. For contemporary battery cells, a realistic target covering this time frame would result in average current consumptions in the region of microampere [69]. Therefore, an ASIC solution is targeted as a proof-of-concept. In the next chapter, the methodology is discussed how to systematically explore the design space and evaluate the performance of the target solution.

## 2.3 Design and Evaluation Strategy

The target is to design a system, in which the algorithm, i.e. the DNN classifier, is adjusted to its hardware and vice versa, such that multiple optimization objectives are met. In the following, we denote this as *algorithm-hardware co-design*. First, we evaluate how the state-of-the-art is addressing the co-optimization of DNNs. Then, we derive our own co-design strategy tailored to our target application.

## 2.3.1 State-of-the-Art of Energy Estimation of Batched ANN Workloads

Influential literature has targeted design schemes for the efficient processing of DNNs, as high classification quality in ML tasks requires high computational cost. Especially, the inference is performed on embedded devices and, hence, the main subject of previous works. It has been identified that the efficient processing of popular reference DNN architectures, such as AlexNet [6], relies on an efficient dataflow [70]. In specific, the energy required to access data in memory is up to 1-2 orders of magnitude more than the energy to process one MAC operation, i.e. the most common operation in the DNN. Hence, the orchestration from memory to processing unit plays an important role in the evaluation of the DNN workload.

Considering ANNs trained in a supervised fashion, labeled data is used to provide desired inputoutput pairs for the model and allow the backpropagation of error values during the training phase. Computer vision benchmarks serve as baselines for the research and development of ANNs and corresponding ASICs accelerators. For instance, MNIST sparked initial research on ANN models, e.g. CNNs [71], and continues to be used for proof-of-concept designs for more advanced neuro-inspired principles, e.g. memristive SNNs [72], even until today. Nevertheless, the increasing complexity of more realistic larger scale datasets, i.e. ImageNet [73], forces algorithms scale in their complexity and triggered key innovations in ANN research.

Popular ANN models resulting from the ImageNet challenge are e.g. AlexNet [6] or ResNet [74]. The former spawned a variety of digital accelerators specifically targeting DNN, i.e. ANNs with deep layered architectures, which are described by a major body of survey works on ANN accelerators [70], [75]. A major bottleneck in larger ANN models is that the amount of parameters, i.e. weights and biases of the ANN, exceed typical on-chip storage/memory capacities. Therefore, off-chip memory, e.g. DRAM, needs to be accessed to buffer required chunks of model parameters for processing. The dataflow regarding the movement of parameters and activations is a major focus in DNN accelerator design. The access sequence is crucial for the consumed energy per inference, as each memory access to different levels of the memory hierarchies consume different energy. For instance, it is less desirable to access off-chip memory than local register files as the consumed energy is up to two orders of magnitude higher [70].

A systematic design space exploration typically uses a quantitative model for KPI evaluation. Analytical models provide a good initial measure to quantify the consumed energy for a large design space of accelerator architectures with different topologies [76]. Further they provide an indicator for the suitability of dataflow schemes for DNN specific workloads.

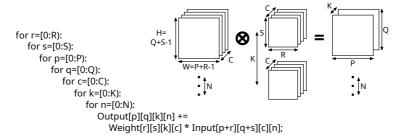

Figure 2.7: Loop nest representation of computational workload of a 2D-convolution operation for a batch of input feature maps [76].

Figure 2.7 shows a convolution operation represented in nested loops over the corresponding dimensions of two dimensional feature maps. In the case of batched image data, there are seven dimensions: three dimensions for the output feature maps, i.e. P, Q (spatial) and K (channel), two dimensions for the convolution kernel, i.e. S and R (spatial), one dimension for the input features maps, i.e. C (channel), and one dimension for the batch, i.e. N. The other dimensions, e.g. spatial dimensions of the input feature map, can be derived, respectively. Based on this representation, loop

nest optimizations are derived from predetermined PE array sizes and memory limitations. The loops can be tiled or unrolled spatially or temporally based on the hardware architecture. In the end the actual numerical dimensions of a specific DNN layer can be inserted, which estimates the number of cycles and memory accesses for the specified workload.

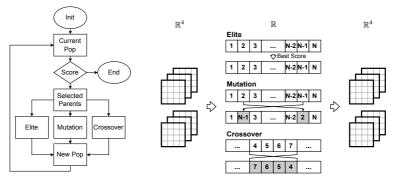

However, conventional DNN energy estimation methods typically reduce the loop nest optimization problem [76], [77]. For instance, the regularity of DNN workloads is used to abstract to calculation of memory accesses. Parashar et al. calculate the first, second and last iteration for the loop tiles for extrapolation [76]. Other works reduce the problem to values indicating the number of tiles within one loop, i.e. how many iterations are required to process one loop dimension with given parallel PEs, e.g. [77]. This is possible, since many DNN accelerator architectures operate in pre-defined patterns, e.g. execute convolution row by row from left to right. One example are two nested loops: The  $x_1$  iterator of the inner loop increments until the end of the range. Then, the  $x_2$  iterator of the outer loop increments, while the inner loop restarts from the start of the range. Above mentioned loop nest optimizations consider the loop ordering, tiling, unrolling etc., however, they do not allow for arbitrary sequences of  $(x_1, x_2)$ . An example would be to traverse all combinations of the 2D-tuple  $(x_1, x_2)$  without a sequential order of  $x_1$  or  $x_2$ .

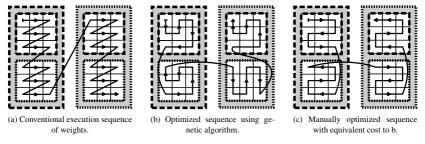

## 2.3.2 Exploration of Dataflow Sequences for Convolution Operations

Previous works distinguish the dataflow based on which data in the convolution is held stationary inside the PE, which are denoted as input, weight and output stationary dataflow<sup>1</sup> [70], [78]. Typically, the number of data held in PEs is less than the number of elements in the processed data tensor. In the conventional dataflow models, the sequence is predetermined by the loop order in the loop nest representation (see Fig. 2.7). It is straightforward to process these loops in a row-by-row or column-by-column fashion. However, the design space of possible sequences is theoretically much larger. This raises the question whether another sequence could provide a more efficient alternative, since memory accesses contribute largely to the energy consumption [70].

From a different perspective, the problem can be viewed as a sequential traversal of elements in a tensor. Instead of iterating the tensor on a dimension-by-dimension basis, a curve can be defined, which passes through all elements in the tensor. In mathematics, the search for these *space-filling curves* date back more than a century [79], [80]. The idea is that these curves traverse the

<sup>&</sup>lt;sup>1</sup>For simplicity we omit special cases such as row stationary dataflows in our investigation

multi-dimensional space, such that "locality" is preserved, i.e. points, which are close in the multidimensional grid, are also close in the traversal order [81]. However, the sequence in the dataflow models require different optimization constraints, which possibly results in solutions with different properties than already proposed space-filling curves.

Therefore in our exploration, we approach the search for the sequence from a new perspective. The concept is to define costs related to the execution sequence in a dataflow model. Based on this cost model, any sequence has a cost, which can be compared with each other and optimized globally. The required steps to achieve this are summarized as follows:

- 1. Memory model to estimate access patterns of an ANN workload

- 2. Index mapping of data samples in PE to required data in memory

- 3. Cost of a sequence of memory accesses during a convolution operation

First, a model needs to be established to define the memory access patterns resulting from different sequences. Then, the relationship between the data in the PE array and the corresponding data, which needs to be stored in the on-chip memory, is defined in a mapping function. This mapping function relates a set of indices from one dataspace to another. This is used in the last step to find overlaps between two consecutive states in a sequence. The cost of this sequence can then be calculated as the sum over all states in a sequence. In the following, these three steps are further presented in detail.

## Memory model

As the memory access cost from off- and on-chip buffers deviate by one or two orders of magnitude [70], it is key to model the number of these two hierarchies separately. We investigate a memory hierarchies with three levels: Off-chip, on-chip memory and registers on the PE level (see Fig. 2.8a). In this model the on-chip memory is limited in size, while the off-chip memory is able to contain all data for a typical DNN inference.

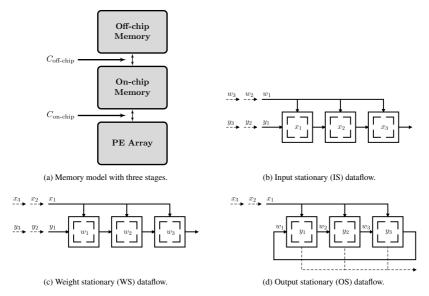

The costs to access the on-chip and off-chip memory are denoted as  $C_{\rm on-chip}$  and  $C_{\rm off-chip}$ , respectively. The access pattern of the on-chip and off-chip memory and, thereby, the number of accesses  $N_{\rm on-chip}$  and  $N_{\rm off-chip}$ , as function of the dataflow scheme used by the DNN accelerator. The considered dataflow schemes are depicted in Fig. 2.8b, Fig. 2.8c and Fig. 2.8d. The dataflow is visualized for the example of the systolic array with three PEs [78]. One cell represents a PE and contains the stationary data. It calculates one MAC operation, i.e. multiplies two values and subsequently adds one value to

Figure 2.8: Simplified memory model to estimate data access costs for elementary dataflow schemes (adapted from [78]). A cell indicates the PE and the data held within it until all corresponding partial sums are calculated.

a partial sum resulting in a new partial sum. The required data within the on-chip memory is further exemplified for the weight stationary dataflow in the next step - the index mapping.

All in all, the memory model uses the number of memory accesses  $N_{\text{on-chip}}$  and  $N_{\text{off-chip}}$  to calculate the memory access cost

$$C_{\text{mem}} = N_{\text{on-chip}} \cdot C_{\text{on-chip}} + N_{\text{off-chip}} \cdot C_{\text{off-chip}}$$

(2.1)

per inference. The computational cost  $C_{comp}$  is also considered as

$$C_{\rm comp} = N_{\rm mac} \cdot C_{\rm mac} \tag{2.2}$$

with  $N_{\text{mac}}$  being the number of the MAC operations in the DNN inference and  $C_{\text{mac}}$  being the cost to execute one operation. In the end, the total cost is the sum of both components resulting in

$$C_{\text{tot}} = C_{\text{comp}} + C_{\text{mem}}, \tag{2.3}$$

## **Index mapping**

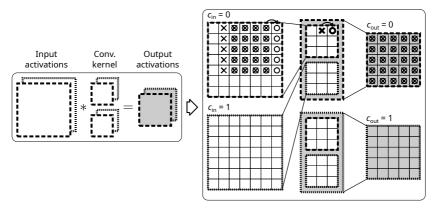

In our investigation, we consider a convolution layer and an input feature map with  $c_{in}$  input channels to produce output feature maps with  $c_{out}$  output channels (see Eq. (2.4)).

$$\mathbf{y}(c_{\text{out}}) = \sum_{c=0}^{c_{\text{in}}-1} \mathbf{W}(c_{\text{out}}, c) * \mathbf{x}(c)$$

(2.4)

Here, '\*' denotes the convolution operation,  $\mathbf{x}$  the input feature maps,  $\mathbf{W}$  the filter kernel and  $\mathbf{y}$  the output feature maps. Similar to Fig. 2.7 we assume three dimensional inputs feature maps and convolve it with four dimensional weights to result in three dimensional output feature maps. It is evident, that the computational cost  $C_{\text{mac}}$  would stay the same regardless of the order, in which input/output channels are computed. However, this is not the case for the memory accesses, due to opportunities for reuse in the on-chip memory.

Since the convolution is performed in a discrete domain, **x**, **W** and **y** can be interpreted as scalar values mapped to integer lattice points in a multi-dimensional space, i.e. dataspace of operand and result tensors [76]. For the design space exploration of dataflow sequences, we want to find the relationship between the dataspace of the tensors, which remains stationary in the PE array, and the other two dataspaces. In the weight stationary dataflow, the objective is to find the location, i.e. spatial indices, of the necessary input and output feature maps given a set of weights. Once this mapping function is known, the overlap between two consecutive states can be calculated. In the following, we showcase this in the example of the weight stationary dataflow, however, the transfer to other dataflow schemes is straightforward.