# Integration of Redox-Based Resistive Switching Memory Devices

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurswissenschaften genehmigte Dissertation

vorgelegt von

Diplom-Ingenieur

Florian Lentz

aus Köln

#### Berichter:

Universitätsprofessor Dr.-Ing. Reiner Waser apl. Professor Dr.-Ing. Michael Heuken

Tag der mündlichen Prüfung: 27. November 2014

Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar.

Forschungszentrum Jülich GmbH Peter Grünberg Institute (PGI) Electronic Materials (PGI-7)

## Integration of Redox-Based Resistive Switching Memory Devices

Florian Lentz

Schriften des Forschungszentrums Jülich Reihe Information / Information

Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

Publisher and Forschungszentrum Jülich GmbH

Distributor: Zentralbibliothek

52425 Jülich

Tel: +49 2461 61-5368 Fax: +49 2461 61-6103

Email: zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Cover Design: Grafische Medien, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2014

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 41

D 82 (Diss., RWTH Aachen University, 2014)

ISSN 1866-1777 ISBN 978-3-95806-019-7

The complete volume is freely available on the Internet on the Jülicher Open Access Server (JuSER) at www.fz-juelich.de/zb/openaccess.

Neither this book nor any part of it may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

#### Abstract

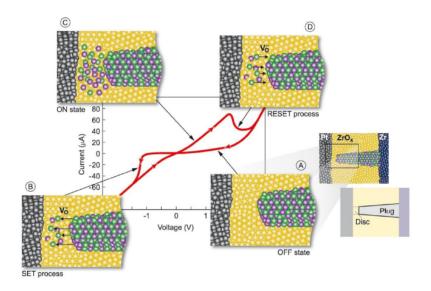

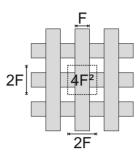

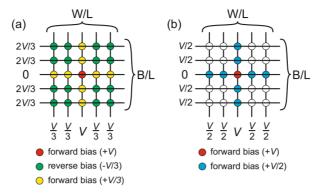

The steadily growing market for consumer electronics and the rapid proliferation of mobile devices such as tablet computers, MP3 players and smart phones make high demands for the nonvolatile memory. Present FLASH memory technology approaches to the end due to physical scalability limits. Therefore, an alternative technology must be developed. For memory technology, not only the storage density and cost are important factors but the power consumption and the writing/reading speed must also be taken in account. Redox-based resistive memory (ReRAM) offers a potential alternative to the FLASH technology and presently is in the focus of research activities. The operating principle of the ReRAM is based on the non-volatile reversible change in resistance by electrical stimuli in a simple metal-insulator-metal (MIM) device architecture. This simple structure enables the integration of ReRAM in passive crossbar arrays, in which each crosspoint consumes only  $4F^2$  (F- feature size) device area. This leads to an ultra-high storage density at reduced cost.

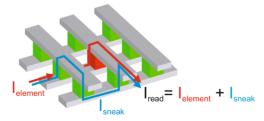

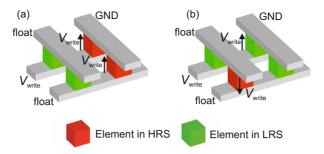

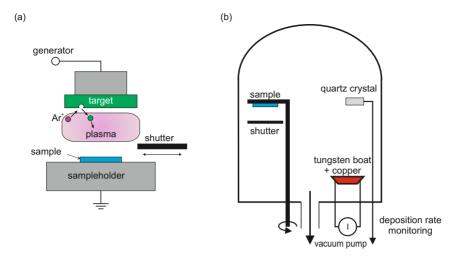

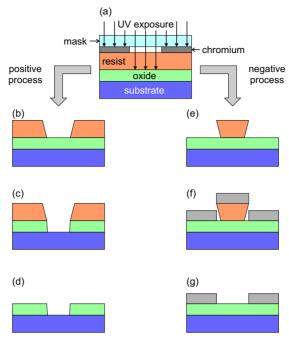

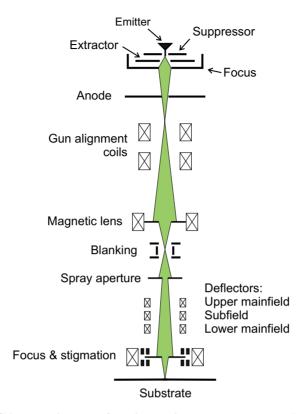

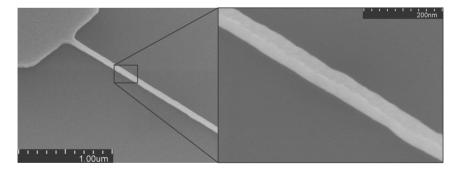

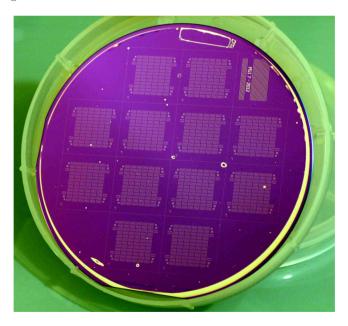

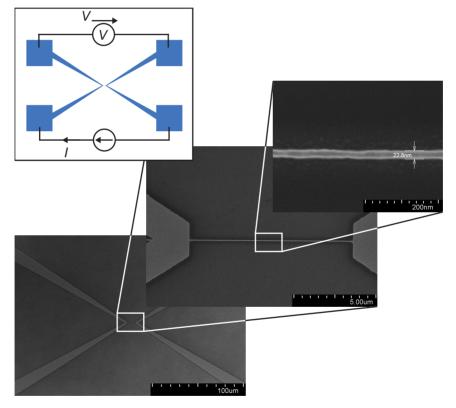

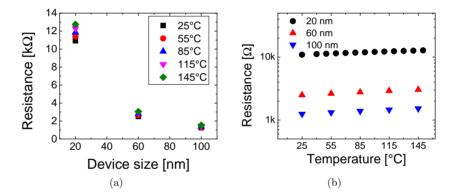

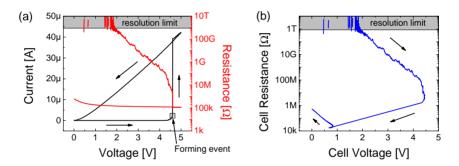

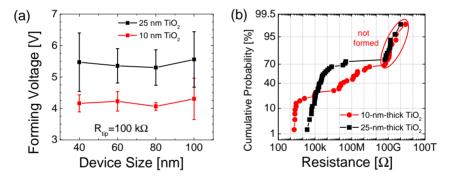

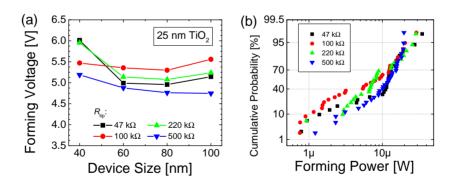

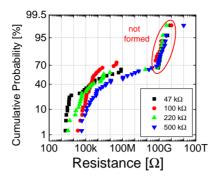

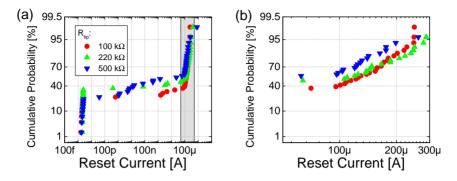

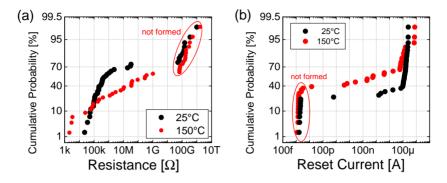

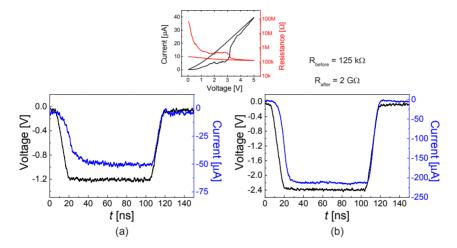

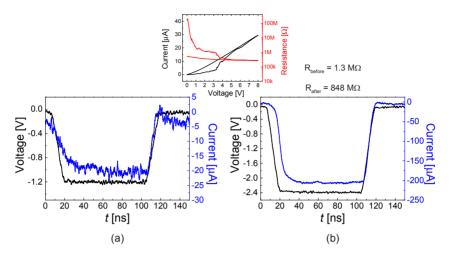

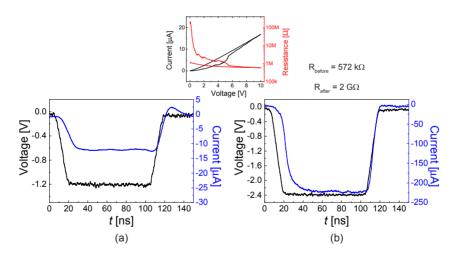

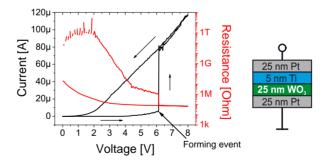

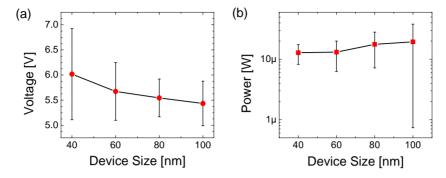

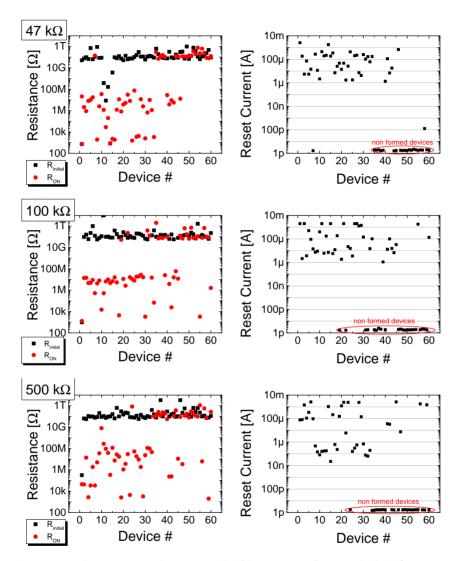

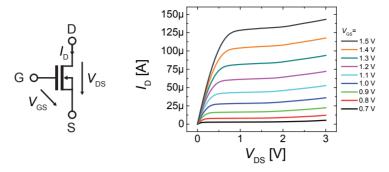

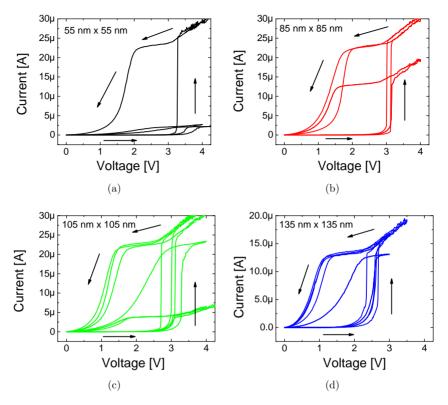

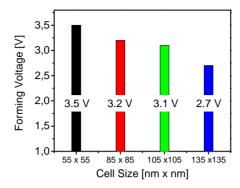

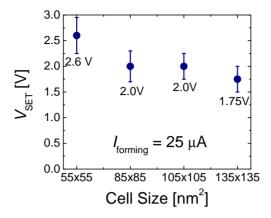

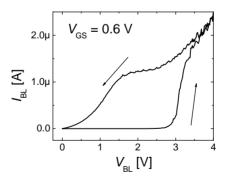

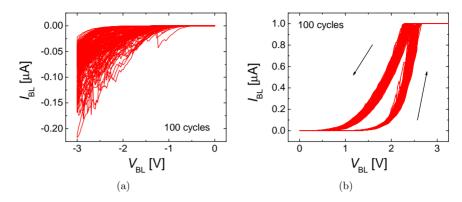

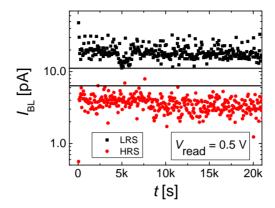

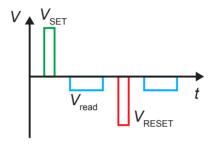

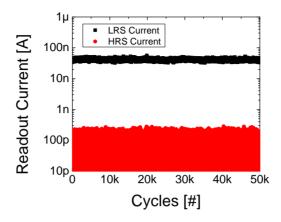

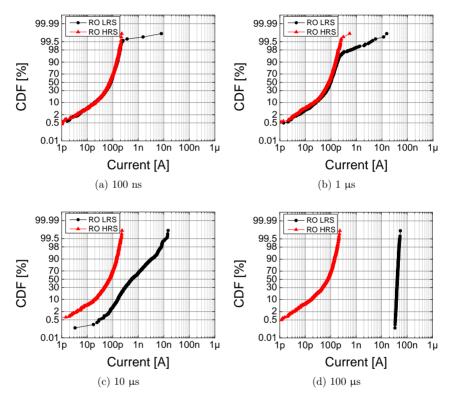

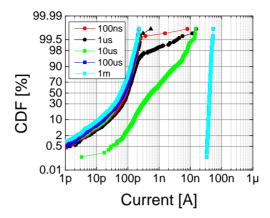

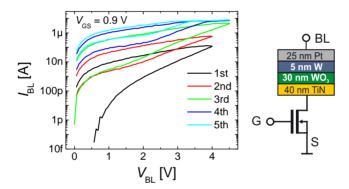

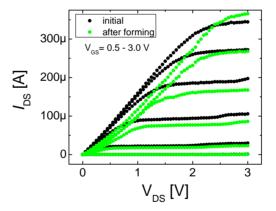

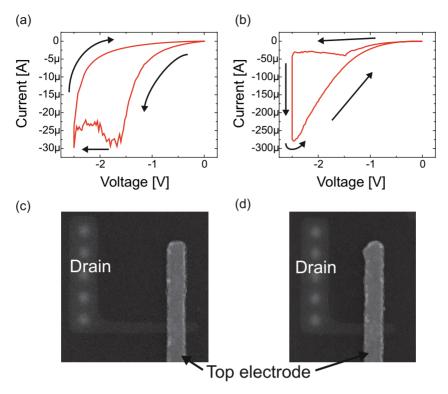

Research on the ReRAM memory elements requires a technology platform that ensures a cost-effective fabrication of the crossbar devices with nanometer feature size. In this thesis, the fabrication processes have been developed based on the nanoimprint lithography, which facilitates both the high resolution (<50nm) and the high throughput at low cost. The stamp for the UV-nanoimprinting is developed with plasma etching and electron-beam lithography. This process facilitates the fabrication of the ReRAM devices sizes ranging from 40x40 nm<sup>2</sup> to 100x100 nm<sup>2</sup>. The fabricated nano-crosspoint ReRAM of different switching layer thickness and different device areas are electrically characterized. In order to toggle the resistance state in the ReRAM device, an electroforming step is generally required. In this work, a systematic analysis of the electroforming process is carried out on TiO<sub>2</sub> and WO<sub>3</sub>based ReRAM cells and the respective switching characteristics are investigated. The switching mechanism is explained by the filamentary conduction model. The forming voltage decreases with decreasing oxide layer thickness whereas it increases for the smaller device size. Due to overshoot phenomena during the electroforming process, these devices show a significant increased switching current, lower non-linearity, and lower endurance. The ReRAM device performance is improved by integration in the backend of a 65nm CMOS process. In the integrated 1T-1R stack, the electroforming is performed by controlling the current flow with the gate electrode. By employing this approach, the switching current in the ReRAM devices is reduced to 1  $\mu$ A. In order to lower the sneak path current in the passive crossbar arrays, a high degree of nonlinearity is required. This nonlinearity parameter has been investigated with 100 ns transient pulses in the nano-crossbar devices and in the 1T-1R structures. This parameter depends on the switching current and switching material properties. The lower switching current in the TiO<sub>2</sub> ReRAM leads to the higher nonlinearity.

Furthermore, the ReRAM nanodevices inherently exhibit open clamp voltage in the switching characteristics. This phenomenon is explained by the electromotive force (EMF). The amplitude of the generated EMF voltage depends on the nature of the switching materials and can be several hundred mV. This degrades the conducting filament and thereby limits the ON state retention properties of the ReRAM devices. Additionally, the non-zero crossing of the I-V characteristics, caused by the EMF voltage demands the refinement of the memristor theory.

## Kurzfassung

Der stetig wachsende Markt für Unterhaltungselektronik und die rasche Verbreitung von mobilen Geräten wie Tablet-Computer, MP3-Player und Smartphones stellen hohe Anforderungen an den verwendeten nichtflüchtigen Speicher. Aufgrund physikalischer Beschränkungen der aktuellen FLASH-Speichertechnologie, nähert sich die Skalierbarkeit dem Ende und daher muss eine alternative Technologie entwickelt werden. Für die Speichertechnologie spielt dabei nicht nur die Speicherdichte und die damit verbundenen Kosten eine wichtige Rolle, sondern vor allem auch die Leistungsaufnahme sowie die Schreib- und Lesegeschwindigkeit sind zu berücksichtigen. Redox-basierte Resistive Speicher (ReRAM) bieten eine mögliche Alternative zur FLASH-Technologie und stehen derzeit im Fokus der Forschungsaktivitäten. Das Funktionsprinzip des ReRAM beruht auf der nichtflüchtigen reversiblen Veränderung des Widerstandes einfacher Metall-Isolator-Metall Bauelemente durch elektrische Signale. Dieser einfache Aufbau ermöglicht den Einsatz in passiven Crossbar-Arrays, in denen jeder Kreuzungspunkt nur eine Fläche von 4F² (F-Strukturgröße) benötigt. Dies führt zu einer extrem hohen Speicherdichte bei reduzierten Kosten.

Die Erforschung von ReRAM Speicherelementen erfordert eine Technologie Plattform, welche eine kosteneffiziente Herstellung von Crossbar-Strukturen im nm-Bereich gewährleistet. In dieser Arbeit wurden Herstellungsprozesse basierend auf der Nanoimprint Lithographie entwickelt, welche sowohl die erforderlichen Auflösungen (<50 nm) als auch einen hohen Durchsatz bei geringen Kosten ermöglichen. Diese Verfahren ermöglichen die Untersuchung von ReRAM Elementen mit deutlich reduzierten Strukturgrößen von 40x40nm<sup>2</sup>. Sowohl der Einfluss der Oxidschichtdicke als auch der lateralen Ausmaße der Speicherelemente auf die elektrischen Eigenschaften wurden untersucht. Der im Allgemeinen benötigte Elektroformierschritt und die damit einhergehenden Schalteigenschaften wurden in dieser Arbeit systematisch für TiO2 und WO3 basierte ReRAM Zellen analysiert. Die Formierspannung skaliert mit der Oxidschichtdicke und erhöht sich bei reduzierten Zellgrößen. Das Uberschwingen der Schaltströme während des Elektroformierschritts von passiven Speicherelementen führt zu erhöhten Schaltströmen, niedrigen Nichtlinearitäten und geringen Lebensdauern. Die Eigenschaften des ReRAM wurden durch Integration in das Backend eines 65-nm-CMOS-Prozess verbessert. In den integrierten 1T-1R Elementen wird der Formierschritt durch die Regelung des Stromflusses mittels angelegter Gate-Spannungen gesteuert wodurch die Schaltströme des ReRAM auf 1 µA reduzieren lassen. Um parasitäre Ströme in passiven Crossbar-Arrays zu reduzieren ist ein hoher Grad an Nichtlinearität erforderlich. Dieser Parameter wurde mit 100 ns Spannungspulsen sowohl in Nanocrossbar als auch in 1T-1R Speicherelementen untersucht. Die Nichtlinearität hängt von den Schaltströmen und Materialeigenschaften des Oxids ab. Reduzierte Schaltströme in TiO<sub>2</sub> ReRAMs führen zu höheren Nichtlinearitäten.

Darüber hinaus weisen ReRAM Elemente von Natur aus offenen Klemmspannungen auf. Dieses Phänomen wird durch das Vorhandensein der elektromotorischen Kraft (EMK) erklärt. Die Amplitude der erzeugten EMK-Spannung hängt von den involvierten Materialien ab und kann mehrere hundert mV betragen. Dies degradiert das leitende Filament und begrenzt die Stabilität der eingeschriebenen Zustände der ReRAM Elemente. Die durch die EMK hervorgerufene Verschiebung der Hysteresekurven erfordert eine Anpassung der Memristor Theorie.

## Contents

| 1 | Inti | roduct  | ion        |                                                       | 1  |

|---|------|---------|------------|-------------------------------------------------------|----|

|   | 1.1  | Scope   | of this we | ork                                                   | 2  |

| 2 | Rec  | lox-Ba  | sed Resi   | stive Switching RAM                                   | 3  |

|   | 2.1  | Mecha   | anisms an  | d Materials                                           | 3  |

|   |      | 2.1.1   | Electroc   | hemical Metallization Memory                          | 6  |

|   |      | 2.1.2   | Valence    | Change Memory                                         | 8  |

|   | 2.2  | ReRA    | M Crossb   | ar-Array Integration                                  | 9  |

| 3 | Fab  | ricatio | on of ReI  | RAM Devices                                           | 15 |

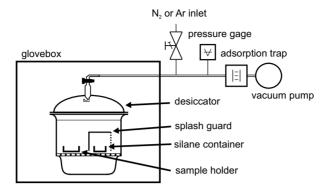

|   | 3.1  | Equip   | ment and   | Experimental Methods                                  | 15 |

|   |      | 3.1.1   | Thin Fil   | m Deposition Techniques                               | 15 |

|   |      |         | 3.1.1.1    | Sputter Deposition                                    | 15 |

|   |      |         | 3.1.1.2    | Thermal Evaporation                                   | 17 |

|   |      | 3.1.2   | Lithogra   | phy Methods                                           | 19 |

|   |      |         | 3.1.2.1    | Optical Lithography                                   | 19 |

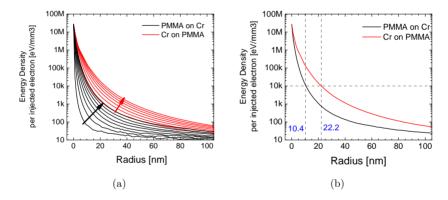

|   |      |         | 3.1.2.2    | Electron Beam Lithography                             | 22 |

|   |      |         | 3.1.2.3    | Nanoimprint Lithography                               | 27 |

|   |      | 3.1.3   | Etching    |                                                       | 30 |

|   |      |         | 3.1.3.1    | Wet Etching                                           | 30 |

|   |      |         | 3.1.3.2    | Dry Etching                                           | 31 |

|   |      | 3.1.4   | Physical   | Characterization Methods $\ \ldots \ \ldots \ \ldots$ | 33 |

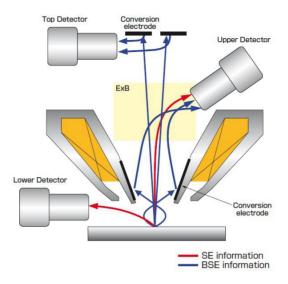

|   |      |         | 3.1.4.1    | Scanning Electron Microscopy                          | 33 |

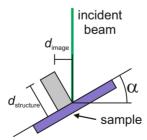

|   |      |         | 3.1.4.2    | Surface Profilometry                                  | 35 |

|   |      | 3.1.5   | Electrica  | al Characterization Setup                             | 36 |

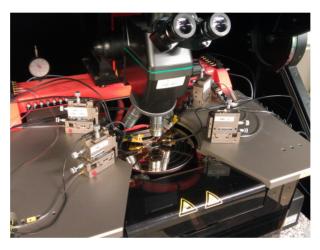

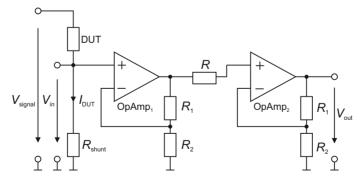

|   |      |         | 3.1.5.1    | Automated Quasi-Static IV-Characterization .          | 36 |

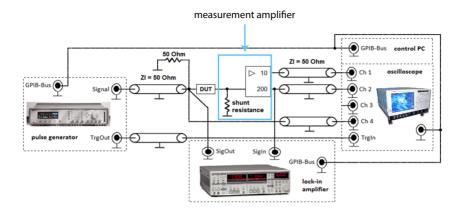

| 3.2                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.1.5.2 Voltage Pulse Measurement Setup                                                                                                                                                                                                                                                                                                                                                                                                                              | 37                                                       |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                   | Nano-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Crossbar Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                       |

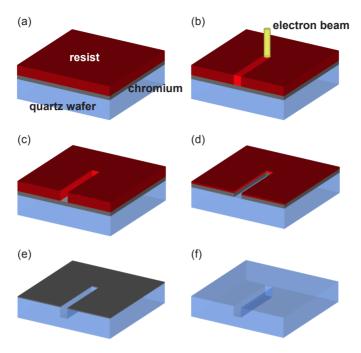

|                                   | 3.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Development of the Imprint Mold                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                       |

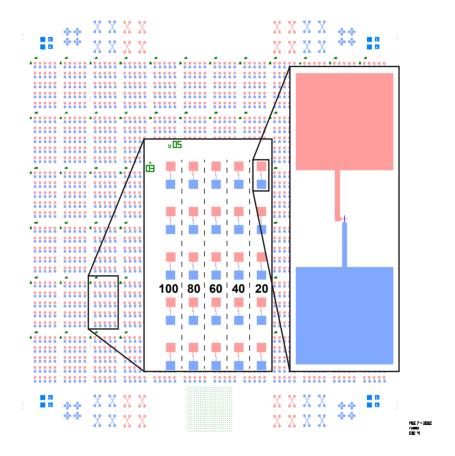

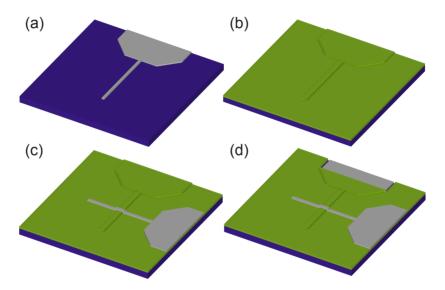

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.1.1 Mask Design                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                       |

|                                   | 3.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pattern Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                       |

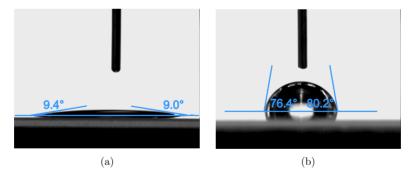

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2.1 UV-Nanoimprint Process                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                       |

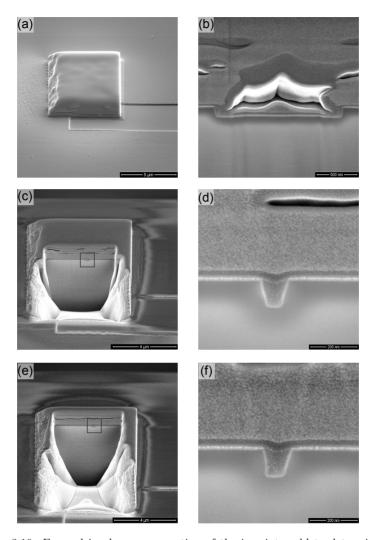

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2.2 Development of the Etch-Processes                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                       |

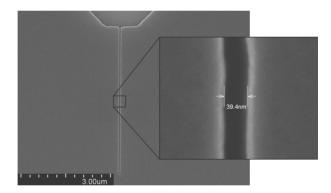

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2.3 Electrical Characteristics of the Nano-Electrodes                                                                                                                                                                                                                                                                                                                                                                                                            | 60                                                       |

|                                   | 3.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Top Electrode Patterning                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63                                                       |

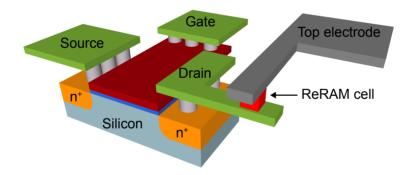

| 3.3                               | Integr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ation of ReRAM Devices with MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66                                                       |

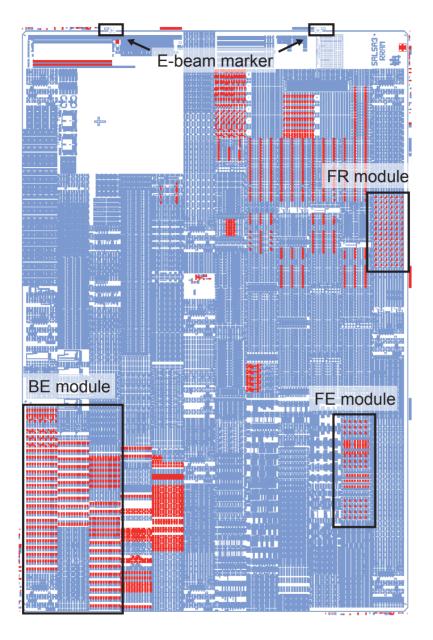

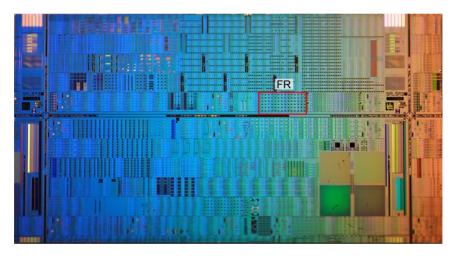

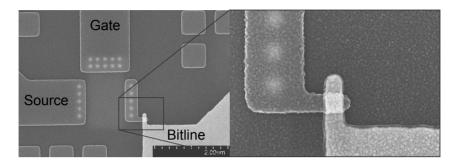

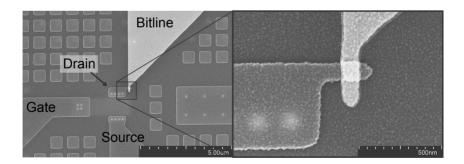

|                                   | 3.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mask Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                       |

|                                   | 3.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Development of the Process Flow                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69                                                       |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.2.1 Oxide Deposition                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                       |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.2.2 Top Electrode Patterning by E-Beam Lithog-                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | raphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71                                                       |

| 4 Ele                             | ectromo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | otive Force in ReRAM Devices                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77                                                       |

| 4.1                               | Theor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | y                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| 4.1                               | Theor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | y                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                                       |

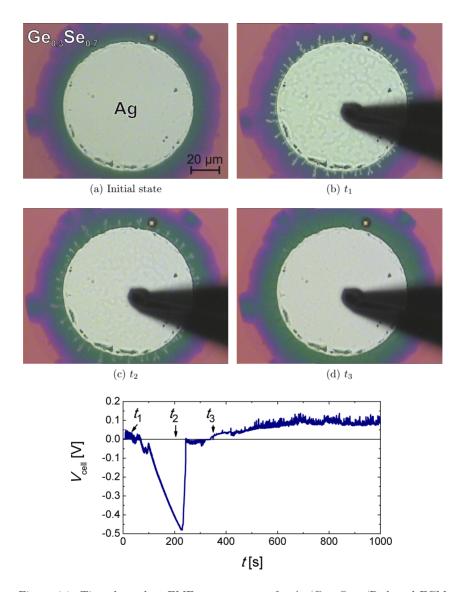

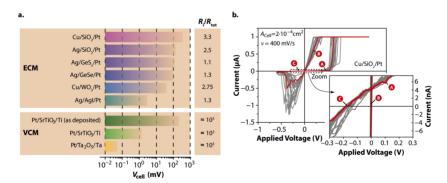

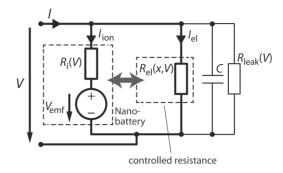

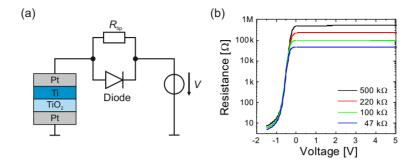

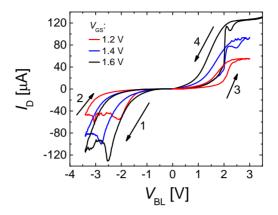

| 4.1                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                       |

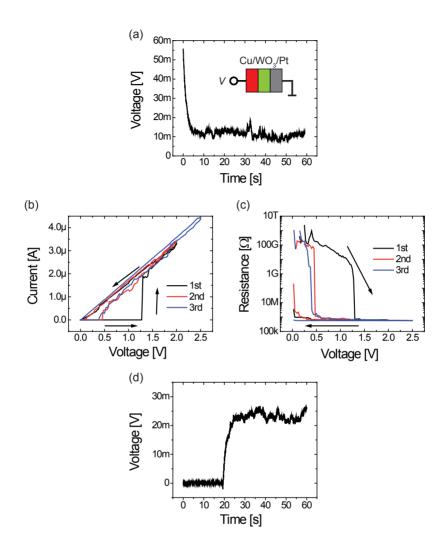

|                                   | EMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78                                                       |

| 4.2<br>4.3                        | EMF Impac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82                                                 |

| 4.2<br>4.3                        | EMF Impace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82<br><b>ts</b>                                    |

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82<br><b>ts</b><br>85                              |

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace Impac | in ECM Systems  t of the EMF on ReRAM Devices  Characterization of Nano-Crossbar Memory Elemen Based Nano-Crossbar ReRAM                                                                                                                                                                                                                                                                                                                                             | 78<br>82<br><b>ts</b><br>85                              |

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace Impac | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82<br><b>ts</b><br>85                              |

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace Impac | in ECM Systems  t of the EMF on ReRAM Devices  Characterization of Nano-Crossbar Memory Elemen Based Nano-Crossbar ReRAM  Electroforming Characteristics  5.1.1.1 TiO <sub>2</sub> Layer Thickness Dependence                                                                                                                                                                                                                                                        | 78<br>82<br><b>ts</b><br>85<br>86                        |

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace Impac | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82<br>85<br>86<br>88<br>88                         |

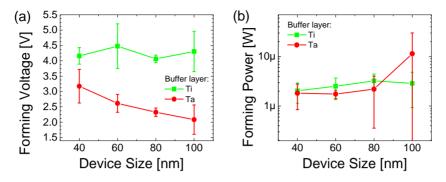

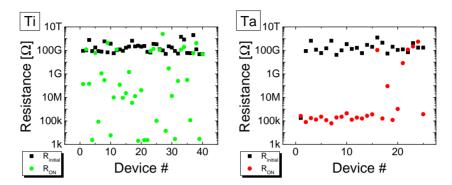

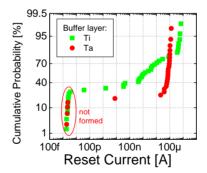

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impace Impac | in ECM Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78<br>82<br>85<br>86<br>88<br>89<br>91                   |

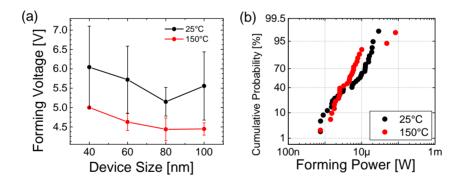

| 4.2<br>4.3<br><b>Ele</b>          | EMF Impacted | in ECM Systems  to of the EMF on ReRAM Devices  Characterization of Nano-Crossbar Memory Elemen Based Nano-Crossbar ReRAM  Electroforming Characteristics  5.1.1.1 TiO <sub>2</sub> Layer Thickness Dependence  5.1.1.2 Impact of the External Series Resistance  5.1.1.3 Influence of the Top Electrode Layer Material  5.1.1.4 Electroforming at Elevated Temperature                                                                                              | 78 82 85 86 88 89 91                                     |

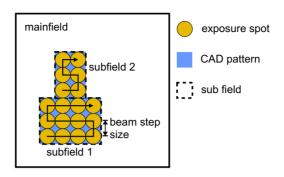

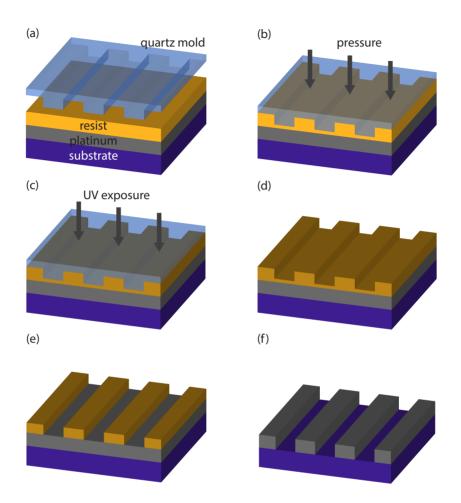

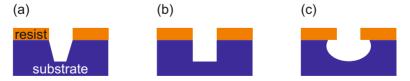

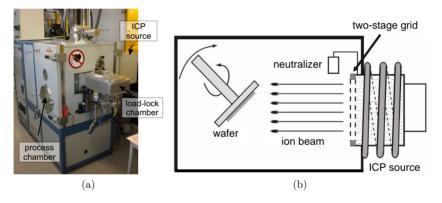

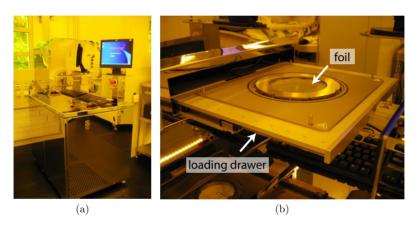

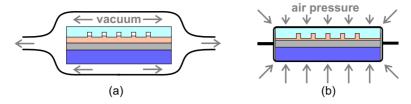

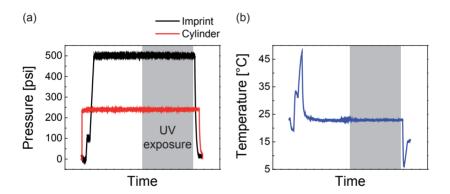

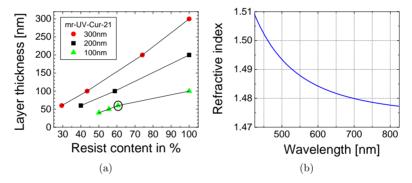

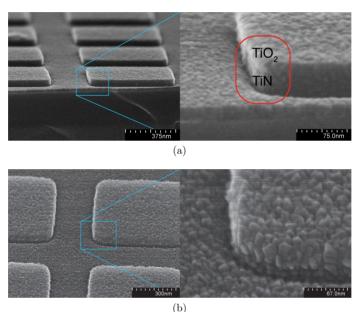

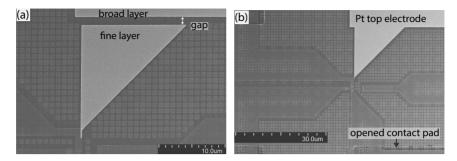

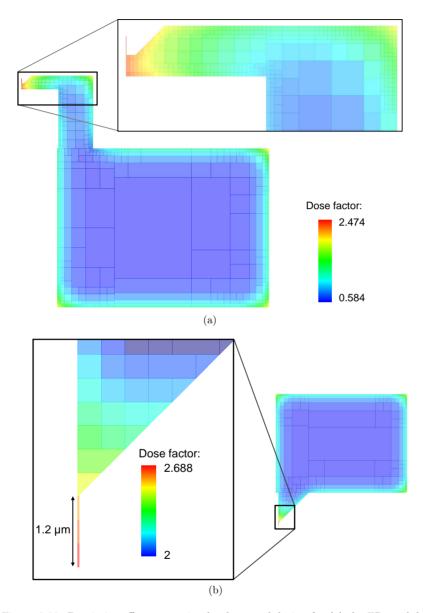

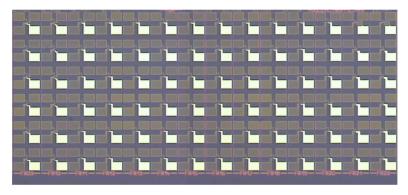

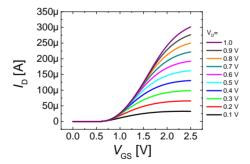

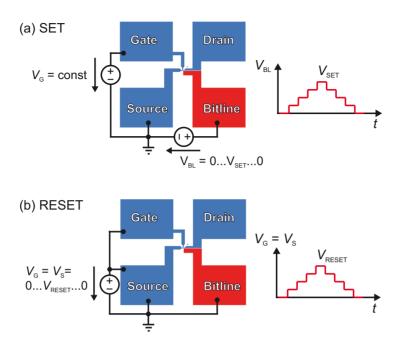

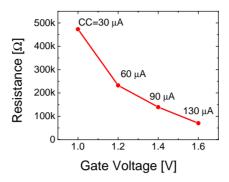

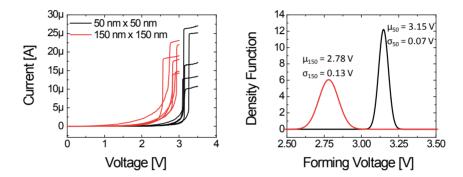

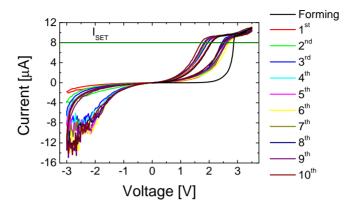

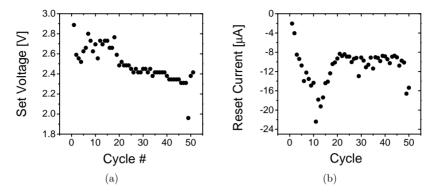

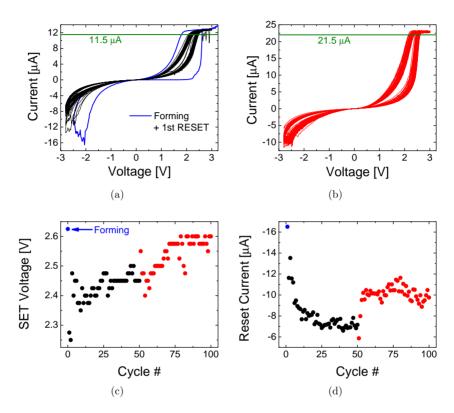

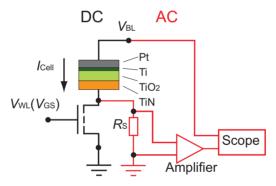

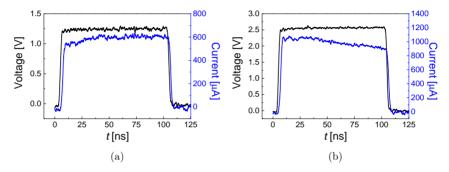

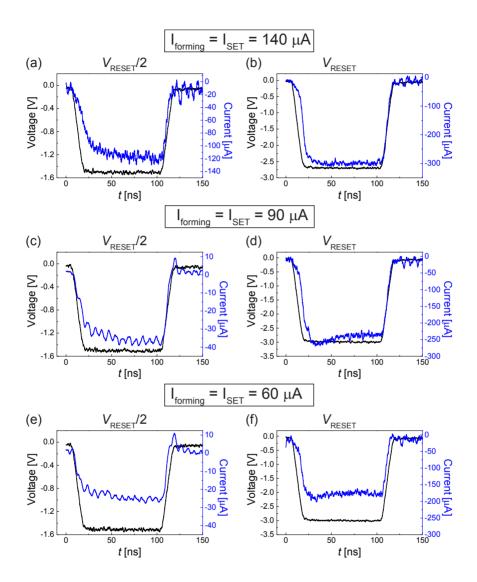

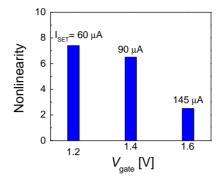

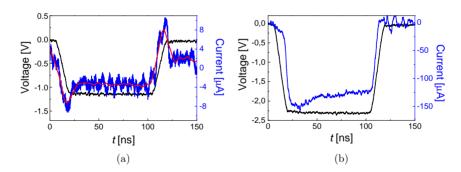

| 4.2<br>4.3<br><b>5 Elo</b><br>5.1 | EMF Impacted | in ECM Systems  t of the EMF on ReRAM Devices  Characterization of Nano-Crossbar Memory Elemen Based Nano-Crossbar ReRAM  Electroforming Characteristics  5.1.1.1 TiO <sub>2</sub> Layer Thickness Dependence  5.1.1.2 Impact of the External Series Resistance  5.1.1.3 Influence of the Top Electrode Layer Material  5.1.1.4 Electroforming at Elevated Temperature  Transient Pulse Characterization                                                             | 78 82 85 86 88 89 91 94                                  |