# Modeling and Realization of an Ultra-Short Channel MOSFET

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von Diplom-Physiker

JOACHIM KNOCH, GEB. GOEBBELS

aus Aachen

Berichter: Universitätsprofessor Dr. B. Lengeler

Universitätsprofessor Dr. H. Lüth

Tag der mündlichen Prüfing: 5.9.2001

## Contents

| 1 | Intr                                         | oducti                | ion                                                                | 1  |  |  |

|---|----------------------------------------------|-----------------------|--------------------------------------------------------------------|----|--|--|

| 2 | Principles of Operation                      |                       |                                                                    |    |  |  |

|   | 2.1                                          | 2.1 The MOS-Capacitor |                                                                    |    |  |  |

|   | 2.2                                          | Channel MOSFET        | 7                                                                  |    |  |  |

|   |                                              | 2.2.1                 | I-V Characteristics                                                | 9  |  |  |

|   |                                              | 2.2.2                 | Channel Length                                                     | 11 |  |  |

|   | 2.3 Short-Channel MOSFET                     |                       |                                                                    |    |  |  |

|   |                                              | 2.3.1                 | I-V Characteristics and Short-Channel Behavior $\ \ldots \ \ldots$ | 12 |  |  |

|   |                                              | 2.3.2                 | Scaling Laws                                                       | 15 |  |  |

|   |                                              | 2.3.3                 | Bulk versus SOI                                                    | 16 |  |  |

|   | 2.4                                          | The Io                | deal Transistor Structure                                          | 17 |  |  |

|   |                                              | 2.4.1                 | Ballistic Transport                                                | 17 |  |  |

|   |                                              | 2.4.2                 | Double-Gate MOSFET                                                 | 18 |  |  |

| 3 | The V-Groove MOSFET                          |                       |                                                                    |    |  |  |

|   | 3.1                                          | Device                | e Principles                                                       | 21 |  |  |

| 4 | Modeling of MOSFET Operation                 |                       |                                                                    |    |  |  |

|   | 4.1                                          | The M                 | Model                                                              | 25 |  |  |

|   |                                              | 4.1.1                 | Poisson's Equation                                                 | 26 |  |  |

|   |                                              | 4.1.2                 | Quantum Calculation                                                | 28 |  |  |

|   | 4.2 Simulations                              |                       |                                                                    | 32 |  |  |

|   |                                              | 4.2.1                 | A 30 nm Device                                                     | 33 |  |  |

|   |                                              | 4.2.2                 | Channel-Length Dependence                                          | 35 |  |  |

|   |                                              | 4.2.3                 | Going to the Limits                                                | 36 |  |  |

|   | 4.3                                          | Result                | ts                                                                 | 41 |  |  |

| 5 | Realization of an Ultra-Short Channel MOSFET |                       |                                                                    |    |  |  |

|   | 5.1                                          | The T                 | echnology                                                          | 43 |  |  |

ii CONTENTS

|              |                      | 5.1.1  | How to prepare a V-Groove?            | 43       |  |  |  |

|--------------|----------------------|--------|---------------------------------------|----------|--|--|--|

|              |                      | 5.1.2  | Mask Materials                        | 45       |  |  |  |

|              |                      | 5.1.3  | Etch Mask Definition                  | 47       |  |  |  |

|              |                      | 5.1.4  | Mask Geometry                         | 49       |  |  |  |

|              |                      | 5.1.5  | Gate Oxidation and Metal Gate         | 50       |  |  |  |

|              | 5.2                  | A Rea  | l Device                              | 52       |  |  |  |

|              |                      | 5.2.1  | The Material System                   | 52       |  |  |  |

|              |                      | 5.2.2  | Optical and Electron-Beam Lithography | 56       |  |  |  |

|              |                      | 5.2.3  | A Complete Device                     | 57       |  |  |  |

|              |                      | 5.2.4  | Deviations from the Ideal Behavior    | 58       |  |  |  |

|              | 5.3                  |        | o Align the Gate?                     |          |  |  |  |

|              | 5.4                  | Result | s                                     | 62       |  |  |  |

| 6            | Mea                  | asurem | ents and Results                      | 65       |  |  |  |

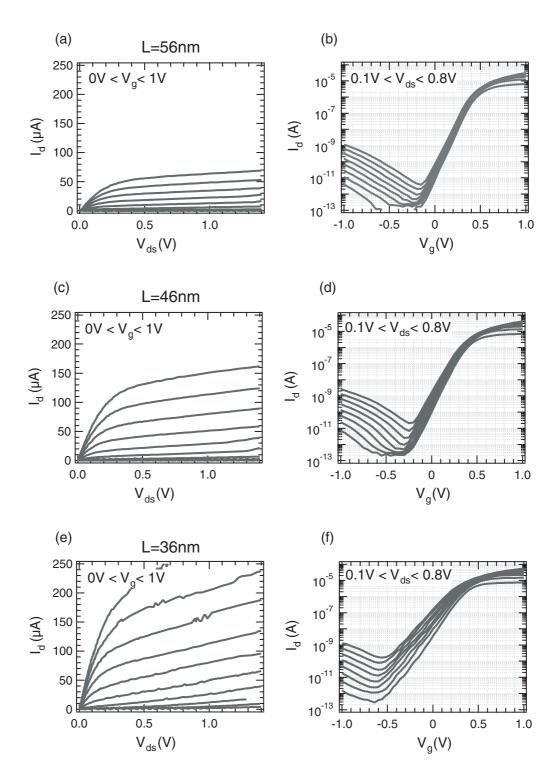

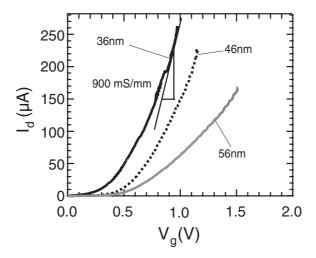

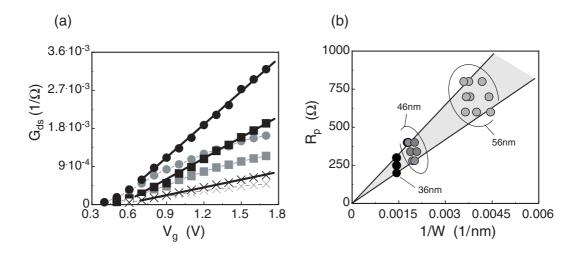

|              | 6.1                  | Room-  | Temperature                           | 66       |  |  |  |

|              |                      | 6.1.1  | I-V Characteristics                   | 66       |  |  |  |

|              |                      | 6.1.2  | Where are we?                         | 74       |  |  |  |

|              | 6.2                  | Low-T  | emperatures                           | 76       |  |  |  |

|              |                      | 6.2.1  | I-V Characteristics                   | 77       |  |  |  |

|              | 6.3                  | Result | s                                     | 80       |  |  |  |

| 7            | What Comes Next?     |        |                                       |          |  |  |  |

| $\mathbf{A}$ | Computational Issues |        |                                       |          |  |  |  |

|              | A.1                  | Noneq  | uilibrium Green's Function Formalism  | 83       |  |  |  |

|              | A.2                  | Numer  | rics                                  | 88       |  |  |  |

| В            | What Etches What?    |        |                                       |          |  |  |  |

| $\mathbf{C}$ | C Recipes            |        |                                       |          |  |  |  |

| D            | Don                  | narks  |                                       | 95       |  |  |  |

| ט            | D.1                  |        | rong Magle Coomatry                   | 95       |  |  |  |

|              |                      |        | rong Mask Geometry                    | 95<br>95 |  |  |  |

|              |                      |        |                                       | 97       |  |  |  |

| $\mathbf{E}$ | Used Chemicals       |        |                                       |          |  |  |  |

| Bi           | Bibliography         |        |                                       |          |  |  |  |

## 1 Introduction

In 1943 Thomas J. Watson - chairman of IBM at that time - stated the often quoted sentence 'I think there is a world market for maybe five computers'. That was in the time before the invention of the transistor based on semiconducting material. This sentence has continuously been proven wrong in the last three decades and today the semiconductor and computer industry is a prospering market with a volume of sales of 200 billion US \$.

For the last 30 years CMOS has been the predominant technology of microelectronics. The metal-oxide-semiconductor field-effect transistor (MOSFET) is at its heart and can nowadays be found millionfold in every computer chip. Over the years a tremendous down-scaling has been taken place resulting in a minimum feature size of 130 nm of today's semiconductor devices. The question arises: Why is scaling important? The answer is that scaling the geometry of the device and the supply voltage by a factor  $1/\kappa$  leads to a higher density of devices  $\propto \kappa^2$  and an increased speed  $\propto \kappa$  while leaving the power consumption constant. The ever increasing demand for higher speed and performance of microelectronic circuits has forced this enormous miniaturization. The remarkable commercial success of CMOS technology and the unique features of the Si/SiO<sub>2</sub> material system explain the enormous efforts of the semiconductor industry to push the limits to ever smaller structures whilst still the same principles of operation are used as at the beginning of the era of integrated circuits.

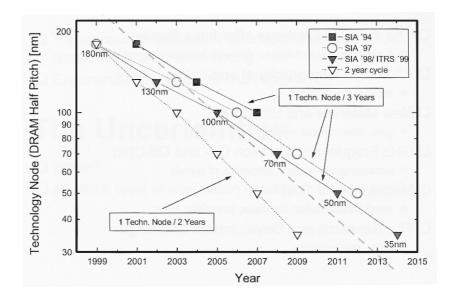

In 1965 G. Moore observed that integration of electronic circuits proceeds exponentially resulting in a doubling of components per chip every 18 months [48]. This so-called Moore's law still holds today and has led to the set up of technology roadmaps which are simple extrapolations of the development experienced so far. According to these roadmaps the limits of CMOS will be reached in the near future. Figure 1.1 shows a compilation of the International Technology Roadmaps for Semiconductors<sup>1</sup> for the years 1994 - 1999. As is predicted by the 1999 Technology Roadmap, the regime of 30 nm feature size is reached in 2015. To what extend CMOS can be further extrapolated and actually realized is quite unclear. A lot of theoretical and experimental research worldwide is dedicated to answer the question of 'how small can we go?'. Theoretical studies on the limits of CMOS have continuously proven wrong by experimentalists in recent years. Devices with channel lengths as short as 15 nm have already been demonstrated successfully [38] which exhibit acceptable electrical characteristics. In particular, the advent of silicon-on-insulator technology which will be the standard material for next generation devices makes a further miniaturiza-

<sup>&</sup>lt;sup>1</sup>http://www.semichips.org

2 1 INTRODUCTION

tion of today's devices possible [53]. Very recent simulations have shown that the limits of CMOS based on SOI technology are around channel lengths of 8 nm [50] for an ideal layout of the MOSFET structure.

For the realization of aggressively scaled devices there are two major obstacles. First, the technological difficulties, especially the nanometer-scale lithography, have to be overcome. Today, several different technologies are investigated which shall replace optical lithography in the near future. In particular, the use of extreme-UV, ion-beam and X-ray lithography are promising candidates. The second is a fundamental physical limit. There is a minimum structure size for which CMOS works. Beyond that, completely different concepts have to be employed. For ever smaller devices quantum mechanical effects will become increasingly important and will strongly influence the performance of MOSFETs.

Figure 1.1: Compilation of the 1994 - 1999 International Technology Roadmaps for Semi-conductors.

The present thesis studies ultra-short channel MOSFETs theoretically and experimentally. A fully quantum mechanical computer simulation of a quasi two-dimensional model for a single-gated ultra-short channel MOSFET has been developed. Simulations are performed in order to study the influence of the geometry of such devices on their electrical behavior. In addition, a technology for the fabrication of ultra-short channel MOSFETs with defined channel lengths is developed. Minimum channel lengths of 10 nm and below can be realized in principle what allows an investigation of the limits of CMOS technology. The key features of the present approach are the generation of an abrupt doping profile with the use of silicon epitaxy on SOI and the self-limited generation of source and drain with anisotropic wet chemical etching. This

results in two major advantages of the present device concept. First, ideally shallow source/drain contacts are achieved what is necessary to prevent short-channel effects. Second, a reproducible process technology is obtained due to the self-limiting behavior. In addition, because of anisotropically etching the device structure the technology is capable of fabricating source-drain separations in the nanometer regime with conventional optical lithography. Devices fabricated with this technology show state-of-the-art electrical characteristics.

The results presented here emerged out of a collaboration with the IBM T.J. Watson Research Center, USA, Massachusetts Institute of Technology, USA and the University of California at Los Angeles, USA.

4 1 INTRODUCTION

## 2 Principles of Operation

The present chapter gives an introduction to the most relevant topics and concepts of a metal-oxide-semiconductor field-effect transistor (MOSFET). Beginning with the metal-oxide-semiconductor capacitor, the MOSFET will be introduced in the following. First, a long-channel device is examined, then the peculiarities of short-channel devices will be introduced and discussed.

#### 2.1 The MOS-Capacitor

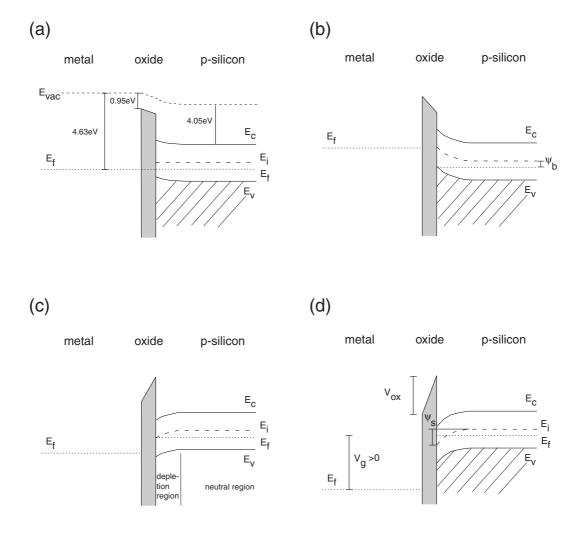

As its name reveals the MOS capacitor consists of three components, i.e. a metal, an insulator (oxide) and a semiconductor. In equilibrium, the edges of the conduction and valence bands are aligned according to the requirement of a common FERMI level throughout the structure. In addition, at interfaces between two components the exact position of the band edges is determined by the work-function of adjacent materials by the requirement of an equal energetic position of the vacuum level  $E_{vac}$  at the respective interface. This is illustrated in figure 2.1 (a) for the case of tungsten as metal electrode and a p-doped silicon substrate. Note, that the energetic position of the band edges is not drawn to scale.

In non-degenerately p-doped silicon the FERMI level  $E_f$  deep in the semiconductor side is determined by the doping concentration  $N_a$  and the temperature T according to [76]

$$E_i - E_f = kT \ln \left(\frac{N_a}{n_i}\right) \tag{2.1}$$

where  $n_i$  is the intrinsic carrier concentration and  $E_i$  can be considered as being the midpoint between valence and conduction band edge. The difference between the FERMI and the intrinsic level  $E_i$  is denoted  $\psi_b$  as is depicted in figure 2.1 (b) at the right end of the p-silicon. If the silicon is degenerately doped the FERMI level lies above the conduction band edge for n-type and below the valence band edge for p-type silicon.

If a voltage  $V_g$  is applied between the metal electrode and the semiconductor a potential  $\psi_s$  is present at the semiconductor-insulator interface which alters the charge distribution at the surface. In the depletion approximation the relation between  $V_g$  and  $\psi_s$  is [76]

$$V_g = V_{fb} + \psi_s + V_{ox} = V_{fb} + \psi_s + \frac{-Q_s}{C_{ox}} = V_{fb} + \psi_s + \frac{\sqrt{2\varepsilon_{si}eN_a\psi_s}}{C_{ox}}$$

(2.2)

Figure 2.1: The MOS capacitor. (a) in equilibrium, (b) accumulation, (c) onset of inversion, and (d) strong inversion.

where  $N_a$  is the density of acceptors and e is the elementary charge.  $V_{fb}$  is the so-called flat-band voltage explained below. For  $V_g \neq 0$  the following cases can be distinguished:

- In equilibrium the MOS system is determined by the requirement of a common Fermi level throughout the entire structure. The positions of the conduction band edges at the interfaces of the different materials are given by the differences in work function. The band-bending of the conduction and valence band of the semiconductor depends on the actual magnitude of the work-function of the metal.

- A negative voltage  $V_g$  accumulates holes at the oxide-semiconductor interface which are the majority carriers in the case of a p-silicon MOS capacitor. The MOS structure is said to be in accumulation.

- If in equilibrium the conduction and valence band edges of the p-silicon are bent a voltage applied between metal electrode and silicon can compensate this bending so that the case of flat band edges in the silicon is obtained. The corresponding voltage is called the flat-band voltage  $V_{fb}$  which can either be positive or negative depending on the work function of the gate electrode and the doping concentration in the silicon.

- If in the case considered in figure 2.1 a positive voltage larger than  $V_{fb}$  is applied the majority carriers in the p-doped region, i.e. the holes, will be repulsed from the surface. The resulting negative depletion charge of the immobile ionized acceptors will force the conduction and valence band to bend downwards. At the instant when  $E_i = E_f$  at the surface an equal occupation of electrons and holes results at the insulator-semiconductor interface. Increasing  $V_g$  yields a higher occupancy of electrons, i.e. the semiconductor is inverted in a small area at the interface. The onset of weak inversion is depicted in figure 2.1 (c). This means that at the surface a small area the inversion layer builds up consisting of bulk minority carriers, i.e. electrons in the case considered here.

- A further increase of gate voltage leads to the case of strong inversion which is shown in figure 2.1 (d). The Fermi-level lies well above the intrinsic level. The surface potential does not change any more when altering the gate voltage because the inversion charge will screen the electric field generated by the gate voltage. In the case of strong inversion all the voltage drops across the insulator and the MOS system behaves like a capacitor.

A criterion for the onset of strong inversion is  $\psi_s = 2\psi_b = 2(E_i - E_f)$ . The corresponding gate voltage  $V_g$  is called the threshold voltage  $V_{th}$  [76] which is given by equation (2.2) with  $\psi_s$  substituted by  $2\psi_b$  as

$$V_{th} = V_{fb} + 2\psi_b + \frac{\sqrt{4\varepsilon_{si}eN_a\psi_b}}{C_{ox}}.$$

(2.3)

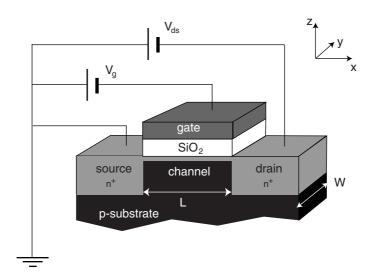

### 2.2 Long-Channel MOSFET

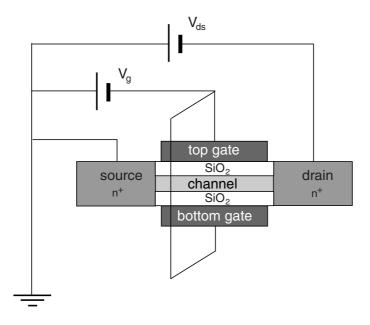

Attaching contacts to the right and to the left of the inversion layer one obtains a MOSFET structure a schematics of which is shown in figure 2.2. The device has three terminals, namely source, drain and gate and consists of two reversibly poled pn-junctions. All following considerations will exclusively be discussed for the case of an n-MOSFET, but can easily be transferred to the p-MOSFET. For an n-MOSFET the channel builds-up in the inversion layer of the p-doped part of the MOSFET which is in between the two n-doped contact regions. The channel is separated from the gate electrode by a thin  $SiO_2$  film. The channel length L is measured along the x-direction, the width W of the transistor in the y-direction. Additionally, the circuitry with the accessory voltages  $V_g$ , the gate voltage, and the drain-source voltage  $V_{ds}$  are shown in figure 2.2 as well.

Figure 2.2: Sketch of the MOSFET with a typical circuitry and the accessory voltages.

Usually, all voltages are measured with reference to the source contact which is connected to ground.

For gate voltages  $V_g \ll V_{th}$  the density of mobile carriers in the channel - i.e. electrons in the case of the n-MOSFET considered here - is exponentially small so that a drain current is prevented from flowing even when the drain-source bias  $V_{ds}$  is different from zero. Equivalently, one can consider the potential barrier generated by the two reversibly poled source-channel and channel-drain pn junctions. If this barrier is high enough no current flow is possible. In equilibrium, the barrier height is equal to the potential difference of the conduction band edges in e.g. source and the channel far away from the depletion zone of the pn junction. The resulting potential is called the built-in potential  $V_{bi}$  which is determined by the doping concentrations of the contacts and the channel. If a positive voltage is applied to the gate an inversion layer is generated connecting source and drain which is called the channel. A drain current  $I_d$  flows which can be controlled by the gate voltage.

In the case of the long-channel MOSFET the channel is much longer than the depletion zones of the pn junctions at the source and drain ends of the channel. Hence, in the case of a long-channel MOSFET these depletion zones can be neglected. The channel is so long that the potential distribution varies only slightly along the x-direction and the potential distribution can be regarded as one-dimensional. In this gradual-channel-approximation the behavior of the MOSFET is determined by the potential along the z-direction and the MOSFET can be described similar to the MOS capacitor.

#### 2.2.1 I-V Characteristics

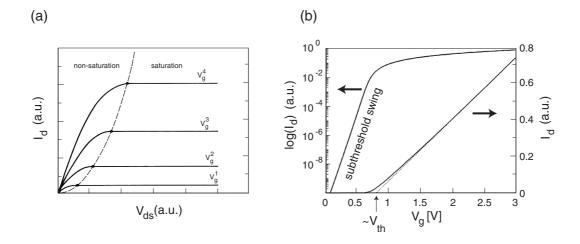

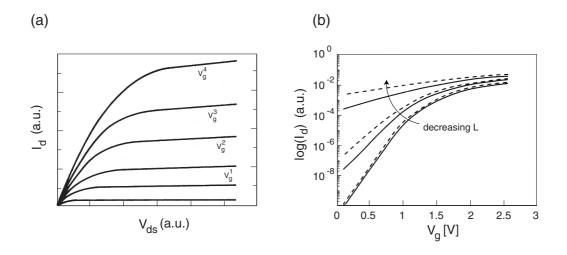

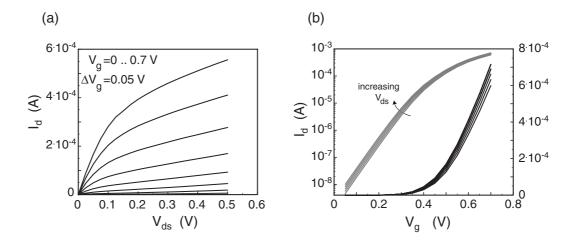

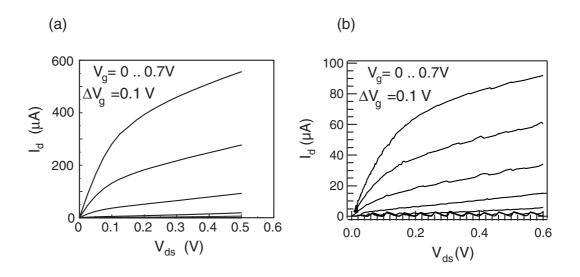

Figure 2.3 (a) shows a typical drain-current versus drain-source voltage plot of a long-channel MOSFET and (b) is a log-scale as well as a linear plot of the drain current  $I_d$  versus  $V_g$  for small drain-source voltages. Depending on  $V_g$  and  $V_{ds}$  one can distinguish between three different regions in the output characteristics:

- the subthreshold region: for  $V_g < V_{th}$  the drain current exponentially depends on  $V_g$  since only electrons with energies higher than the conduction band edge in the channel contribute to the current. The occupancy of these energy levels is only exponentially small no matter whether MAXWELL-BOLTZMANN or FERMI-statistics is encountered.

- the linear region: for small  $V_{ds}$  the MOSFET behaves like a resistor whose resistance depends on  $V_q$ .

- the saturation region: for high  $V_{ds}$  and  $V_g > V_{th}$  the drain current saturates. Its actual value solely depends on  $V_q$ .

The above listed modes of operation will now be discussed in more detail in the following paragraphs.

Figure 2.3: Output (a) and transfer (b) characteristics of a long-channel MOSFET.

#### **Subthreshold Behavior**

Below threshold the current is very small but not zero. In fact, it depends exponentially on the gate voltage. The left curve in figure 2.3 (b) shows a log-scale plot of the drain current versus gate voltage for small bias  $V_{ds}$ . The

straight line in the region below the threshold voltage is said to be the inverse subthreshold swing. It is defined as

$$S^{-1} = \frac{\partial \log I_d}{\partial V_q} \tag{2.4}$$

and indicates how the drain current alters when changing the gate voltage, i.e. it is a measure for the gate control of the device below threshold. Usually, the numerical value is given in mV/dec, i.e. how much gate voltage change is necessary in order to change  $I_d$  by one decade. Ideally, this change in gate voltage is given by  $\Delta V_g \approx kT \ln 10$  and has a numerical value of  $S=60\,\mathrm{mV/dec}$  at room temperature. The subthreshold behavior is important for digital applications since it determines how the device can be switched on and off. An acceptable ratio between on- and off-state current  $I_{on}/I_{off}$  is about 4 - 5 orders of magnitude for  $V_g$  given by the supply voltage and  $V_g=0$ , respectively. Since the supply voltage of future digital circuits must be reduced in order to diminish the power consumption S must not be larger than  $\sim 100\,\mathrm{mV/dec}$ . Otherwise no defined off-state is obtained any more.

#### The Linear Region

For small drain source voltage  $V_{ds}$  the drain current  $I_d$  can be given by the following relation [76]

$$I_d = \mu_{eff} C_{ox} \frac{W}{L} (V_g - V_{th}) V_{ds}$$

$$\tag{2.5}$$

where  $\mu_{eff}$  is the effective mobility of the conduction electrons and  $V_{th}$  is the threshold voltage. Equation (2.5) indicates that for small  $V_{ds}$  the MOSFET behaves like a resistor where the resistance  $R_{ds}(V_g) = V_{ds}/I_d$  can be modulated by the gate voltage. The linear region of  $I_d - V_{ds}$  curves can be seen in figure 2.3 (a) in the left part indexed 'non-saturation'.

More important for the extraction of device parameters is the  $I_d - V_g$  plot shown in figure 2.3 (b). Linear  $I_d - V_g$  plots (right curve in fig. 2.3 (b)) at low drain bias are used to approximately determine the threshold voltage and to extract the effective channel length of a MOSFET. The threshold voltage  $V_{th}$  can be determined from the  $I_d - V_g$  plot by linearly extrapolating the curve to  $I_d = 0$ . The intercept with the  $V_g$ -axis yields approximately  $V_{th}$  as is shown in figure 2.3 (b) by the dotted line.

#### **MOSFET** in Saturation

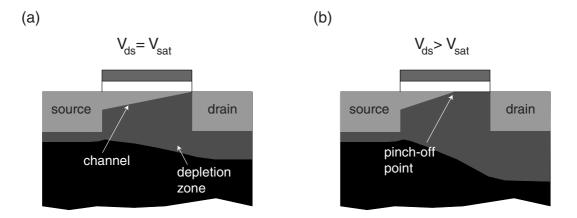

For increasing  $V_{ds}$  the drain current first raises linearly as stated above and reaches its maximum value at  $V_{ds}^{sat}$  which is shown by the dashed line in figure 2.3 (a). Current saturation occurs because at the drain end the inversion charge density vanishes if  $V_{ds}$  equals the gate overdrive  $V_g - V_{th}$ , i.e. the channel vanishes at the drain end which is termed pinch-off. Figure 2.4 (a) shows this

situation schematically. The saturation current depends on  $V_g$  as (dashed line in figure 2.3 (a))

$$I_d^{sat} = \mu_{eff} C_{ox} \frac{W}{L} \frac{(V_g - V_{th})^2}{2m}$$

(2.6)

with  $m = 1+3t_{ox}/W_{dm}$  being the body-effect coefficient and  $W_{dm}$  the maximum depletion layer width [76]. A further increase of  $V_{ds}$  beyond the saturation voltage leaves  $I_d$  unchanged whilst the pinch-off point moves towards the source as shown in figure 2.4 (b).

Figure 2.4: Current saturation in a MOSFET. (a) For  $V_{ds} = V_{sat}$  the channel vanishes at the drain end. (b) The pinch-off point moves to the source for  $V_{ds} > V_{sat}$ .

A plot of  $I_d$  versus  $V_g$  in the saturation region and for  $V_g \gg V_{th}$  yields the so-called transconductance  $g_m$  of the MOSFET defined according to

$$g_m = \frac{1}{W} \left. \frac{\partial I_d}{\partial V_g} \right|_{V_{ds} > V_{sat}, V_g \gg V_{th}}.$$

(2.7)

The transconductance is a measure of how effective the drain current in the on-state of the device is controlled by the gate voltage.

#### 2.2.2 Channel Length

The channel length is a key-parameter in CMOS technology since it is used for circuit simulations, short-channel design etc. However, the notion 'channel length' is not well-defined. There are quite a few length scales all related to the spatial extension of the channel. One distinguishes between the mask length  $L_{mask}$ , the gate length  $L_g$ , the metallurgical channel length  $L_{met}$  and the effective channel length  $L_{eff}$ . The difference between  $L_{mask}$  and  $L_g$  is simply due to an imperfect or deliberate deviation of the lithography mask pattern and the actual gate pattern. The metallurgical channel length denotes the separation

between source and drain, i.e. denotes the geometrical channel length. The effective channel length is different from the other lengths since it is defined by the electrical characteristics of the MOSFET and is no geometrical length.  $L_{eff}$  is a measure of how much gate-controlled current a device can deliver and is therefore an important length scale for circuit models. In general  $L_{eff}$  is different from  $L_{met}$  depending on the doping profile of source and drain. In lightly-doped-drain devices, for instance,  $L_{eff} > L_{met}$  whereas for abrupt doping profiles it can be significantly shorter than  $L_{met}$  [76]. There are several methods to extract the effective channel length from electrical characteristics [62]. For short channel MOSFETs the 'shift and ratio' method introduced by TAUR et al. is the most effective. This method compares the linear regime of the output characteristics of a long- and a short-channel device with equal width [74].

When devices get shorter and shorter it becomes increasingly difficult to exactly define the metallurgical channel length. As long as there is no abrupt doping profile the actual source-drain separation cannot be determined unambiguously since the annealing steps in the process flow of MOSFET fabrication will smear out the borders of implanted source/drain contacts due to diffusion of the dopants. Hence, when producing ultra-short channel MOSFETs diffusion of dopants can be a severe problem for the reproducibility of a certain technology.

#### 2.3 Short-Channel MOSFET

Although the transition from a long-channel to a short-channel MOSFET is a gradual one there exist qualitative and quantitative differences between them. For shrinking channel length the depletion zones at the source-channel and channel-drain contacts become more and more a part of the actual channel and their influence cannot be neglected any more. The resulting potential distribution is two-dimensional rather than one-dimensional. The proximity of source and drain thereby modifies the effective potential distribution and a number of so-called short-channel effects (SCE) appear which deteriorate the performance of the MOSFET. These effects are discussed in more detail in the following.

#### 2.3.1 I-V Characteristics and Short-Channel Behavior

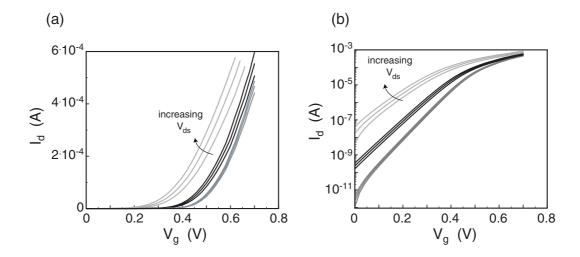

As already mentioned, the depletion zones of source and drain influence the electrical behavior of short-channel MOSFETs which manifests itself in the appearance of short-channel-effects. The short-channel effects come about because of an increasing loss of control of the depletion charge by the gate and an increasing influence by the drain. This can be seen in the output and transfer characteristics of such devices. The drain current of MOSFETs suffering from SCE does not saturate any more which is shown in figure 2.5 (a);  $I_d$  increases significantly even in the saturation region. Figure 2.5 (b) shows the transfer

characteristics of devices with decreasing channel length for two different  $V_{ds}$  (adjacent straight and dashed lines belong to one device). The loss of gate control manifests itself in an increasing subthreshold swing S which moreover depends on  $V_{ds}$ . Physically there is no distinction between different SCE since they are all due to the influence of the depletion zones of source and drain on the barrier height of the channel when L is reduced. However, according to the regime of operation a number of SCE are specified.

Figure 2.5: Output (a) and transfer (b) characteristics of a short-channel MOSFET. (b) shows curves with decreasing channel length for two different  $V_{ds}$ .

#### **Drain-Induced-Barrier-Lowering**

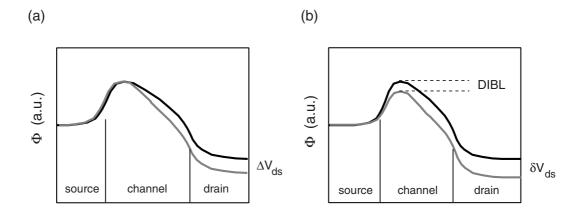

Due to the increasing extension of the drain depletion zone with increasing  $V_{ds}$  the barrier height at the edge of the source is lowered. This so-called drain-induced-barrier-lowering (DIBL) increases the carriers injected into the channel and the drain current raises in the saturation region. The situation is schematically shown in figure 2.6 contrasted to the situation in a device with long-channel behavior. The potential profile of the MOSFET is depicted for two different  $V_{ds}$ . For the long-channel device (a) the potential barrier at the source does not change under bias but depends on  $V_{ds}$  for the short-channel device (b). Therefore, the leakage current in the off-state of the device is increased with increasing bias. In the extreme case the device can be switched on under bias so that it cannot be used for digital applications because of the lack of a well defined on- and off-state. An equivalent approach to this phenomenon is that for a device suffering from SCE the depletion charge in the channel is influenced more and more by the drain electric fields as the channel length is decreased. This is referred to as charge sharing by the gate and drain electric fields.

Figure 2.6: Potential profile in a long-channel (a) and a short-channel (b) MOSFET for two different  $V_{ds}$  illustrating the appearance of DIBL in (b).

Due to the barrier lowering the threshold voltage becomes bias dependent so that a measure for the DIBL is the shift of the threshold voltage  $V_{th}$  per incremental change of the bias  $V_{ds}$ , usually given in units of mV/V.

$$DIBL = \left| \frac{\Delta V_{th}}{\Delta V_{ds}} \right| \tag{2.8}$$

Obviously, for an ideal long channel device the value of DIBL approaches zero.

Alternatively, looking at figure 2.6 (b) DIBL can be quantified by the ratio between the amount of barrier lowering indicated as 'DIBL' in the diagram per  $\delta V_{ds}$  for  $V_g \approx 0\,\mathrm{V}$ . This can certainly be done only for simulated curves where the potential profile is known. A practical way of extracting the DIBL is found by the observation that the barrier lowering essentially leads to a shift of the transfer characteristics to lower  $V_g$  [79]. A horizontal line is drawn in the transfer characteristics which crosses the curve for a medium  $V_{ds}$  at  $V_g \approx 0$ . The gate voltage interval where the horizontal line crosses transfer curves for higher and lower  $V_{ds}$  is then divided by the  $V_{ds}$ -interval of the belonging curves. This value represents the DIBL also specified as mV/V. However, this procedure results in higher numerical values (about a factor of 2) for the DIBL when compared to the direct relation possible for simulated curves.

#### Threshold-Voltage Roll-Off

As already mentioned above when L is of the order of the extension of the depletion zones in source and drain the potential barrier height is decreased depending on L. This results in a decrease of the threshold voltage compared to  $V_{th}$  of a long-channel device. This so-called threshold voltage roll-off is a severe problem in short-channel devices because manufacturing tolerances in the channel dimensions leads to significantly differing  $V_{th}$  from device to device

[80]. In addition,  $V_{th}$  must not be too small in order to get a defined off-state at  $V_g = 0 \,\mathrm{V}$ . In order to overcome this problem the influence of source and drain depletion zones have to be diminished which can be done by increasing the acceptor doping level in the channel or decreasing the source/drain contact depths (ultra-shallow contacts). As will be discussed below another way is to use very thin silicon-on-insulator (SOI) films with which the fraction of the gate controlled depletion charge is increased [15]. Furthermore, quantization in ultra-thin SOI films in the direction of the film thickness can enhance the effective potential barrier height thereby increasing the threshold voltage [54].

#### **Channel Length Modulation**

The effective channel length is reduced by the extensions of the depletion zones at the source-channel and channel-drain contact. For increasing  $V_{ds}$  the depletion zone at the drain end enlarges so that the effective channel length is diminished and becomes a function of  $V_{ds}$ . The channel-length modulation  $\Delta L$  is actually not a real short-channel effect since it also occurs in the long-channel MOSFET. But in the case of a long-channel device it can be neglected because  $L \gg \Delta L$ . However, in the case of a short channel the channel length modulation is of the order of L and influences the electrical behavior of the device. With increasing bias the channel gets shorter and shorter which leads to an increase of current in the saturation region. For high bias the depletion zones can get together which in the extreme case results in the so-called punch-through. A high drain current then flows in the MOSFET which cannot be affected by the gate any more.

#### 2.3.2 Scaling Laws

As mentioned above, when a MOSFET is scaled down the depletion width of source and drain have to be made small which can be done by increasing the doping concentration  $N_a$  in the channel. However, this increases the threshold voltage (see equation (2.3)) which in turn reduces the drivability of a MOSFET for given supply voltage. This in turn can be overcome by reducing the oxide thickness. Hence, scaling of a MOSFET is possible if certain rules are obeyed in order to avoid SCE and corruption of device performance. Dennard et al. were the first who put forward such scaling rules [21]. All spatial dimensions and potentials are scaled by a common factor  $1/\kappa$  and the doping concentration by  $\kappa$ . Since the electric fields in the scaled device remain the same as in the unscaled one this scaling rule is referred to as constant field scaling. The drawback of constant field scaling is that the diffusion potentials of the pn-junctions are not scaled so that the supply voltage cannot be scaled accordingly. Reducing the supply voltage is essential in highly integrated circuits in order to reduce the power consumption of the circuit [75] and to guarantee device reliability which is of concern due to increasing electric fields in the devices. Therefore, the scaling rules are generalized by the introduction of additional scaling factors in order to compensate the short-comings mentioned above. This approach is

called 'selective scaling' which has two spatial dimension scaling factors. One scales the gate length and the vertical dimensions of the device the other scales the width of the device as well as the wiring [20, 85]. However, the scaling rules loose their validity for channel lengths in the nanometer regime. Even for the highest doping levels there are only a few dopants in the channel which lead to fluctuating electrical behavior from device to device disabling digital applications [87]. Hence, for ultimately scaled devices doping of the channel cannot be tolerated. A special device layout must be employed in this case in order to prevent the SCE from making the device inoperative.

#### 2.3.3 Bulk versus SOI

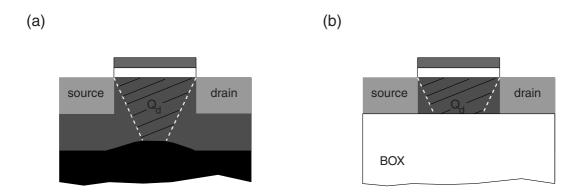

Instead of working with a usual silicon substrate the efforts nowadays aim at using silicon-on-insulator (SOI) technology. SOI offers advantages not only in the direct dielectric isolation of adjacent devices being part of a circuit on a chip but also for the actual device itself. This is due to the unique feature of having a silicon film of varying thickness  $t_{si}$  on  $SiO_2$ , called the buried oxide (BOX). Short-channel effects are strongly reduced in SOI-based MOSFETs. Additionally, the presence of the buried oxide reduces parasitic capacitances of the device such as the junction-to-substrate capacitance [15] which increases the response speed of such transistors.

The electrical behavior of a MOSFET fabricated on the basis of SOI technology depends strongly on the thickness  $t_{si}$  [15]. For thick films ( $\geq 300 \,\mathrm{nm}$ ) the devices are very much like bulk MOSFETs. Reducing  $t_{si}$  results in a thin film device with superior output characteristics and short-channel behavior for scaled-down devices [15, 81]. In particular, the fully-depleted (FD) SOI MOS-FET is the most promising version of possible SOI devices. Fully-depleted means that  $t_{si}$  is smaller than the depletion length at threshold. When scaling MOSFETs down the depletion charge controlled by the gate decreases with decreasing device dimensions which leads to DIBL resulting in the threshold voltage roll-off and eventually in a punch-through. SOI devices on the other hand are much less vulnerable to short-channel effects. This can be understood with a simple geometrical construction [15, 81]. The charge controlled by the gate can be estimated by a trapezoidal region underneath the gate with the upper base given by the gate length and the lower reduced due to the influence of source and drain. If the channel length is scaled down the lower base reduces until it vanishes. If this happens most of the depletion charge is not controlled by the gate anymore but by source and drain and the device suffers from short-channel effects. This scenario is depicted in figure 2.7 (a) for a bulk MOSFET. The depletion region is shaded dark-gray and the part of the depletion charge controlled by the gate is the hatched area. Using SOI as shown in figure 2.7 (b), the relative amount of the gate-controlled depletion charge can be increased. This amount is maintained if the silicon film thickness is reduced accordingly when scaling the channel length down [72]. Therefore, the DIBL and the threshold-voltage roll-off in these devices is much smaller and starts at much smaller channel lengths than in bulk devices [81, 72] which is due to the more efficient gate control of the depletion charge and the automatic ultra-shallow source/drain contacts.

Figure 2.7: Bulk (a) versus SOI (b). The dark-gray shaded region is the total depletion charge whereas the hatched area is the depletion charge  $Q_d$  controlled by the gate [15].

If the SOI film thickness is further reduced quantum mechanical effects become important so that the quasi-continuum of two-dimensional subbands in the channel splits up into energetically separated levels [44]. Quantization plays an important role in very thin film SOI devices because the electron wave-function is confined to the SOI film by the two SiO<sub>2</sub>-potential barriers represented by the gate oxide and the BOX [35]. In particular the first two-dimensional subband in the channel can be energetically well separated from the conduction band edge which significantly enhances the effective barrier height between source and drain [14, 23]. Since the first subband belongs to the ladder with high effective mass [5] in vertical direction quantization is of concern only for very thin  $t_{si}$ [44]. For ultra-short channel MOSFETs with undoped channel (see below) the increase in barrier height is important in order to avoid punch-through in these devices. However, quantization can degrade the performance of MOSFETs due to a reduction of the density of states in the channel and therefore a reduction of the inversion charge. Furthermore, the charge centroid is moved away from the Si/SiO<sub>2</sub> interface which results in a reduction of inversion capacitance. In addition, the threshold voltage increases due to the quantization [54] so that for low supply voltage the gate overdrive  $V_g - V_{th}$  is reduced. This results in a performance loss concerning the drivability of the device if the SOI thickness is smaller than  $\sim 3 \, \mathrm{nm}$  [12].

#### 2.4 The Ideal Transistor Structure

#### 2.4.1 Ballistic Transport

If the channel length is reduced to lengths in the range of 10-20 nm even for the highest doping levels there is only a small number of dopants in the channel

and every device will have its own specific spatial dopant configuration. This results in a fluctuation of threshold voltage from device to device which severely limits the applicability of MOSFETs in circuits [87, 46]. Increasing the width of the devices is no remedy for  $V_{th}$  fluctuations since in the subthreshold regime the current appears to be highly localized to the area of lowest potential barrier which can be different from device to device [12]. Therefore, one has to avoid doping in the channel and a special design is necessary to prevent the short-channel effects from deteriorating the performance of the transistor.

If the channel is undoped it was shown theoretically that the total mean free path of carriers in the channel limited by electron-electron and electron phonon-interaction [24] is such that ballistic transport, i.e. transport without scattering is possible for channel lengths smaller than  $30\,\mathrm{nm}$  [28]. Since lowering the temperature suppresses both interaction processes ballistic transport is predicted at  $77\,\mathrm{K}$  for  $L \leq 50\,\mathrm{nm}$  [49]. Ballistic transport is favorable since the highest transconductances are anticipated for these devices.

Although electrons in ballistic MOSFETs move dissipationless the resistance of the MOSFET is not zero. There is a fundamental contact resistance which cannot be lowered no matter what contact metallurgy is employed [19, 8]. This resistance is due to the fact that the current inside the contacts is carried by infinitely many transverse modes (i.e. along the width of the device) whereas in the channel there are only a finite number of modes accessible [17]. This contact resistance is approximately  $R_c = 12.9 \,\mathrm{k}\Omega/M$  with M being the number of transverse modes in the channel.

The consideration of current saturation in ballistic MOSFETs is different from the notion of pinch-off in long-channel MOSFETs. The drain current  $I_d$  can be written as [49]

$$I_d \propto \int dE \left( f_s - f_d \right) T(E)$$

(2.9)

where T(E) is transmission coefficient of electrons moving from source to drain. When direct tunneling between source and drain is neglected  $T(E) \approx 1$  for energies above the potential barrier maximum  $E_{pot}^{max}$  represented by the source-channel pn-junction. In equilibrium both occupation factors are equal and cancel each other. For high bias  $f_d$  vanishes in the energy range for which  $T(E) \neq 0$  and a net current flows which is given by the factor  $f_s$  for  $E \geq E_{pot}^{max}$ . Hence, if tunneling between source and drain can be neglected transport in ballistic MOSFETs is determined by the thermionic emission over the potential barrier generated by the two reversibly poled source-channel and channel-drain pn junctions.

#### 2.4.2 Double-Gate MOSFET

There appears to be a consensus about the optimal design of an ultra-short channel device [75, 85] which is the double-gated MOSFET on SOI. Many theoretical studies have revealed its superior electrical characteristics [84, 50].

The two gates effectively terminate the drain electric field lines which results in an efficient suppression of short-channel effects [75]. There is an abrupt doping profile between contacts and the channel. The device structure of the double-gated MOSFET is depicted in figure 2.8. It consists of a very thin silicon film provided with top and back gate separated by very thin gate-oxides from the channel. Source and drain are degenerately doped ( $\sim 10^{20} \, \mathrm{cm}^{-3}$ ) in order to keep the depletion zones and series resistances of the contacts as small as possible. The silicon thickness of the SOI film  $t_{si}$  is in the nanometer range. The reason for the superior short-channel behavior of the double-gated SOI MOSFET is the good control of the inversion charge by the gates. In addition, ideal ultra-shallow contacts are obtained automatically due to the geometry of the double-gate design [72].

As a rule of thumb for designing such a device, the ratio between gate length and silicon film thickness should not be smaller than about four in order to avoid punch-through [86]. Theoretical investigations of ultimately scaled double-

Figure 2.8: Ideal short-channel transistor structure. An ultra-thin undoped silicon layer is provided with top- and bottom-gate. Source and drain are degenerately doped with an abrupt doping profile between channel and contacts.

gated MOSFETs prognose functioning devices with channel lengths down to  $8\,\mathrm{nm}$  for an SOI thickness of  $2\,\mathrm{nm}$  and oxide thickness of  $1\ldots1.5\,\mathrm{nm}$  [50]. Large transconductances up to  $4000\,\mathrm{mS/mm}$  are predicted.

However, such double-gated MOSFETs are very difficult to realize since both gates have to be fabricated aligned to each other, surrounding a silicon layer only a few nanometer in thickness.

## 3 The V-Groove MOSFET

In recent years there have been proposed and realized many different concepts for the fabrication of an ultra-short-channel MOSFET [34, 36, 37, 77]. Channel lengths in the range of 30 nm down to 15 nm have been reported in the literature [13, 33, 38, 83]. With the use of electrically variable shallow source/drain junctions a MOSFET with 8 nm gate length has even been successfully fabricated [36]. However, this device needs two different gates in order to control the channel and the leads separately and suffers from very high source/drain series resistances. Most of the device concepts rely on the use of thin film SOI material with its advantages for scaled-down transistors. In general, there are two different strategies which are pursued namely the lateral MOSFET as is usually done in today's fabrication processes and the vertical MOSFET where the MOS structure is tilted at an angle of 90°. Both approaches have their specific advantages. In the case of a vertical MOSFET the active channel area can be realized, for instance, with molecular beam epitaxy (MBE) so that very short channels with atomic precision can in principle be fabricated [47]. Furthermore, a double-gated MOSFET can be realized much more easily than in the case of the lateral structure. On the other hand, vertical MOSFETs are difficult to fabricate since the technology is rather involved and requires many process steps [47, 33]. A lateral MOSFET layout on SOI offers the ability to achieve very thin channel regions which allows to reduce the short-channel effects and to exploit the vertical quantization in order to enhance the potential barrier of the channel [14, 63]. Additionally, with the use of very thin SOI films ultra-shallow source/drain contacts are automatically achieved [72].

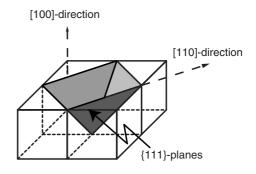

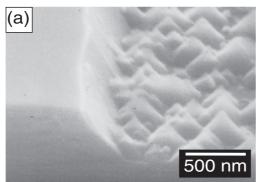

In the present chapter a concept for the realization of an ultra-short-channel MOSFET on SOI with lateral layout is introduced and discussed. The concept relies on a combination of silicon epitaxy and a self-limited etch process which defines the channel region and separates source and drain. The device layout has some major advantages which allow the fabrication of MOSFETs with well-defined channel lengths in the 10 nm regime.

#### 3.1 Device Principles

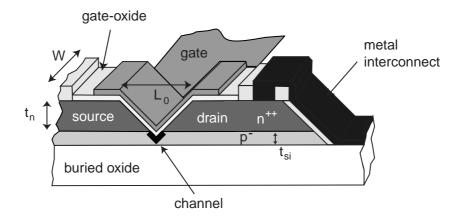

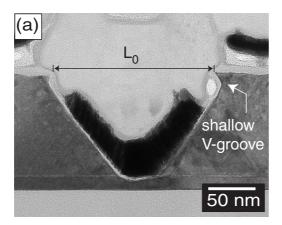

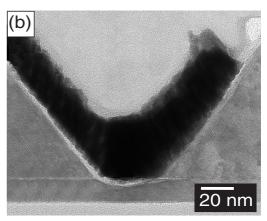

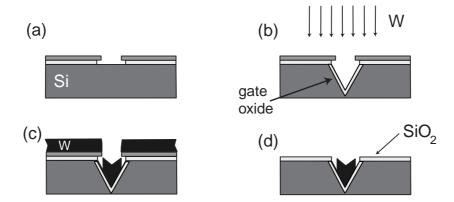

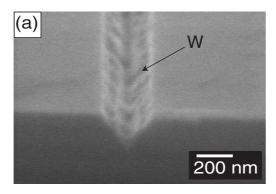

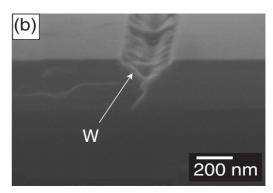

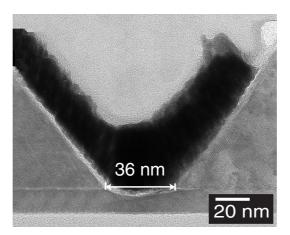

Figure 3.1 shows a schematic cross section of the device idea. A highly Sb doped  $n^{++}$  silicon layer (thickness  $t_n$ ) is epitaxially grown on a thin, undoped  $p^-$  silicon film of thickness  $t_{si}$  being part of a silicon-on-insulator (SOI) wafer. An appropriate etch anisotropically etches a 'V' shaped groove with opening  $L_0$  into the  $n^{++}$  layer with the tip of the 'V' just touching the  $p^-$  region. The

separated  $n^{++}$  areas serve as source and drain and the channel forms in the  $p^-$  in between source and drain, i. e. in the tip region of the V-groove. A thin gate oxide separates the channel as well as the  $n^{++}$  regions from a metal gate electrode. Except in the V-groove region the anisotropic etch cuts through the whole  $n^{++}/p^-$ -stack and isolates adjacent devices from each other. Metal

Figure 3.1: Sketch of the device geometry showing the V-groove obtained with anisotropic etching of an epitaxial silicon stack. The channel is located between the highly doped  $n^{++}$  regions.

interconnects are used in order to contact the devices. The advantages of this specific layout are the following:

- With the use of silicon epitaxy an abrupt doping profile is achieved. No implantation technique is necessary and the borders of the source and drain contacts are sharply defined by the geometry of the V-groove. Hence, a well-defined source-drain separation is obtained. The expression 'channel length' and 'source-drain separation' can therefore be used synonymically, referred to as L throughout the next chapters. Note, that raising source and drain on top of the channel layer with an abrupt doping profile is actually the optimal way of generating ultra-shallow contacts which is important in order to suppress SCE. Additionally, due to the high doping level the parasitic series resistance of source and drain is kept as small as possible.

- The channel layer is nominally undoped. This is necessary since for very small channel lengths the distinct configuration of dopant atoms influence the electrical behavior of the devices as already discussed in the previous chapter. Additionally, the p<sup>-</sup> layer is made thin in order to reduce shortchannel effects.

- Because the V-groove tapers off towards the channel a very short channel in the nanometer regime can be defined in the tip region of the groove by a much larger mask at its opening  $L_0$ . The required mask opening

$L_0$  is given by the geometry of the V-groove and depends only on the thickness  $t_n$  of the  $n^{++}$  layer. Hence, by choosing an appropriate  $t_n$  the V-groove process can be adjusted to any desired lithographic technique. As is shown in chapter 5, source-drain separations as short as 10 nm can be achieved with the present approach.

- The device layout inherently brings about a control of having fabricated a MOSFET with ultra-short channel. If the thickness of the SOI film is very thin only ultra-short-channel transistors can be obtained, because in case of the V-groove opening  $L_0$  being too large the tip of the 'V' cuts through the  $p^-$  layer and no transistor action is possible. Thus, the geometry of the device gives an upper cut-off for possible channel lengths which is given by the relation  $L_{max} = 2t_{Si}/\tan(\alpha)$ . On the other hand, if  $L_0$  is too small the V-groove does not cut through the entire  $n^{++}$  stack and source and drain will be shortened. Again, no transistor action is possible.

- A metal gate is chosen with the advantage that there is no depletion zone

in the gate as it happens to be for poly-silicon and that a metal gate has

a much lesser electrical resistance which is important for high frequency

applications.

The present approach is attractive due to its conceptual simplicity. There are a lot of technological problems to be solved, though, which are set forth in chapter 5. Obviously, the generation of a proper V-groove is of central interest in the device concept. A self-limited, anisotropic etch procedure has to be developed in order to establish a reproducible and reliable technology.

# 4 Modeling of MOSFET Operation

Before going on to the realization of the proposed device concept, simulations of single-gated short-channel MOSFET on SOI will be performed in order to get information about the electrical behavior of such devices. Classical calculations have often failed to predict the electrical characteristics of ultimately scaled MOSFETs since quantum mechanical effects like the shift in  $V_{th}$  for ultrathin  $t_{si}$  play an important role for such devices. Therefore, a quantum mechanical simulation has been developed and will be presented here. Many publications dealing with the quantum mechanical simulation of ultra-small MOSFETs can be found in the literature. However, most of these papers incorporate only some quantum mechanical aspects in their simulations. For instance, either the enhancement of the effective barrier height in the channel due to vertical quantization [56] is considered or merely a 1D model perpendicular to the current flow is employed in order to describe the tunneling current from the gate to the channel [66, 30, 43]. Other works compute the 2D electron and current distributions relying on quasi-classical methods but neglect tunneling through the gate [50] or abandon self-consistency between the quantum and Poisson equations [49].

In this chapter a quasi two-dimensional model for an ultra-short-channel MOSFET is introduced and analyzed which fills the gap between the work mentioned above in that it combines a full quantum mechanical treatment of carrier transport with gate leakage in a self-consistent manner. The potential distribution in the direction of current flow will be reduced to a 1D problem making simulations using the non-equilibrium Green's function technique [18, 42, 16] feasible. Vertical quantization is taken into account through an effective barrier height in the channel. The use of the non-equilibrium Green's function formalism enables among other things the correct treatment of open boundaries for a finite computational domain which otherwise is often terminated by artificial boundary conditions [67, 71].

#### 4.1 The Model

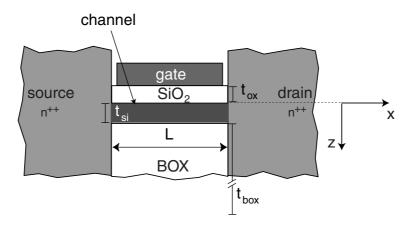

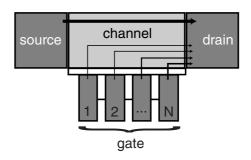

The device concept introduced in the previous chapter is a single-gated, fully-depleted MOSFET on SOI. Therefore, the model under investigation is chosen accordingly. In order to simplify the calculations the model is somewhat modified which is depicted in figure 4.1. A thin SOI film of thickness  $t_{si}$  serves as

channel of length L which is connected to semi-infinite source and drain contacts. The thickness  $t_{box}$  of the buried oxide is considered as being very large. The channel is assumed to be undoped whereas source and drain are degenerately doped with dopant concentration on the order of some  $N_d \approx 10^{20} \, \mathrm{cm}^{-3}$ . All dopants are fully ionized, i.e. they constitute a constant, positive background, called the jellium. The channel is seperated from a metal gate by a thin gate oxide (thickness  $t_{ox}$ ), typically a few nanometer in thickness. Any influence of the gate on the  $n^{++}$  contacts is neglected. The width W of the device

Figure 4.1: Model of the single-gated short-channel MOSFET on SOI used for the simulations. The channel length is aligned along the x-, the width along the y-direction.

is directed along the y-direction and is taken large enough so that the assumption of translational invariance along y is justified. As is shown in figure 4.1, x is directed along the channel length and z along the vertical direction, i.e. the SOI film thickness. Following Young [90, 89], the original two-dimensional potential distribution is reduced to an essentially one-dimensional one as stated in the next section.

#### 4.1.1 Poisson's Equation

The potential distribution in the MOSFET is governed by a two-dimensional Poisson equation of the form

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial z^2}\right)\Phi(x, z) = \frac{\rho(x, z)}{\varepsilon_{si}}.$$

(4.1)

In order to reduce the simulation problem to a one-dimensional calculation the so-called parabolic approximation for the potential distribution  $\Phi(x, z)$  is made [88, 89, 90]

$$\Phi(x,z) \approx c_0(x) + c_1(x)z + c_2(x)z^2 \tag{4.2}$$

Equation (4.2) needs three boundary conditions in the vertical direction to be fulfilled in order to specify the 'constants'  $c_i(i = 0..2)$  although there exist four

4.1 THE MODEL 27

conditions namely the potential and electric field at both  $\mathrm{Si/SiO_2}$  and  $\mathrm{Si/BOX}$  interfaces. According to reference [88] the exact value of the potential at the  $\mathrm{Si/BOX}$  interface does not need to be specified since the potential essentially floats at this interface. It is assumed that the buried oxide is so thick that a finite potential difference across the BOX leads to a negligible field at the  $\mathrm{Si/BOX}$  interface. Hence, the following boundary conditions determine the potential distribution in z-direction

- $\Phi(x,0) \equiv \Phi_f(x) = c_0(x)$ , where  $\Phi_f$  is called the surface potential

- the electric field at z=0 is determined by the gate voltage  $V_q$

$$\frac{d\Phi(x,z)}{dz}\bigg|_{z=0} = \frac{\epsilon_{ox}}{\epsilon_{si}} \frac{\Phi_f(x) - V_g + V_{bi}}{t_{ox}} = c_1(x)$$

(4.3)

with  $V_{bi}$  being the built-in potential. In the case of an undoped channel  $V_{bi}$  is given by  $\Delta_{si}/2 + E_f$  where  $\Delta_{si}$  is the energy gap of silicon and  $E_f$  is the FERMI energy relative to the conduction band edge deep inside the source/drain contact. Hence,  $V_{bi}$  is the maximum possible potential barrier height between source and drain. Doping the channel with acceptors would raise  $V_{bi}$  but is not considered here due to reasons mentioned in chapter 2. Furthermore, we have assumed a midgap workfunction gate metal such as tungsten so that  $V_{fb} = 0$  for an undoped channel. However, using a metal gate with different work function yields an  $V_{fb} \neq 0$  which would have to be added to  $V_{bi}$  in equation (4.3). The effect would simply be a shift in  $V_{th}$ .

• at the interface to the buried oxide the electric field is approximately zero for large  $t_{box}$

$$\left. \frac{\Phi(x,z)}{dz} \right|_{z=t_{si}} = \frac{\epsilon_{ox}}{\epsilon_{si}} \frac{\Phi_{bs} - \Phi_b(x)}{t_{box}} = c_1(x) + 2t_{si}c_2(x) \approx 0$$

(4.4)

Inserting this into the two-dimensional Poisson equation (4.1) and setting z=0 one ends up with an expression for the surface potential  $\Phi_f(x,z)$  in the channel. Thus, the following reduced equation for  $\Phi_f$  is obtained [88, 56]

$$\frac{d^2\Phi_f(x)}{dx^2} - \frac{\epsilon_{ox}}{\epsilon_{si}} \frac{\Phi_f(x) - V_g + V_{bi}}{t_{si}t_{ox}} = \frac{\rho_{tot}(x)}{\epsilon_{si}}$$

(4.5)

where  $\rho_{tot}(x)$  is the total charge density which in the contacts includes the uniform jellium of positive ionized donors. To be explicit,  $\rho_{tot}$  is given as follows

$$\rho_{tot}(x) = \begin{cases} \frac{|e|n(x)}{\epsilon_{si}} & \text{in the channel} \\ \frac{-|e|(N_d - n(x))}{\epsilon_{si}} & \text{in source/drain} \end{cases}$$

(4.6)

and n(x) has to be calculated quantum mechanically as explained in the next section. Note, that in source and drain  $V_g$  is taken to be zero and  $V_{bi}$  is replaced by the terminal voltages, i.e. zero in source and  $V_{ds}$  in drain. Having calculated  $\Phi_f$  the full 2D potential distribution can be obtained with equation (4.2) by computing  $c_{1,2}$  from equations (4.3) and (4.4); the potential profile in z-direction at a particular position x is illustrated in figure 4.3.

A natural length scale  $\lambda$  appears in the reduced Poisson equation which plays the role of an effective screening length [2, 88]

$$\frac{d^2\Phi_f(x)}{dx^2} - \frac{\Phi_f(x) - V_g + V_{bi}}{\lambda^2} = \frac{\rho_{tot}(x)}{\epsilon_{si}} \quad \text{with} \quad \lambda = \sqrt{\frac{\epsilon_{si}}{\epsilon_{ox}} t_{si} t_{ox}}.$$

(4.7)

This screening length is due to the particular geometry of the considered device and has a somewhat different form for double-gated SOI MOSFET [88, 56]. It has the obvious implication that in order to achieve a small screening length the thickness of the SOI film as well as the gate-oxide thickness have to be reduced appropriately when scaling-down the channel length L. Since a small  $\lambda$  is effective in screening the potential variation at source and drain it is inevitable for scaled-down MOSFETs in order to suppress the short-channel effects and prevent punch-through. The channel length has to be significantly longer than the screening length. Simulations show that the inequality  $2\lambda \lesssim L/3$  should be satisfied in order to get proper MOSFET operation<sup>1</sup>.

#### 4.1.2 Quantum Calculation

As already mentioned, for structures on a geometrical scale considered here a quantum mechanical calculation of the carrier dynamics is inevitable. Since the charge of the electrons significantly influences the potential distribution in the MOSFET structure the induced potential due to electron-electron interaction has to be taken into account. In the present approach the HARTREE-potential is included by calculating self-consistently the electrostatic potential from the POISSON- and the quantum-equations; exchange correlations are neglected in the analysis.

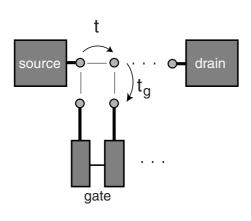

The non-equilibrium Green's function formalism is employed in order to calculate the quantum mechanical charge- and current-distributions in the simulated structure since it allows to easily incorporate scattering in the structure and is capable of simulating an open quantum system by *exactly* taking the coupling to contacts into account [17].

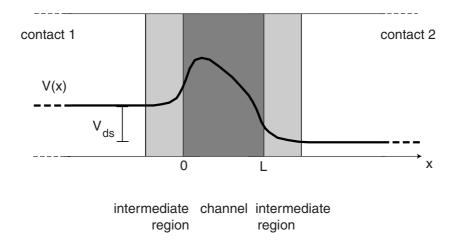

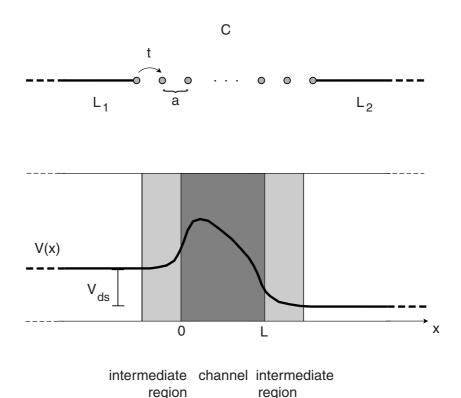

The MOSFET structure is partitioned into three parts as shown in figure 4.2. Source and drain consist of contact 1/2 and the adjacent intermediate region which are regions where the electric field in x-direction is non-zero. The spatial extend of the intermediate regions depends on the screening of the electric field at the transition to the channel and therefore on the electron density in source and drain. The computational domain is truncated to the gray-shaded regions

<sup>&</sup>lt;sup>1</sup>This is a rule of thumb which empirically emerged out of several different simulations.

4.1 THE MODEL 29

which will be called the device or the conductor in the following. The actual contacts with zero electric field extending to  $\pm \infty$  are exactly accounted for via a particular self-energy function [17, 18]. The computation is numerically performed on a tight-binding grid with lattice spacing a and nearest neighbor hopping parameter t. Details of the theory involved and the numerical procedure are given in appendix A.

Figure 4.2: Potential distribution of the device. The light and dark-gray shaded regions represent the computational domain for which the numerical calculation is performed.

In order to describe the dynamics of the electrons in the device the retarded and advanced Green's functions have to be calculated. These Green's functions are determined by the following equations

$$[E - H - \Sigma^R] G^R(\vec{r}, \vec{r}', E) = \delta(\vec{r} - \vec{r}') \quad \text{and} \quad G^A = (G^R)^{\dagger}$$

(4.8)

where the retarded self-energy function  $\Sigma^R$  accounts for the coupling to the contacts, as well as for possible scattering events of electrons in the respective parts of the structure. Since a non-equilibrium situation is considered the functions  $G^n$ ,  $G^p$  and  $\Sigma^{in}$ ,  $\Sigma^{out}$  are necessary as well (note, that throughout the text DATTA's notation is used [17, 18]) which are the electron/hole correlation function and the in- and out-scattering functions which mediate the injection and absorption of carriers. The electron correlation function  $G^n$  is given by the following relation

$$G^{n}(\vec{r}, \vec{r}', E) = \int d\vec{r}_{1} d\vec{r}_{2} G^{R}(\vec{r}, \vec{r}_{1}, E) \Sigma^{in}(\vec{r}_{1}, \vec{r}_{2}) G^{A}(\vec{r}_{2}, \vec{r}', E).$$

(4.9)

Having calculated  $G^n$ , the local density of carriers follows as

$$n(\vec{r}) = 2 \times \frac{1}{2\pi} \int dE \, G^n(\vec{r}, \vec{r}, E)$$

(4.10)

where the factor of 2 accounts for spin degeneracy. With this density the electrostatic potential  $\Phi_f$  can be calculated using the particular surface Poisson equation (4.5) derived in the previous section. The resulting potential is inserted into the Hamiltonian H in the equation for the retarded Green's function (4.8) of the device. Therefore, equations (4.8), (4.10) and (4.5) have to be solved iteratively until self-consistency is achieved.

It is well known that the iteration between the Schrödinger equation and the Poisson equation is numerically unstable and does not lead to a converged solution unless a relaxation factor is included [1]. In particular when dealing with an open quantum system self-consistency is not trivial to achieve (see the discussion in [29]) because the number of carriers is not a conserved quantity. In the simulations of open systems the reservoirs must be able to emit and absorb particles according to the requirement of overall charge neutrality in the device and zero electric field at the boundaries to the contacts. Different strategies are pursued in order to obtain self-consistency. For instance, Pötz employed so-called 'flexible' boundary conditions where the Fermi-energies in the reservoirs are slightly varied to ensure charge neutrality [57]. However, in the present work a Newton-Raphson iteration scheme is used (see appendix C of [42]) which is numerically stable and leads to self-consistency within a few iterations. Details of the procedure are given in appendix A.

Figure 4.3: Potential profile in z-direction using the quadratic approximation.  $E_1^h$  is the first 2D-subband due to z-quantization.

Since the thickness  $t_{si}$  of the SOI film bounded by the gate-oxide and the BOX - is only a few nanometer, the first twodimensional subband due to the quantization in the z-direction is energetically well separated from the conduction band edge given by  $\Phi_f$ , thereby enhancing the effective potential barrier height. Furthermore, the electric quantum limit [68] is considered here where due to the quantization only the lowest 2D subband is occupied which is justified for small  $t_{si}$ . This subband has the heavy effective electron mass  $m_h$  directed along the z-coordinate and a degeneracy factor of two [5]. Therefore, the transport mass is the light electron effective mass  $m_l$  which is also used in the HAMILTONIAN for the 1D calculations. Contributions of higher subbands are taken into account by a nu-

merical factor according to reference [49] which is justifiable if the fraction of higher subbands is not too large. This factor is given by  $2 \times (total\ population)/(population\ of\ 1st\ subband)$  where the 2 is due to the valley degeneracy of the first subband [49]. For 300 K,  $t_{si}=10\,\mathrm{nm}$  and  $E_f\approx 150\,\mathrm{meV}$  the factor is approximately  $2\times 2.1$  and for  $t_{si}=15\,\mathrm{nm}$  about  $2\times 3.2$ , where  $E_f$  is the FERMI energy relative to the conduction band edge in the source contact.

4.1 THE MODEL 31

The potential distribution for two different gate voltages is depicted in figure 4.3 for one point x in the channel. The potential profile is given by equation (4.2) for a particular surface potential  $\Phi_f$ . The position of the first 2Dsubband is indicated for the two profiles as well. However, for simplicity the position of the first two-dimensional subband relative to the conduction band is approximated by the energy  $E_1^h$  of a rectangular potential well<sup>2</sup> which is constant throughout the channel and given by

$$E_1^h = \frac{\hbar^2 \pi^2}{2m_h t_{si}^2} \tag{4.11}$$

One could compute an  $\tilde{E}_1^h(x)$  depending on the position in the channel using explicitly the parabolic approximation of the potential under the assumption that it is possible to decouple the z-part of the Hamiltonian at each position x. This approximation holds until the potential variation along the x-direction is comparable to the variation in z-direction [67, 5] so that for ultra-short channel MOSFETs the validity can be questioned. A fully two-dimensional calculation would be necessary in this case.

Since all quantities will be averaged over z by integrating over z and dividing by  $t_{si}$  the exact form of the wave function of the first subband is of no importance as long as it is normalized so that the integration over the z-coordinate yields a factor of one. Translational invariance in the y, z-directions is assumed in source and drain, i.e. in the contacts and the intermediate regions for the computation of the carrier density. Hence, three-dimensional densities can easily be obtained by replacing all FERMI distribution factors by the so-called supply func-

Figure 4.4:  $I_d$  contributions from source and the 'gate contacts'.

tions as stated in appendix A. The supply function is essentially the FERMI-integral of the order 1/2 multiplied by the energy-independent 2D density of states. In the channel, translational invariance can only be assumed in the y-direction whereas in z-direction the quantization has to be taken into account. Therefore, a special averaging procedure has to be performed which is described in the appendix. This procedure yields the three-dimensional carrier density of the first 2D subband in the channel and is also employed to get the 3D current density. As was mentioned in section 2.4.1, there is a fundamental contact resistance  $R_c$  due to a finite number of current carrying modes in the channel. Hence, if the width of the device is rather small the assumption of translation invariance is not valid any more. Here, we estimate the fundamental contact resistance according to reference [19] to be  $70\,\Omega$  for a device with a width of  $700\,\mathrm{nm}$  and  $E_f = 150\,\mathrm{meV}$ . In order to keep the simulation simple translational invariance in y-direction is assumed and the current  $I_d$  is corrected afterwards by adding  $R_c$  and  $R_{ds} = V_{ds}/I_d$  which gives for unchanged  $V_{ds}$  the corrected

$<sup>{}^{2}</sup>E_{1}^{h}$  is the difference between the band bottom and the first subband.

current  $\tilde{I}_d$  what is true for all series resistances. Parasitic series resistances do not only influence the drain current. The gate voltage is reduced as well according to  $\tilde{V}_g = V_g - R_s I_d$  where  $R_s$  is the parasitic source resistance. This effect is neglected in the present analysis since  $R_s = R_c/2 = 35\,\Omega$  results only in a slight change of  $V_g$ .

Care has to be taken with the effective masses. In source and drain the electron density is computed with the 3D density of states effective mass  $m_{dos} = \sqrt[3]{m_h m_l^2}$  [5]. In the channel the 2D  $m_{dos} = \sqrt{m_h m_l}$  and the conductivity or transport effective mass is simply the light electron mass  $m_l$ .

After self-consistency is achieved the source-drain current through the structure is calculated according to (see appendix A)

$$I_{sd} = W \times \frac{2e}{h} \int dE \left( f_s(E) - f_d(E, V_{ds}) \right) \times T(E)$$

(4.12)

where T(E) is the transmission function for carriers moving from source to drain and  $f_{s,d}$  are the equilibrium FERMI distribution functions of source and drain.

For very thin gate oxides direct tunneling of electrons from the gate to the channel becomes more and more important and increases the current  $I_d$  in the subthreshold regime. Hence, the off-current of devices with ultra-thin gate oxides 'saturates' for  $V_g \approx 0 \, \text{V}$  at the magnitude of the tunneling current. This means that for  $V_g \lesssim 0$  the transport is dominated by the tunneling current from gate to channel, in particular by that part of the gate adjacent to the drain. For this part of the gate there is only the thin gate oxide as barrier so that the tunneling current raises with increasing difference  $V_{ds} - V_q$ . The subthreshold saturation of  $I_d$  can corrupt logic applications due to the lack of an off-state. Tunneling can be incorporated in the computations by attaching N'gate contacts' with length L/N to the gate oxide along the channel as depicted in figure 4.4. All these contacts have the same  $E_f$ , i.e. they are shortened as is the case for the real gate. In the limit  $N \to \infty$  a continuous gate follows. For simplicity, the gate electrode is assumed to consist of the same highly doped  $n^{++}$ silicon as source and drain. The total drain current is the sum of the current from source to drain and the part from gate to drain. This is illustrated in figure 4.4 with arrows going from source to drain and from each 'gate contact' to drain. The total drain current is explicitly given by

$$I_d = I_{sd} + \sum_{i=1}^{N} I_{gd}^i. (4.13)$$

Again, details can be found in the appendix.

#### 4.2 Simulations

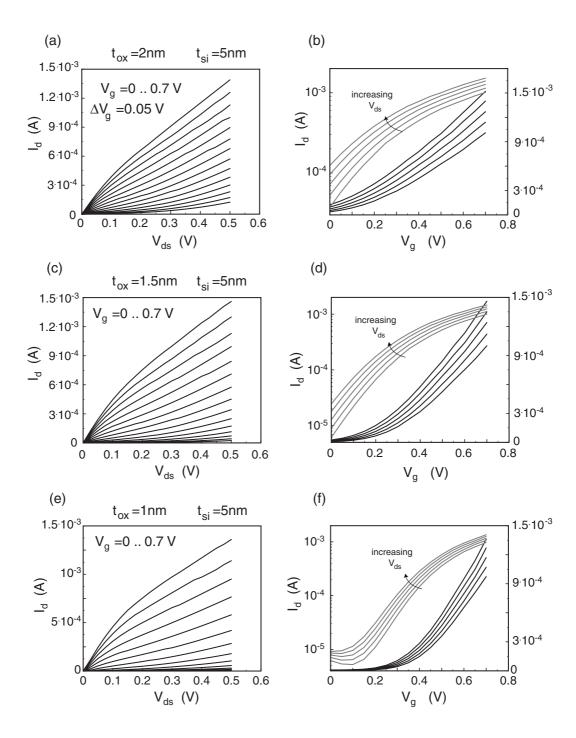

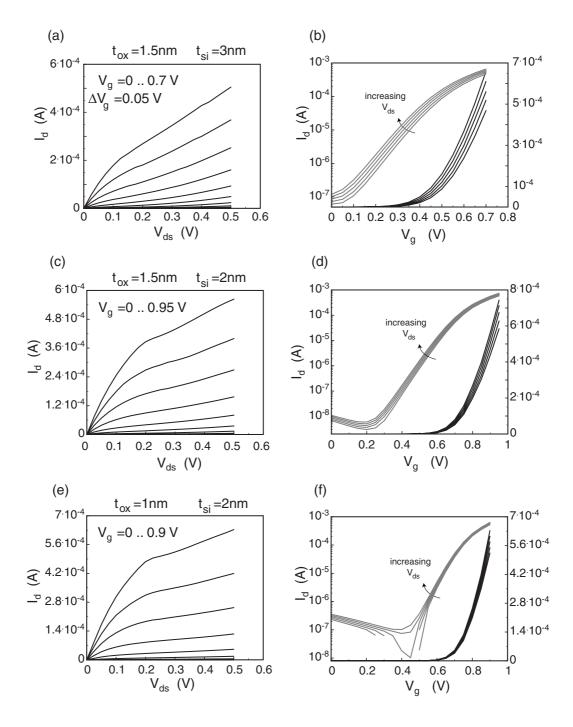

In the following the computations presented above are used to investigate the electrical behavior of single-gated short-channel MOSFETs. In particular, the

4.2 SIMULATIONS 33

influence of the SOI and oxide thickness on the output characteristics is studied. For all simulations room temperature and a width of 700 nm is assumed. In addition, the doping concentration in source and drain is always taken to be  $3\times 10^{20}\,\mathrm{cm^{-3}}$  which yields an  $E_f=150\,\mathrm{meV}$ . According to DATTA et al. [19] the fundamental contact resistance is estimated to be 70  $\Omega$  for the chosen width. As mentioned above, the calculated drain current has to be corrected appropriately which is done for all simulations displayed below.

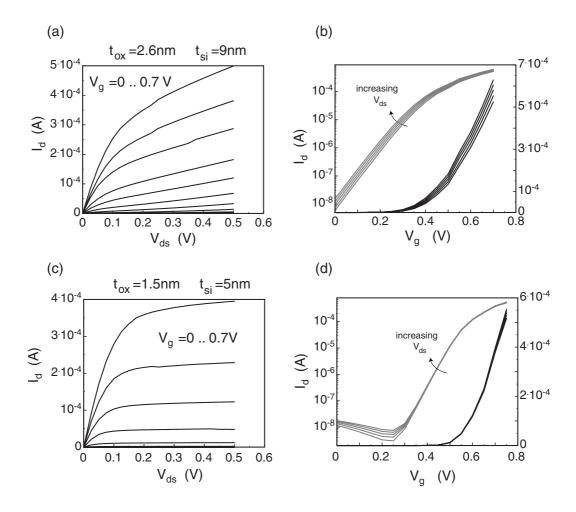

#### 4.2.1 A 30 nm Device

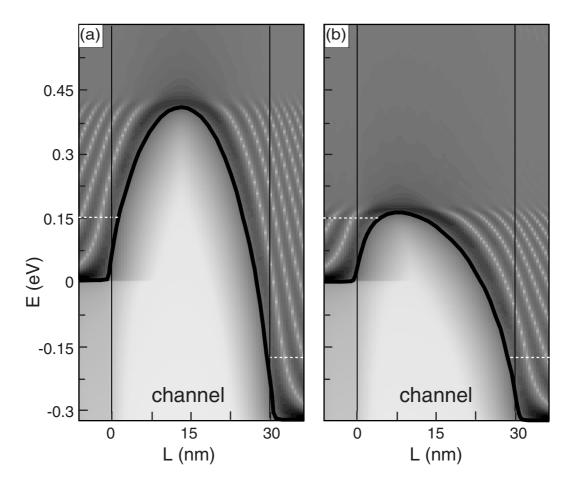

Figure 4.5 (a) and (b) show typical gray-scale images of the local density of states versus energy for two different  $V_g$  and equal bias. Additionally, the potential profile of the conduction band is shown in the figure as well. The

Figure 4.5: Local density of states for a 30 nm transistor at room temperature. The darker the image the higher the density of states. The position of the FERMI energies in source and drain are indicated by the white dotted lines. The vertical black lines illustrate the transition between channel and source/drain. Parameters for the simulation:  $V_{ds}=0.325\,\mathrm{V}$  and (a)  $V_g=0.05\,\mathrm{V}$ , (b)  $V_g=0.55\,\mathrm{V}$ .

parameters for the calculation are L = 30 nm,  $t_{ox} = 2 \text{ nm}$  and  $t_{si} = 10 \text{ nm}$ . The width and the doping concentration have the values stated above;  $V_{ds}$  and  $V_g$  are as indicated in the figure.

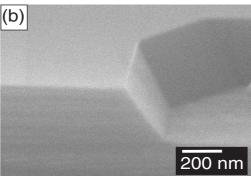

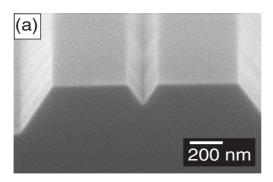

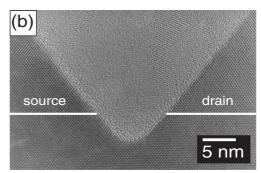

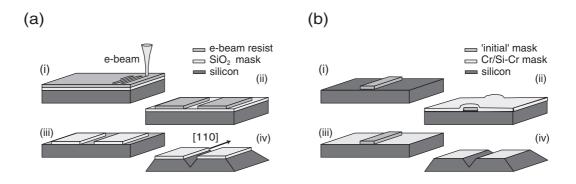

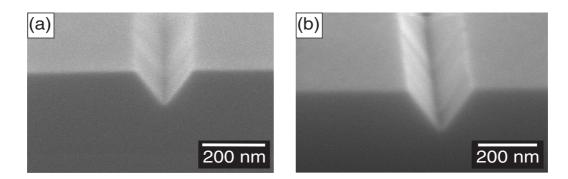

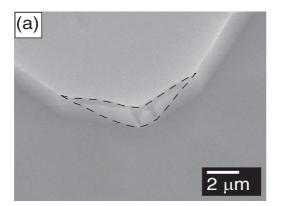

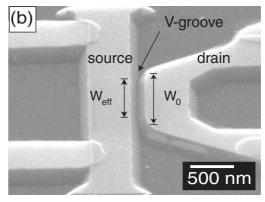

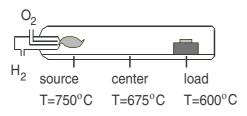

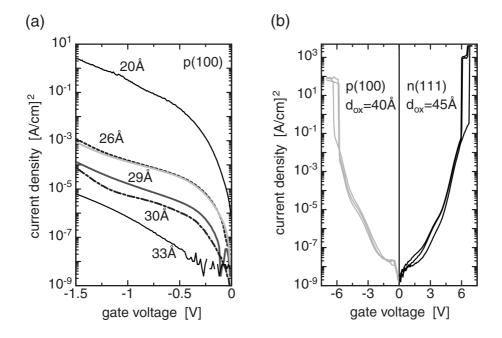

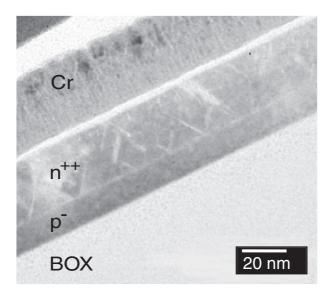

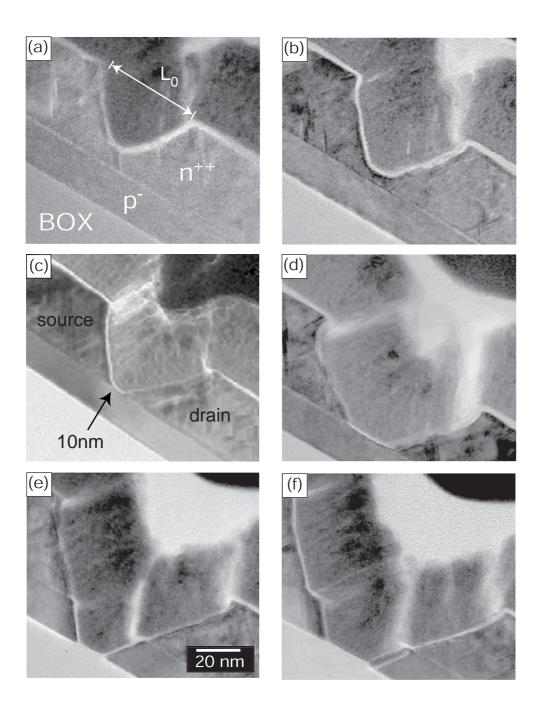

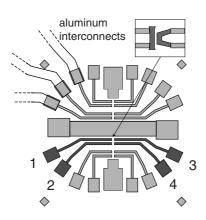

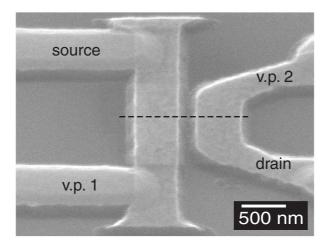

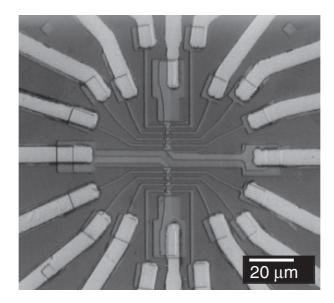

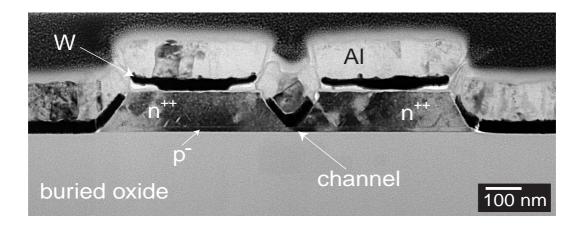

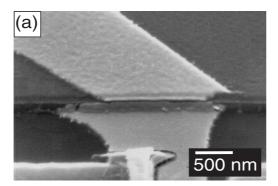

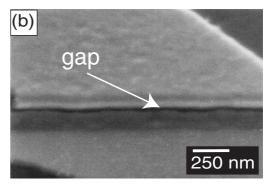

The local density of states exhibits the typical structure for energies below the maximum potential energy due to back-reflection of carriers [40]. Above this energy a continuum of states is available. The light gray within the potential barrier indicates a non-zero density of states which is due to the leakage of the electron wave-function into the potential barrier. A very high density of states can be seen right above the conduction band edge. Hence, vertical quantization is not important for  $t_{si} \geq 10 \, \mathrm{nm}$ .