# OpenMP Scalability Limits on Large SMPs and How to Extend Them.

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

# Diplom-Informatiker Dirk Schmidl aus Erkelenz

Berichter: Universitätsprofessor Dr. Matthias S. Müller Universitätsprofessor Dr. Christian Bischof

Tag der mündlichen Prüfung: 28. Juni 2016

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

## Zusammenfassung

Aktuell sind Rechenknoten mit zwei Prozessoren die am häufigsten verwendeten Knoten im Bereich des Hochleistungsrechnen. Viele tausend dieser Knoten können über ein schnelles Netzwerk miteinander gekoppelt werden zu einem Rechencluster. Um diese Cluster zu programmieren wird üblicherweise das Message Passing Interface (MPI) verwendet. MPI erfordert es die Parallelität und die verwendeten Datentransfers sehr explizit über Funktionsaufrufe zu realisieren.

Eine Alternative zu MPI, welche eine Parallelisierung auf höherer Ebene erlaubt ist OpenMP. In OpenMP können serielle Programme mit Pragmas angereichert werden um rechenintensive Teile der Anwendung parallel auszuführen. In vielen Fällen ist dies mit weniger Aufwand verbunden wie eine Parallelisierung mit MPI, bei der die gesamte Datenverteilung über alle Knoten im gesamten Programm implementiert werden muss. Der Nachteil von OpenMP ist, dass es nur auf Maschinen mit geteiltem Hauptspeicher und nicht auf den weit verbreiteten Clustern eingesetzt werden kann. Eine Reihe von Herstellern hat sich aber darauf spezialisiert große Maschinen mit geteiltem Hauptspeicher herzustellen. Da geteilter Hauptspeicher und damit einhergehende Anforderungen an die Koheränz der Speicher und Caches kompliziert zu implementieren sind, haben solche Maschinen Eigenheiten, die bei der Programmierung mit OpenMP berücksichtigt werden müssen um eine gute Parallelisierung zu erreichen.

In dieser Arbeit beschäftige ich mich damit die Eigenschaften verschiedener dieser großen Maschinen mit geteilten Hauptspeicher und die Programmierbarkeit mit OpenMP zu untersuchen. An Stellen an denen OpenMP nicht die nötigen Mittel für eine gute Parallelisierung liefert, werde ich Verbesserungen aufzeigen.

Weiterhin beschäftige ich mich in der Arbeit damit, wie Anwendungen mit OpenMP für solche Maschinen systematisch optimiert werden können. Hierbei wird die Nutzbarkeit von Performance-Analyse-Werkzeugen untersucht und Verbesserungen im Bereich der Task-basierten Analyse vorgestellt, welche die Optimierung für große Systeme vereinfachen. Abschließend stelle ich noch ein Modell vor, welches verwendet werden kann um eine Performance-Abschätzung für eine Anwendung auf einem solchen System vorzunehmen.

Abschließend wird anhand von zwei Anwendungen gezeigt, dass es die vorgestellten Optimierungen erlauben mit echten Nutzeranwendungen eine Skalierbarkeit mit OpenMP auf großen Systemen zu erreichen.

## **Abstract**

The most widely used node type in high-performance computing nowadays is a 2-socket server node. These nodes are coupled to clusters with thousands of nodes via a fast interconnect, e.g. Infiniband. To program these clusters the Message Passing Interface (MPI) became the de-facto standard. However, MPI requires a very explicit expression of data layout and data transfer in a parallel program which often requires the rewriting of an application to parallelize it.

An alternative to MPI is OpenMP, which allows to incrementally parallelize a serial application by adding pragmas to compute-intensive regions of the code. This is often more feasibly than rewriting the application with MPI. The disadvantage of OpenMP is that it requires a shared memory and thus cannot be used between nodes of a cluster. However, different hardware vendors offer large machines with a shared memory between all cores of the system. However, maintaining coherency between memory and all cores of the system is a challenging task and so these machines have different characteristics compared to the standard 2-socket servers. These characteristics must be taken into account by a programmer to achieve good performance on such a system.

In this work, I will investigate different large shared memory machines to high-light these characteristics and I will show how these characteristics can be handled in OpenMP programs. When OpenMP is not able to handle different problems, I will present solutions in user space, which could be added to OpenMP for a better support of large systems.

Furthermore, I will present a tools-guided workflow to optimize applications for such machines. I will investigate the ability of performance tools to highlight performance issues and I will present improvements for such tools to handle OpenMP tasks. These improvements allow to investigate the efficiency of task-parallel execution, especially for large shared memory machines. The workflow also contains a performance model to find out how well the performance of an application is on a system and when to stop tuning the application.

Finally, I will present two application case studies where user codes have been optimized to reach a good performance by applying the optimization techniques presented in this thesis.

## **Contents**

| Lis | st of | Figure  | 5                                                                          | i۱  |

|-----|-------|---------|----------------------------------------------------------------------------|-----|

| Lis | st of | Tables  |                                                                            | vi  |

| 1   | Intr  | oductio | on                                                                         | 1   |

|     | 1.1   | Main    | Contributions                                                              | į   |

|     | 1.2   |         | A Architectures                                                            |     |

|     | 1.3   |         | of-the-art in NUMA Programming                                             |     |

|     | 1.4   |         | iment Hardware                                                             |     |

| 2   | A B   | enchm   | ark-Guided Characterization of Large Shared-Memory Ma-                     | -   |

|     | chin  | es      |                                                                            | 11  |

|     | 2.1   | Memo    | bry Performance                                                            | 12  |

|     |       | 2.1.1   | Serial Memory Performance                                                  | 12  |

|     |       | 2.1.2   | Parallel Memory Bandwidth                                                  | 14  |

|     |       | 2.1.3   | $memory\_go\_around \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 16  |

|     |       | 2.1.4   | Data Management                                                            | 18  |

|     | 2.2   | Openl   | MP Runtime Issues                                                          | 20  |

|     |       | 2.2.1   | EPCC Benchmarks                                                            | 20  |

|     |       | 2.2.2   | Nested Parallelism                                                         | 22  |

|     | 2.3   | Distar  | nce Matrices                                                               | 24  |

|     |       | 2.3.1   | System Locality Distance Information Table                                 | 25  |

|     |       | 2.3.2   | Automatic Matrix Generation                                                | 26  |

|     | 2.4   | Summ    | nary                                                                       | 28  |

| 3   | lmp   | roved l | Memory Allocation and Migration in OpenMP Programs                         | 29  |

|     | 3.1   | Facets  | s of Affinity in OpenMP Programs                                           | 31  |

|     |       | 3.1.1   | Distribution of Data                                                       | 32  |

|     |       | 3.1.2   | Placement of Threads                                                       | 33  |

|     |       | 3.1.3   | Distribution of Work                                                       | 34  |

|     | 3.2   | Gener   | ating Reasonable Place Lists                                               | 35  |

|     |       | 3.2.1   | The Traveling Salesman Problem                                             | 36  |

|     |       | 3.2.2   | Approximation algorithms                                                   | 37  |

|     |       | 3.2.3   | Evaluation                                                                 | 38  |

|     |       | 201     | D 1.1                                                                      | 4.0 |

|   | 3.3 | OMPX: An OpenMP Extension Library for Memory Placement 3.3.1 Memory Allocation and Initialization | 40<br>41 |

|---|-----|---------------------------------------------------------------------------------------------------|----------|

|   |     | 3.3.2 Memory Migration                                                                            | 42       |

|   |     | 3.3.3 Performance Modeling for Memory Migration                                                   | 43       |

|   | 3.4 | Summary                                                                                           | 46       |

| 4 | NUI | MA-aware Scheduling Strategies                                                                    | 47       |

|   | 4.1 | <b>∂</b>                                                                                          | 50       |

|   |     | 4.1.1 A NUMA-aware Load Balancing Benchmark                                                       | 50       |

|   | 4.2 | A NUMA-aware Work Scheduler                                                                       | 54       |

|   |     | 4.2.1 The Scheduling Principle                                                                    | 55       |

|   |     | 4.2.2 Work Stealing                                                                               | 55       |

|   |     | 4.2.3 Performance Results                                                                         | 58       |

|   | 4.3 | Locality-aware Task Programming                                                                   | 59       |

|   |     | 4.3.1 Implementation of task schedulers                                                           | 60       |

|   |     | 4.3.2 Task creation patterns                                                                      | 61       |

|   |     | 4.3.3 NUMA-aware task creation                                                                    | 62       |

|   |     | 4.3.4 Tasking Performance on NUMA systems                                                         | 63       |

|   | 4.4 | Summary                                                                                           | 64       |

| 5 |     | bling NUMA-aware Task-performance Analysis                                                        | 67       |

|   | 5.1 | Task-related Performance Issues                                                                   | 67       |

|   | 5.2 | Analyzing Tasks with Sampling Based Performance Tools                                             | 70       |

|   |     | 5.2.1 Intel VTune Amplifier XE                                                                    | 71       |

|   |     | 5.2.2 Oracle Solaris Studio Performance Analyzer                                                  | 73       |

|   | 5.3 | Event-Based Performance Tools                                                                     | 74       |

|   |     | 5.3.1 Gathering performance data for tasks in Score-P                                             | 74       |

|   | - 1 | 5.3.2 Detecting task-related performance issues                                                   | 77       |

|   | 5.4 | Improvements to Investigate Tasks on NUMA Machines                                                | 84       |

|   |     | 5.4.1 Shortcomings in Score-P Regarding Task Analysis                                             |          |

|   |     | 5.4.2 Combining Traces with Hardware Information                                                  |          |

|   | 5.5 | 5.4.3 Evaluation                                                                                  | 85<br>88 |

|   | 0.0 | Summary                                                                                           | 00       |

| 6 |     | Vorkflow to Program Large SMP Machines                                                            | 89       |

|   | 6.1 | Tools-guided Performance Tuning on Big SMP Machines                                               | 90       |

|   |     | 6.1.1 Tuning Cycle                                                                                | 90       |

|   |     | 6.1.2 Investigated Issues                                                                         | 91       |

|   | 0 - | 6.1.3 Conjugate Gradient Method                                                                   | 96       |

|   | 6.2 | Modeling OpenMP Performance                                                                       |          |

|   |     | 6.2.1 Performance Models                                                                          |          |

|   |     | 6.2.2 A Performance Model for large SMPs                                                          |          |

|   |     | 6.2.3 Model Description                                                                           | 103      |

| Bil | bliogr | raphy 1                                  | 15 |

|-----|--------|------------------------------------------|----|

| 7   | Sum    | mary and Conclusion 13                   | 13 |

|     | 6.4    | Summary                                  | 11 |

|     |        | 6.3.2 TrajSearch                         | 08 |

|     |        | 6.3.1 SHEMAT-Suite                       | 07 |

|     | 6.3    | Case Studies                             | 06 |

|     |        | 6.2.4 Example: Conjugate Gradient Method | 05 |

|     |        |                                          |    |

## **List of Figures**

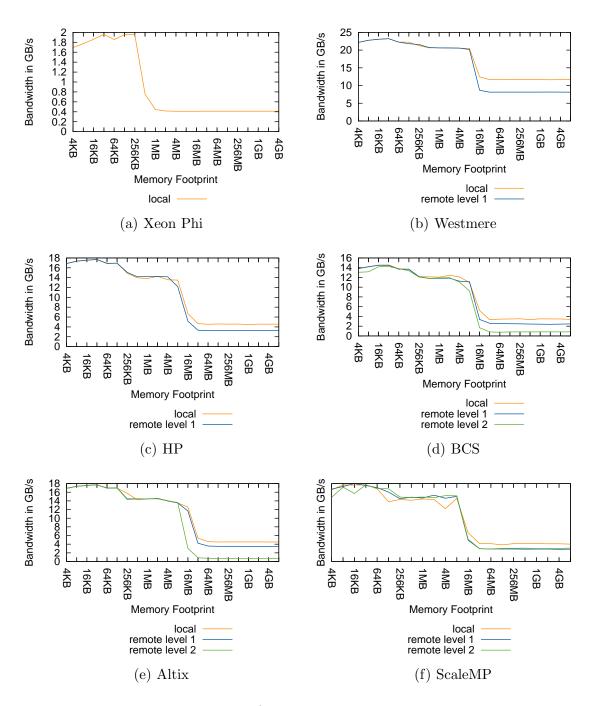

| 2.1 | Read Bandwidth in GB/s reached for different NUMA levels measured on the Xeon Phi, Westmere, HP, BCS, Altix and ScaleMP |     |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

|     | system for different memory footprints                                                                                  | 13  |

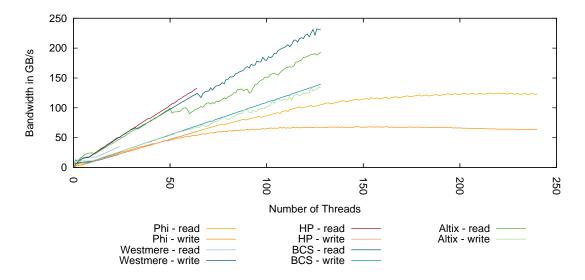

| 2.2 | Parallel read and write bandwidth on the Westmere, HP, Altix,                                                           |     |

|     | BCS and Xeon Phi systems for an increasing number of threads                                                            | 15  |

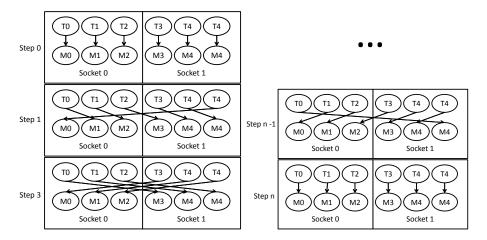

| 2.3 | The memory_go_around benchmark works in n+1 steps. In the                                                               |     |

|     | first step the memory of the right neighbour is used to measure                                                         |     |

|     | the bandwidth, in the next step the memory of the next neighbour                                                        |     |

|     | and so on. This increases the distance between thread and memory                                                        |     |

|     | v                                                                                                                       |     |

|     | in every step, until half of the steps are done, then the distance                                                      | 1.0 |

| 2.4 | decreases until it reaches zero in the last step                                                                        | 16  |

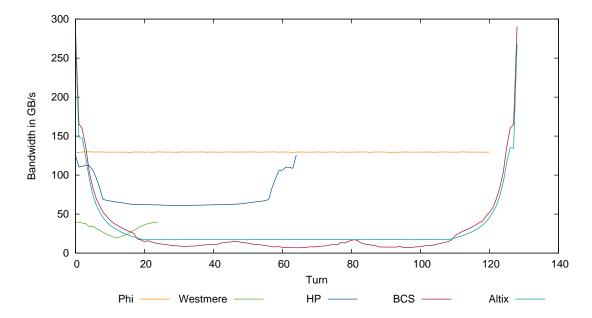

| 2.4 | Bandwidth measured with the memory_go_around benchmark for                                                              |     |

|     | n+1 steps with n threads on the Westmere, HP, Altix, BCS, and                                                           |     |

|     | Xeon Phi system                                                                                                         | 17  |

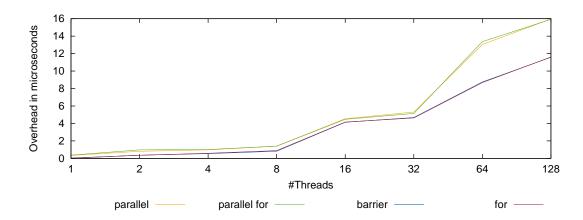

| 2.5 | Overhead for different OpenMP constructs measured with the EPCC                                                         |     |

|     | microbenchmarks on the BCS machine and the Intel Compiler 14.0.                                                         | 22  |

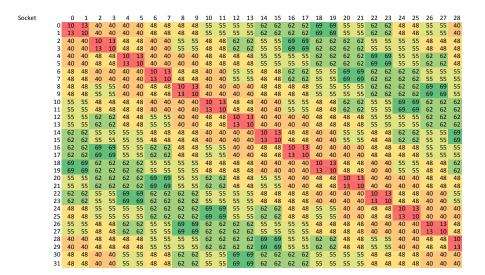

| 2.6 | (a)Distance Information retrieved from Linux and (b) measured                                                           |     |

|     | distance with our distance matrix benchmark on a 8-Socket Intel                                                         |     |

|     | Nehalem-EX machine                                                                                                      | 25  |

| 2.7 | Distance information retrieved from Linux on an SGI Altix UV                                                            | 26  |

| 2.8 | Distance matrix of the HP (left) and the BCS system (right). The                                                        |     |

|     | matrix is scaled such that the upper left value is always ten, larger                                                   |     |

|     | numbers indicate higher distances                                                                                       | 27  |

|     |                                                                                                                         |     |

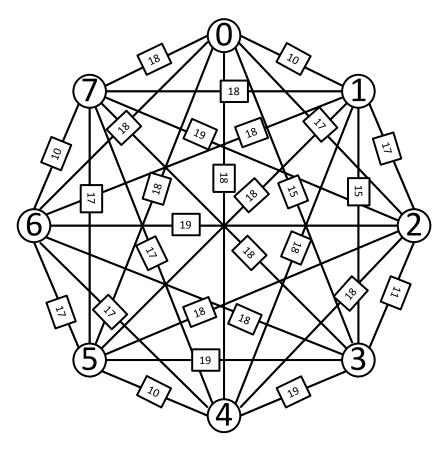

| 3.1 | Graph representation of the measured distances between the sockets                                                      |     |

|     | on the 8-socket HP system                                                                                               | 37  |

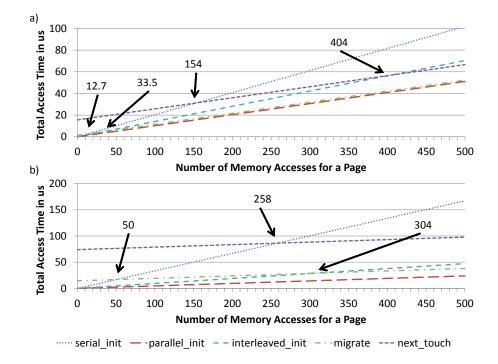

| 3.2 | Access time for different numbers of accesses of a complete page                                                        |     |

|     | for different initialization and migration strategies on the 2-socket                                                   |     |

|     | Westmere a) and 4-socket SandyBridge b) system. The points of                                                           |     |

|     | intersection indicate when migration is beneficial over serial or                                                       |     |

|     | interleaved                                                                                                             | 45  |

|     |                                                                                                                         |     |

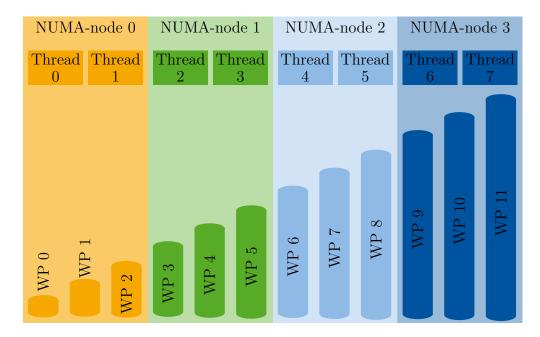

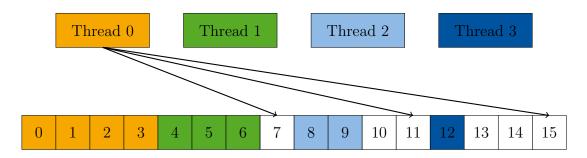

| 4.1 | Distribution of work packages (WPs) across NUMA nodes for the                                                           |     |

|     | load balancing benchmark. Exemplary for 12 work packages (WPs)                                                          |     |

|     | on a machine with 8 threads and 4 NUMA nodes                                                                            | 51  |

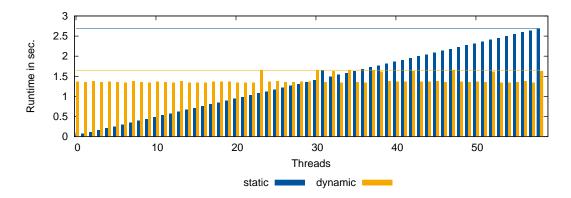

| 4.2 | Load balancing benchmark results on a Xeon Phi system, running with 59 threads. Scheduling 3840 work packages with a static and                                   | <b>F</b> 0 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

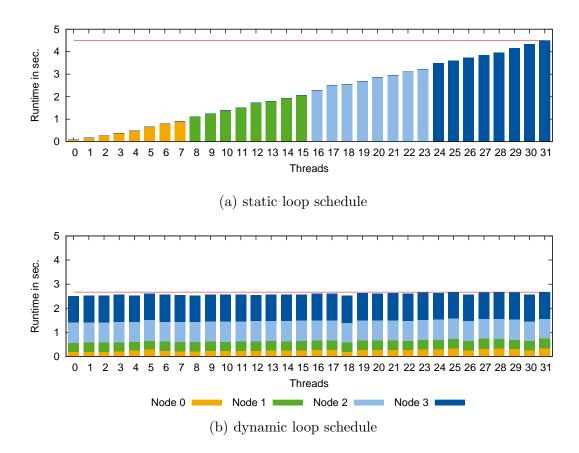

| 4.3 | dynamic scheduled parallel loop                                                                                                                                   | 52         |

| 1 1 | running with 32 threads. Scheduling 3840 work packages with a static and dynamic scheduled parallel loop                                                          | 53         |

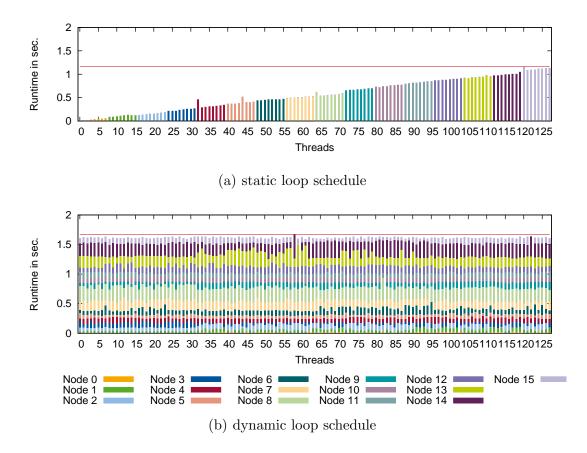

| 4.4 | Load balancing benchmark results on a 16-socket system, running with 128 threads. Scheduling 3840 work packages with a static and dynamic scheduled parallel loop | 54         |

| 4.5 | Illustration of the NUMA-aware scheduler for 16 work packages and 4 threads. Thread 0 finishes its packages first and can now steal                               | 0.1        |

|     | package 7, 11 or 15                                                                                                                                               | 56         |

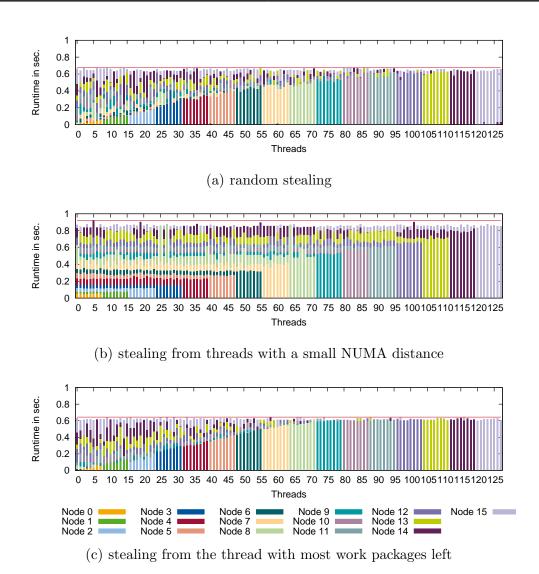

| 4.6 | Load balancing benchmark results the NUMA-aware scheduler with different strategies for work stealing.                                                            | 57         |

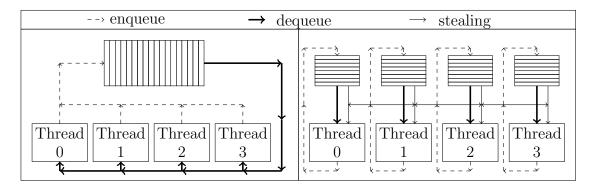

| 4.7 | Illustration of a central task queue used by four threads (left) and                                                                                              |            |

| 1.0 | thread-local task queues for four threads (right)                                                                                                                 | 60         |

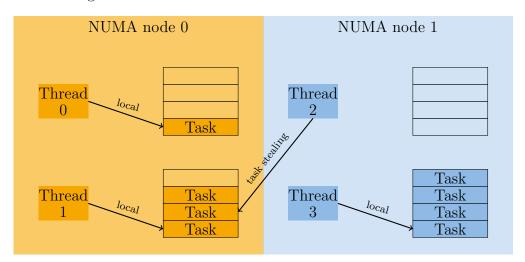

| 4.8 | Illustration of local task queues for four threads. Thread 2 has an empty queue and applies task stealing. The other threads have local                           |            |

|     | tasks to execute.                                                                                                                                                 | 62         |

| 4.9 | Load balancing benchmark results when tasking was applied. All                                                                                                    |            |

|     | tasks were created by the thread which also initialized the data used                                                                                             | co.        |

|     | by the task, to maintain locality for thread-local task queues                                                                                                    | 63         |

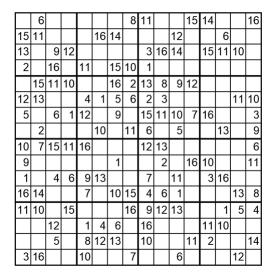

| 5.1 | A 16x16 Sudoku board with initial entries (left) and the algorithm                                                                                                |            |

| r 0 | in pseudocode to solve the sudoku puzzle(right)                                                                                                                   | 71         |

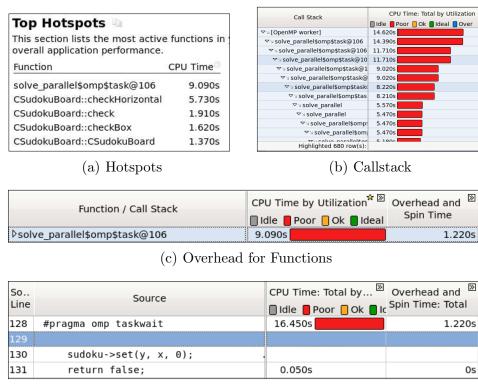

| 5.2 | Analysis results of the Sudoku solver with the Intel VTune Amplifier XE for 32 threads on a 2-socket SandyBridge system with 32 cores                             |            |

|     | in total                                                                                                                                                          | 72         |

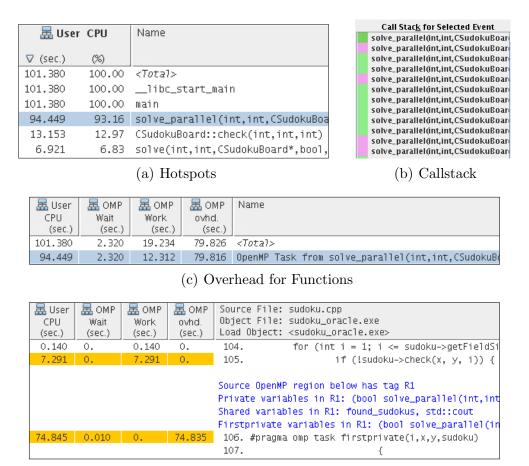

| 5.3 | Analysis results of the Sudoku solver with the Oracle Solaris Studio                                                                                              |            |

|     | Performance Analyzer for 32 threads on a 2-socket SandyBridge system with 32 cores in total                                                                       | 73         |

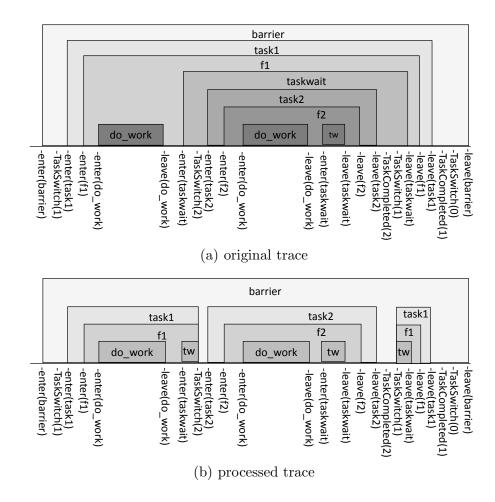

| 5.4 | Call stacks based on the present enter and exit events in the OTF2                                                                                                | 10         |

|     | trace, in (a) for the original trace and in (b) after the virtual exit                                                                                            |            |

|     | and enter events were added                                                                                                                                       | 76         |

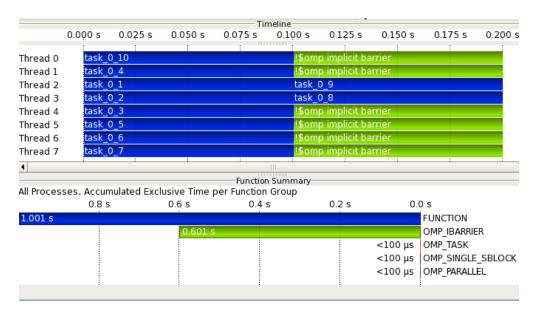

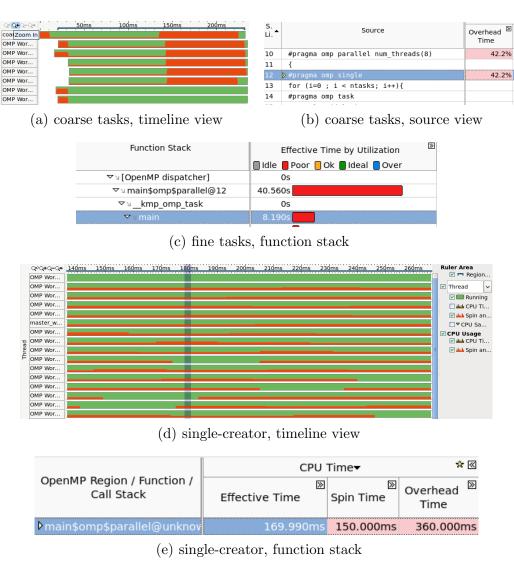

| 5.5 | Vampir screenshot showing how too coarse grained tasks can be detected                                                                                            | 77         |

| 5.6 | Vampir screenshot showing how too fine grained tasks can be detected.                                                                                             | 78         |

| 5.7 | Vampir screenshot showing the single-creator pattern                                                                                                              | 79         |

| 5.8 | Performance analysis with VTune for the test programs with too coarsely grained tasks, too finely grained tasks and with a bottle-                                |            |

|     | neck on the creator site with the single-creator pattern                                                                                                          | 80         |

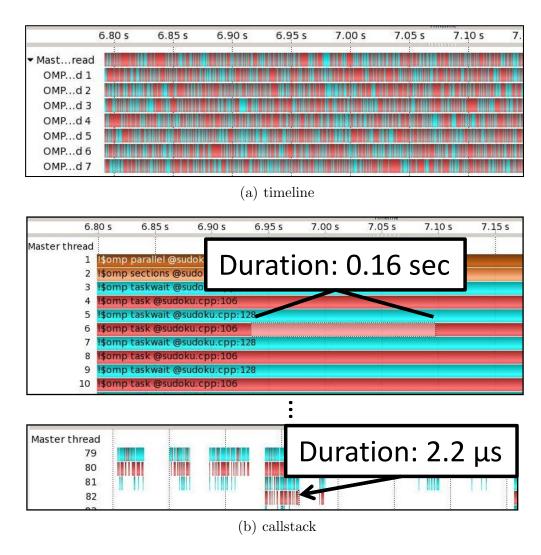

| 5.9 | Vampir screenshot showing the timeline and callstack view for the                                                                                                 | 0.0        |

|     | Sudoku solver                                                                                                                                                     | 82         |

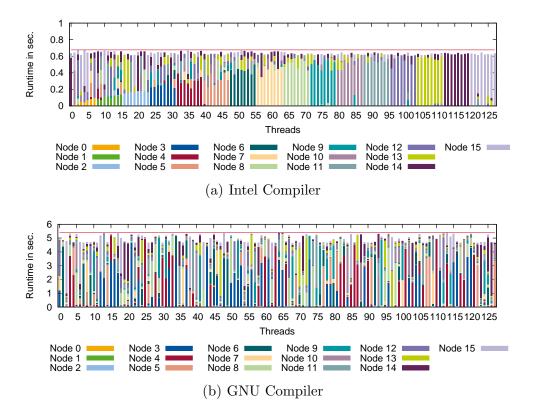

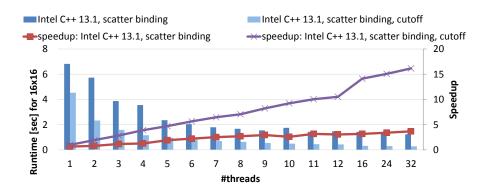

| 5.10       | Performance of the Sudoku solver example without and with the                                                                                                                                                                                                                                                                                                                                                                                   |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | cut-off strategy used                                                                                                                                                                                                                                                                                                                                                                                                                           | 83  |

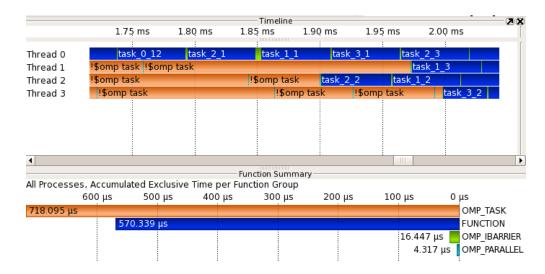

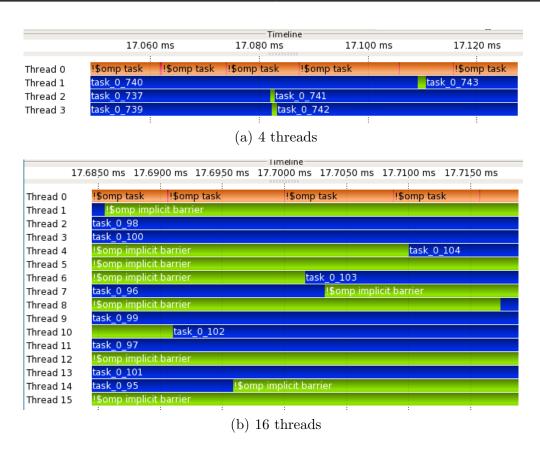

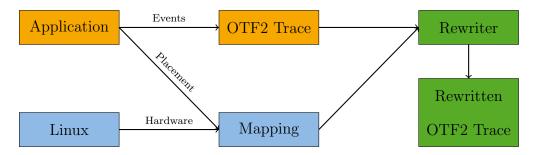

| 5.11       | Workflow of the trace rewriter tool to use hardware information to analyze NUMA related task scheduling issues                                                                                                                                                                                                                                                                                                                                  | 85  |

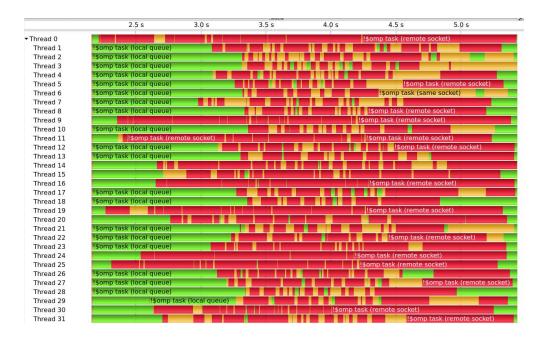

| 5.12       | Vampir screenshot showing the tasks during the execution of the load balancing benchmark with the Intel runtime. Tasks executed on the creating thread ar shown in green, stolen tasks from the same                                                                                                                                                                                                                                            | 0.0 |

| 5.13       | NUMA-node in orange and from remote NUMA-nodes in red Vampir screenshot showing the tasks during the execution of the load balancing benchmark with the GNU runtime system. Tasks executed on the creating thread are shown in green, stolen tasks from the same NUMA-node in orange and from remote NUMA-nodes in red. Comparing this figure to figure 5.12, a huge difference in the way tasks are scheduled in the GNU and Intel runtime can |     |

|            | be observed                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87  |

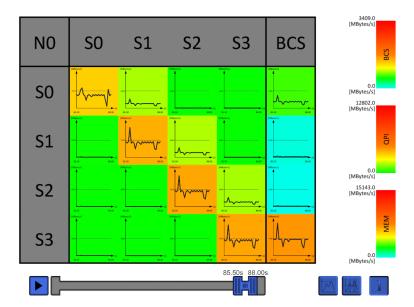

| 6.1<br>6.2 | Illustration of the tuning cycle                                                                                                                                                                                                                                                                                                                                                                                                                | 90  |

|            | system                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95  |

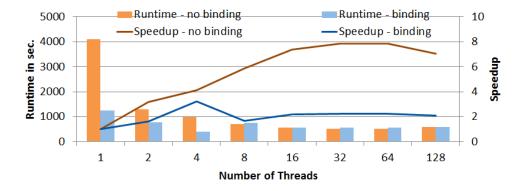

| 6.3<br>6.4 | Hotspots of the CG solver investigated with Intel VTune Performance reached with the CG solver on the BCS system after                                                                                                                                                                                                                                                                                                                          | 97  |

| 6.5        | parallelizing hotspots with and without thread binding Local and remote memory accesses of the matrix vector multiplica-                                                                                                                                                                                                                                                                                                                        | 97  |

| 6.6        | tion in the CG solver measured with Intel VTune Performance reached with the CG solver on the BCS system after optimizing the memory access pattern by distributing the matrix                                                                                                                                                                                                                                                                  | 98  |

|            | across NUMA nodes                                                                                                                                                                                                                                                                                                                                                                                                                               | 99  |

| 6.7        | Overhead in the sparse matrix vector operation in the CG solver, measured with Intel VTune                                                                                                                                                                                                                                                                                                                                                      | 99  |

| 6.8        | Performance reached with the CG solver on the BCS system after<br>optimizing the memory access pattern by distributing the matrix                                                                                                                                                                                                                                                                                                               |     |

|            | across NUMA nodes                                                                                                                                                                                                                                                                                                                                                                                                                               | 100 |

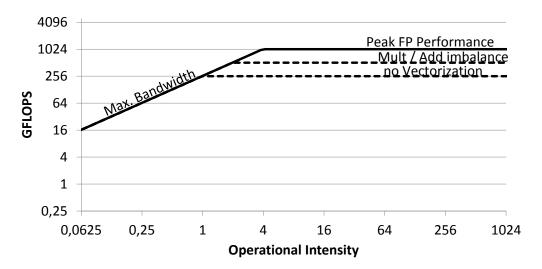

| 6.9        | The Roofline Model applied to the BCS system                                                                                                                                                                                                                                                                                                                                                                                                    |     |

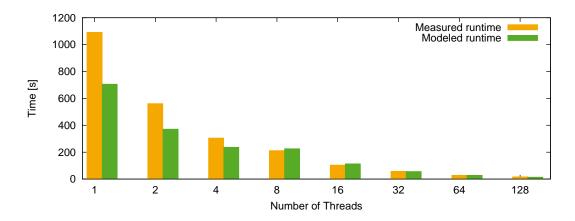

| 6.10       | Measured and modeled runtime for the CG solver                                                                                                                                                                                                                                                                                                                                                                                                  |     |

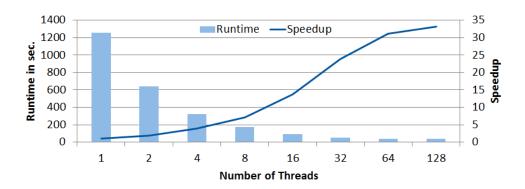

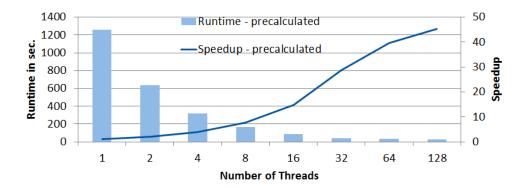

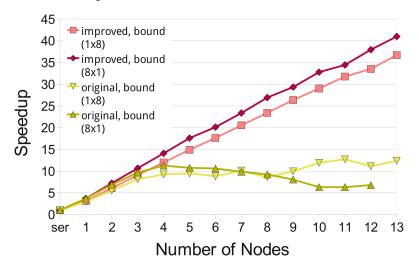

| 6.11       | Speedup of the SHEMAT-Suite code on a 13 board ScaleMP ma-                                                                                                                                                                                                                                                                                                                                                                                      |     |

|            | chine for the original and optimized version                                                                                                                                                                                                                                                                                                                                                                                                    | 107 |

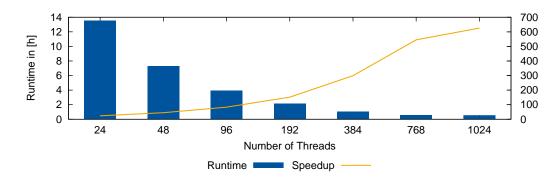

| 6.12       | Runtime and speedup of the TrajSearch code on a Numascale ma-                                                                                                                                                                                                                                                                                                                                                                                   |     |

|            | chine with up to 1024 threads                                                                                                                                                                                                                                                                                                                                                                                                                   | 110 |

## **List of Tables**

| 1.1 | Overview of the machines used during this work                                                                                                                                                                                                                    | 10       |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | Overhead in microseconds for a malloc call allocating 1MB of memory. All threads constantly allocate and free memory. Results are shown for 30, 60 and 120 threads on the Xeon Phi and 32, 64 and 128 on the HP, BCS and Altix                                    | 19       |

| 2.2 | Bandwidth reached when initializing an 2 GB array with first-touch memory placement. In brackets the speedup compared to a single thread on the same machine is shown. Results are shown for 30, 60 and 120 threads on the Xeon Phi and 32, 64 and 128 on the HP, | 20       |

| 2.3 | BCS and Altix systems                                                                                                                                                                                                                                             |          |

| 2.4 | ferent compilers                                                                                                                                                                                                                                                  | 21<br>23 |

| 3.1 | Shortest paths generated by the brute-force, greedy or Christofides algorithm                                                                                                                                                                                     | 39       |

| 3.2 | Average page access time and overhead to migrate a page in $\mu$ s on the 2-socket Westmere and 4-socket SandyBridge system                                                                                                                                       | 44       |

| 5.1 | Task generation behavior of the BOTS benchmarks and several applications from RWTH Aachen University                                                                                                                                                              | 68       |

| 5.2 | Overhead and generated amount of data for investigated tools for the Sudoku code                                                                                                                                                                                  | 83       |

| 5.3 | Fraction of tasks which have been executed locally, on the same socket or remotely for the GNU runtime system, compared to the expected ratio                                                                                                                     | 87       |

## 1 Introduction

Several programming paradigms exist for parallel programming today. Two industry standards have become the de-facto standards in high-performance computing for this purpose over the past decades, namely the Message Passing Interface (MPI) and Open Multi-Processing (OpenMP). While MPI can be used on shared and distributed memory systems, OpenMP requires a single system with a shared memory for execution. However, OpenMP allows to extend the time consuming parts of a serial program incrementally with directives for parallel execution, without the need to rewrite the overall application. MPI, in contrast, requires an explicit data distribution by the programmer and it requires to manually send messages whenever data needs to be transferred between processes. Therefore, the complete application needs to be adjusted to the distributed data layout, which requires a complete rewrite of the application code in many cases. MPI therefore is often called the "assembly language of parallel programming", as e.g. mentioned in [Mattson et al., 2004] and [Pacheco, 1996], whereas OpenMP was often found to be easier to use but it is also said to be very limited in scalability [Jost et al., 2003].

To combine the advantages of both paradigms, many approaches have been investigated to allow OpenMP programming on large core counts. One way is to couple multiple shared memory boards with a special interconnect that allows to maintain shared memory over all boards. SGI designed their proprietary NU-MAconnect for this purpose, which allows to build shared memory systems with thousands of cores. Although, SGI was one of the first and maybe the most successful vendor producing large shared memory machines in the past, other vendors provide similar solutions as well. Bull, for example, completed the development of the bull coherence switch, a chip that can be used to couple standard 4-socket servers to a larger shared memory system with up to 16 processors. Numascale is another company which developed a chip to combine several boards to a single machine. This chip can couple hundreds of boards in a 3D-torus topology, forming single systems with thousands of cores. The company ScaleMP uses a different approach to reach the same goal. Instead of providing a hardware solution to build a single machine, ScaleMP offers a virtualization software, called vSMP Foundation, to provide shared memory on a cluster of standard servers. vSMP Foundation uses the standard infiniband network of the cluster for the actual data transfers, but provides the view of a shared memory and a single operating system image to the user.

All these machines allow to use OpenMP on hundreds or thousands of cores. Although every OpenMP program can be run on these machines, the performance is often worse than expected. On standard 2- or 4-socket servers the cache coherence is typically maintained by a protocol called snooping. This implies that all changes to a cache line, i.e. writes to a memory location, are propagated to all other caches in the system. This allows to invalidate all other copies of the cache lines in the system because these copies now contain an old value. The network traffic for such a protocol increases drastically with the number of processors in the system which need to be cache coherent, because every processor has changes to communicate and needs to invalidate own copies when others change those cache lines. Therefore, snooping does not scale for larger systems. All vendors of larger systems, mentioned before, use a different protocol to connect systems in a cache coherent manner. The second protocol is a directory based cache coherence protocol. Here, the owner of a cache line has a directory with instances holding a copy of this cache line. When the cache line is changed, the owner is informed and the owner informs all instances with a copy of the cache line. This reduces the traffic substantially, because typically a cache line is now not shared by all cores in a system but only by a few cores or not at all. Such a directory based protocol allows to build large systems, but the disadvantage is that a changes to a cache line are propagated slower, since first the owner of the cache line needs to be informed and second everyone with a copy must be informed, whereas snooping directly informs everyone in one step. As I will show later in this work, this results in different characteristics of large NUMA systems compared to standard 2- or 4-socket servers. To achieve performance a programmer needs to be aware of these characteristics and must keep them into account during the parallelization of his code.

This work presents new and extends well-known methods for application tuning on shared memory machines to achieve scalability to hundreds or thousands of cores with OpenMP parallel applications. I will first characterize different large shared memory machines, like an SGI Altix Ultraviolet, a Bull Coherence Switch system and a ScaleMP machine with the use of standard benchmarks as well as self-implemented tests to investigate performance relevant parameters of these machines and I will show how this information can be used to automatically generate a machine description as it is needed in OpenMP's affinity support (i.e. a place-list). I cover standard techniques and tools as a basis before I present self implemented methods for data migration and NUMA-aware load-balancing, as well as extensions to standard performance tools which allow to detect performance issues which could not be detected before, especially when OpenMP tasks are used. Finally, ways to model OpenMP performance especially on large NUMA machines are presented and I will present a recommended workflow to optimize applications for large NUMA machines to achieve this performance.

The rest of this work is structured as follows: First I will explain types of NUMA

machines and introduce the systems used for experiments throughout this work in the rest of this chapter. Afterwards, performance characteristics of the investigated machines and different OpenMP runtime systems on these machines are evaluated and discussed in section 2, where I will also present how the gathered information can be used to set up a distance matrix as a way to describe the machine properties with respect to non-uniform memory access. I will cover general NUMA optimizations and present the OMPX library for memory placement in chapter 3, and investigate load balancing issues on large NUMA systems in chapter 4. In chapter 5 I will cover the ability of performance tools to handle OpenMP tasks and I will present extension to a performance measurement system, called Score-P, to improve the investigation of performance problems related to tasks on large SMP systems. Furthermore, I developed a performance model for OpenMP applications on NUMA systems and a workflow to optimize applications. This and two applications case studies which prove the optimizations useful on real application codes are presented in chapter 6. Finally conclusions are drawn in chapter 7.

### 1.1 Main Contributions

This work provides new contributions over state-of-the-art practices in the area or high-performance computing in the following fields.

First, as mentioned before, large shared memory machines exist from many vendors and with different underlying technical solutions. Characteristics of these different machines are investigated with the help of kernel benchmarks to classify the different architectures. Distance information of the NUMA nodes in a system are used to automatically build a place-list. A place-list is an abstract machine description used by OpenMP to support affinity. The generation of this list is left to the programmer by the OpenMP specification, so a systematic way to generate it can further ease the use of OpenMP's affinity support. Furthermore, the results of the kernel tests are used to form an easy-to-use performance model for OpenMP programs on these machines. Existing performance models nowadays are either very simple, like the roofline model [Williams et al., 2009], where peak-performance and memory bandwidth are the only restrictions for application performance, or models are extremely complicate to apply. E.g. in [Treibig and Hager, 2010 a model is presented to predict the performance of serial programs, based on an analysis of the generated assembly code and detailed hardware information about throughput and latency for all cache levels, based on processor specific vendor information. According to the authors, this is not done for parallel programs, because the transfers of cache lines cannot be predicted that accurate by looking at the assembly code only. In [Culler et al., 1993] or [Ramos and Hoefler, 2013 parallel applications are considered, but the models concentrate only on the network and only network transfer times are considered. Both models require in-depth knowledge of all transfers, which is useful in message passing applications, but most often not realistic for OpenMP programs, since data is transferred transparently by the cache coherence mechanisms of the hardware. [Calotoiu et al., 2013] presented a tool for automatic performance modeling, namely Extra-P. This tool allows to extrapolate the performance of an application runs with many cores based on a few previous measurements with smaller core counts. The tool focuses on MPI applications, but the techniques might be applied to OpenMP applications as well. However, such an approach will very likely lead to inaccurate predictions on hierarchical NUMA systems, as the small scale measurements on a few cores do not provide any reliable data to predict memory access performance outside of the local NUMA domain. The model presented here will use results from the kernel benchmarks to provide a more accurate performance estimation than the roofline model, while it will still be usable by non architecture experts and for OpenMP programs.

Second, data and thread placement are the most important factors in shared memory programming on NUMA systems. The current standard of OpenMP allows the placement of threads on places with different strategies. For the data placement no OpenMP support exists, but it is common practice to use the firsttouch data placement policy to distribute the data across NUMA nodes in the desired way. This means, that the data needs to be accessed first on the node where it should reside in memory, this can be achieved in many cases by parallel initialization with the same access pattern that is later on used during computation. If this is not sufficient for an application, e.g. because the data access pattern changes over time, like in adaptive algorithms, data migration mechanisms exist for the Linux operating system. This work will investigate the usefulness of these mechanisms on modern architectures. Furthermore, a method will be presented to achieve migration-on-next-touch in user space for the Linux operating system. This approach means that memory is migrated to the thread which uses the memory the next time. The Solaris operating system offers support for this type of migration, but for Linux no support exists so far. The advantage of this method is not that it is faster than explicit migration, but that it can be applied easier if the access pattern is unknown or hard to describe for explicit migration calls.

Third, load balancing is one of the major challenges in parallel computing in general. OpenMP provides standard methods to deal with load imbalance for unbalanced computation loops, namely dynamic or guided schedules can be applied, leading to a balanced but unpredictable and unreproducible distribution and order of the loop iterations of the parallel loop. This makes it impossible to allocate data on the right NUMA nodes in advance. This work will present a NUMA-aware scheduling mechanism, providing load balancing while still maintaining data locality where possible.

Fourth, since OpenMP version 3.0, tasks provide a different way to express parallelism in OpenMP. The concept of tasks adds an additional layer of parallelism but also of complexity to OpenMP programs. An OpenMP runtime has a lot of flexibility in the way tasks are executed. This allows a lot of optimization inside the runtime system, e.g. automatic work balancing, and for the programmer it allows to express complex parallel algorithms in a simpler way in many cases, e.g. when recursions are used. The downside for a programmer is that it is hard to analyze the performance of OpenMP task parallel programs, since the runtime system makes many decisions for the programmer. This work will investigate the behavior of different OpenMP runtime systems and analyze how tasks are handled on large NUMA machines. Based on this information, different methods to use tasks by a programmer are presented and advice is given on which methods should be used when on large NUMA machines.

Fifth, this work investigates common performance problems occurring in standard OpenMP programs in general and on large NUMA architectures in particular. The ability of performance tools to detect these problems is investigated and for issues which cannot be detected easily, methods are presented to extend performance tools to detect these issues. The problematic issues are related to OpenMP tasking, since this relatively new concept is not well supported by many performance tools. To improve this, the Score-P measurement system is used as a basis which allows to profile and trace application runs of parallel programs. For traces, a trace-to-trace converter is used which adds additional information to the trace file and runs several tests on the measured data to highlight the mentioned tasking related performance issues.

## 1.2 NUMA Architectures

All major processor vendors building chips for high-performance computing servers build so called Non-uniform Memory Access (NUMA) architectures. In these architectures a core can access all the memory in the system, but the access time differs depending on the physical location of the memory. Typically there is a part of the memory attached to every socket of the system which can be accesses faster than memory attached to remote sockets. The advantage of NUMA architectures is that the available memory bandwidth in a system is increased with the number of sockets. The disadvantage is, that a programmer needs to take the NUMA characteristics into account to achieve good performance on such a system.

A commonly used way to program such systems is to use OpenMP, which provides a high-level pragma-based way for parallel programming, which is in many cases easier to apply than distributed-memory programming. Of course a shared-memory program is limited to a single system running a single OS instance. This

is why some hardware vendors build large shared-memory machines based on specialized interconnects, like SGI builds the Altix UltraViolet systems with up to 2048 cores based on their proprietary NUMAconnect interconnect.

Besides hardware solutions to build large shared-memory machines software solutions have been investigated to allow shared memory programming on clusters. Some approaches modified the Linux kernel to achieve a Single System Image (SSI) on top of a cluster, for example MOSIX [Barak et al., 1993] or OpenMOSIX as well as Kerrighed [Morin et al., 2004] [Vallée et al., 2003]. Multi-threaded applications have not been in the focus of these projects and thus they did not turn out to be very useful for OpenMP programs. MOSIX / OpenMOSIX both only allow the migration of processes and not of threads, which makes it unsuitable for OpenMP. It has been shown that Kerrighed can run OpenMP applications employing a modified threading library [Margery et al., 2003], but this project did not progress over a proof-of-concept state allowing the execution of commercial codes. In addition, the achieved performance was not suitable for productive use. ScaleMP is the first company offering a product to couple cluster nodes into a single system. The software solution, called vSMP, allows to run a single system Linux image on an infiniband cluster. Any shared-memory program can run on these machines without recompilation.

Specifically targeting the execution of OpenMP programs on clusters has also been the focus of several research projects and even commercial products. In [Lu et al., 1998] an OpenMP implementation for the TreadMarks software has been presented, which supports a subset of the OpenMP standard. In [Sato et al., 2001] an OpenMP implementation on top of the page-based distributed shared memory (DSM) system SCASH has been presented for the Omni source-to-source translator. In this approach, all accesses to global variables are replaced by accesses into the DSM and all shared data is controlled by the DSM. Although the full OpenMP specification is implemented, support for the C++ programming language is missing. Intel's ClusterOpenMP [Hoeflinger, 2006] has been the only commercial approach for OpenMP on clusters with full support for OpenMP 2.5. An examination revealed major shortcomings in the applicability and the memory management [Terboven et al., 2008b] for real-world applications and meanwhile Intel ceased the development of this product.

## 1.3 State-of-the-art in NUMA Programming

NUMA-aware programming in OpenMP has been investigated for some time. One of the major issues which has been tackled so for is the placement of threads on the architecture. For this problem OpenMP offers support since version 3.1, which has been extended in version 4.0. Details are described in this work in chapter 3. Also

for memory placement same state-of-the-art practices have evolved, specifically the use of the first-touch memory placement policy of the OS to distribute data over the system by a parallel data initialization. In OpenMP, no support for data placement or migration exists at all. For the OpenMP tasking feature or for dynamic schedules, which offer more flexibility in terms of work balancing, no NUMA support exists at all.

Besides the functionality to program in a NUMA-aware fashion, support in performance analysis tools is also mandatory to detect and avoid certain issues. Here, some tools exist which give some information on NUMA accesses, but they are typically hard to use, since they are based on hardware counters which are extremely hardware dependent and change with every new processor generation.

In practice, even if many large NUMA systems exist, they are mostly partitioned by a batch system to run many batch jobs in parallel and only a very few user codes scale very well over a complete system. Techniques, as they will be presented in this work, are developed to optimize more user codes for large NUMA systems to make full use of these machines for a higher number of user codes.

## 1.4 Experiment Hardware

This work contains results carried out on the following architectures.

#### Westmere

This system is a Bullx B500 blade equipped with two Intel Xeon X5675 ("Westmere") processors with 6-cores each, a clock rate of 3.07 GHz and 24 GB of main memory. The Westmere system represents a standard 2-socket node which is the most commonly used node type in current clusters.

#### SandyBridge

The SandyBridge system is a 4-socket DELL M820 system equipped with Intel Xeon E5-4620 ("SandyBridge") processors running at a clock rate of 2.20 GHz. The system contains 256 GB of main memory.

#### **HP ProLiant**

The HP ProLiant DL980 G7 server used for our experiments is a single server equipped with eight Intel Xeon X6550 processors with 8 cores each. All processors

are clocked at 2 GHz and connected to each other through the Intel Quick Path interconnect. Every processor contains a memory controller attached to 32 GB of main memory, making this server a ccNUMA machine with a total of 64 cores and 256 GB of memory.

#### SGI Altix UltraViolet

The SGI Altix UV system consists of several two socket boards, each equipped with two Intel Xeon E7- 4870 10-core processors clocked at 2.4 GHz. All of these boards are connected with SGIs NUMALink interconnect into a single shared memory machine. Since on one board the cache-coherence is established directly over the QPI, whereas the NUMALink network is needed for different boards, this machine is a hierarchical NUMA machine, with different cache-coherency mechanisms on different hierarchical levels. The machine used in our tests has 2080 cores and about 2 TB of main memory. All of our tests were done on up to 16 processors during batch operation of the system. For a better comparison with the 8-core processors used in the other systems, all tests were done using only eight of the ten available cores on each socket, i.e. using up to 128 cores.

#### **BCS**

The BCS system consists of four bullx s6010 boards. Each board is equipped with four Intel Xeon X7550 processors with 8 cores each and 64 GB of main memory. The Intel Quick Path Interconnect combines the four sockets to a single system and the Bull Coherence Switch (BCS) technology is used to extents the QPI to combine four of those boards into one SMP machine with 128 cores and 256 GB of main memory. So, this system is also a hierarchical NUMA system.

#### **ScaleMP**

The ScaleMP machine investigated here consists of 16 boards, each equipped with four Intel Xeon X7550 8-core processors clocked at 2 GHz and 256 GB of main memory. The boards are connected via a 4x QDR InfiniBand network, where every board is connected via two host channel adapters. Thus, from a hardware point of view this is an ordinary (small) cluster. The innovative part of the machine is the vSMP software, which runs below the operating system and creates a single system image on top of the described hardware. The virtualization layer of the processors and the InfiniBand network is used by the vSMP software to create cache-coherency on a per page basis and to allow remote memory access between all the boards. A partition of the main memory is reserved by the vSMP software to run different caching and prefetching mechanisms automatically in the

background, as well as a page-based memory migration mechanism. These mechanisms do not only move pages on access, they can also adjust the home node of memory pages if pages are frequently used on a remote node. This is a notable difference to standard x86-based non-uniform memory architectures (NUMA), like the Altix or BCS machine, where page migration needs to be done by the user, if possible at all. From a user point of view the machine looks like a single Linux machine with 512 cores and about 3.7 TB of main memory. About 300 GB of the available memory are used by the vSMP software internally for caching. Linux sees 64 NUMA nodes, each containing about 64 GB of main memory. Due to the End Users License Agreements of ScaleMP, no absolute performance results for the ScaleMP machine may be presented here, but I will show relative improvements for different tuning steps on such a system.

#### Intel Xeon Phi

The Intel Xeon Phi coprocessor is not a NUMA machine, it is only a single chip with one memory chunk attached. The system is used for comparison to demonstrate the behavior of a non-NUMA system for the tests carried out. The Intel Xeon Phi coprocessor is based on the concepts of the Intel Architecture (IA) and provides a shared-memory many-core CPU that is packed on a PCI Express extension card. The version used here has 60 cores clocked at 1.053 GHz and offers full cache coherency across all cores with 8 GB of GDDR5 memory. A ring network connects all cores with each other and with memory and I/O devices. Every core supports 4-way Hyperthreading, which allows the system to run up to 240 threads in parallel. The comparably small amount of main memory is attached to the Xeon Phi Chip as one NUMA node. Thus, the system is a 240-way parallel system with a uniform memory architecture, which is another difference to the other machines with are large NUMA systems.

The Xeon Phi card used in this work was plugged into a host system with two Intel Xeon E5 processors. For all of our experiments we used the host system only to cross-compile the executables, which were copied and executed stand-alone on the Xeon Phi. This procedure gives us insight in the performance attributes of the chip, independent from the programming model used. Of course, comparing one extension card with complete systems is an uneven comparison, but for sure we will see standalone systems with hundreds of cores in the near future and the Phi might give evidence on the behavior of such systems.

| System      | #sockets | #cores | clock rate         | memory            | 2nd level interconnect |

|-------------|----------|--------|--------------------|-------------------|------------------------|

| Xeon Phi    | 1        | 60     | 1.0 GHz            | 8 GB              | -                      |

| Westmere    | 2        | 12     | $3.0~\mathrm{GHz}$ | 24 GB             | -                      |

| SandyBridge | 4        | 32     | $2.2~\mathrm{GHz}$ | $256~\mathrm{GB}$ | _                      |

| HP          | 8        | 64     | $2.0~\mathrm{GHz}$ | $256~\mathrm{GB}$ | _                      |

| BCS         | 16       | 128    | $2.0~\mathrm{GHz}$ | $256~\mathrm{GB}$ | Bull Coherence Switch  |

| ScaleMP     | 64       | 512    | $2.0~\mathrm{GHz}$ | 3789 GB           | Infiniband / vSMP      |

| Altix       | 208      | 2080   | $2.4~\mathrm{GHz}$ | 2048 GB           | NUMALink               |

Table 1.1: Overview of the machines used during this work.

## 2 A Benchmark-Guided Characterization of Large Shared-Memory Machines

As already mentioned before, a part of this work is to provide insights in the different types of shared-memory machines, since machine attributes have a high influence on the program's performance. In this chapter, I will show methods to investigate relevant attributes of large SMP machines with standard kernel benchmarks and self-implemented benchmarks. All tests are done on the set of shared memory machines presented in section 1.4, but the methods can easily be applied to any other machine. Since machines with uniform memory access (UMA), non uniform memory access (NUMA) and with software or hardware based multiple NUMA levels are used in these experiment, general differences between these machine types will be highlighted by these tests as well. The benchmark results are later on in this work used as basis for a machine description which can be used for OpenMP programs to improve the affinity support in section 3.2, and to formalize a performance model for OpenMP programs on NUMA systems, overcoming some of the limitations of well established performance models in section 6.2.

Benchmarks to investigate the performance of different aspects of an architecture have been developed in many different studies. Standard benchmarks to investigate the memory performance of a system are the Stream benchmark [McCalpin, 1995] and the LMBench benchmark suite [McVoy and Staelin, 1996]. For OpenMP programs the EPCC microbenchmarks [Bull, 1999], [Bull and O'Neill, 2001], [Bull et al., 2012] can be used to measure the overhead of OpenMP constructs. Furthermore, benchmark suites exist which can be used to compare the performance of architectures and OpenMP implementations for application-like kernels, e.g. the SPEC OMP benchmark suite [Aslot et al., 2001], [Müller et al., 2012] or the NAS parallel benchmarks [Bailey et al., 1991]. For OpenMP programs using the new tasking paradigm the Barcelona OpenMP Task Suite (BOTS) [Duran et al., 2009] can be used.

All of these benchmarks come with published performance results on different architectures, but no study has been made to compare the performance of large SMP machines so far. Furthermore, I want to investigate different aspects of the machine and not improve the benchmarks themselves in this work. So, I used some

of the benchmarks mentioned, like the EPCC microbenchmark or developed own tests for specific characteristics of the test machines. The rest of this chapter will show that hardware awareness is important on large NUMA systems and which parts of an application are mostly influenced by these hardware characteristics. Furthermore, it shows differences and similarities of the machines and OpenMP runtime systems on these machines.

Parts of the results and methods presented in this chapter have been published before. In [Schmidl et al., 2010a], [Schmidl et al., 2010b] and [Berr et al., 2012] kernel tests on a ScaleMP system similar to results presented here have been reported. Furthermore, the performance of Xeon Phi systems in comparison to hierarchical NUMA systems like the BCS machine were presented in [Cramer et al., 2012] and [Schmidl et al., 2013b]. Finally, a study comparing different NUMA systems as they are used here was published at IWOMP 2013 in [Schmidl et al., 2013a].

## 2.1 Memory Performance

One of the big advantages of NUMA systems compared to UMA machines is the fact that every processor has its own memory and that this memory is directly connected to the processor. Thus, the available amount of main memory and the available bandwidth increases with the number of sockets in such a system. Since many scientific applications are memory bound, a high overall memory bandwidth is important for many applications. Therefore, I will first investigate the main memory bandwidth of the target platforms of this work.

## 2.1.1 Serial Memory Performance

The memory bandwidth and latency on a NUMA system is highly influenced by the physical location of the memory in relation to the processor core accessing the memory. As described in section 1.4, the investigated machines have a uniform memory access (Xeon Phi), a non uniform memory access with one level (Westmere, HP) or with two levels (Altix, BCS, ScaleMP). First, I implemented a serial memory bandwidth test which reads or writes an data array 1000 times and computes the reached memory bandwidth. The test can be used to measure the reachable bandwidth for a single thread on different systems. The command line tool numact1, provided by the Linux operating system, can be used to set the core and also the memory node used for the benchmark. For example, the bandwidth a thread running on core 0 can reach when data on the fourth NUMA node is accessed can be measured by the following command:

Figure 2.1: Read Bandwidth in GB/s reached for different NUMA levels measured on the Xeon Phi, Westmere, HP, BCS, Altix and ScaleMP system for different memory footprints.

numactl --membind=4 --physcpubind=0 ./bandwidth\_test.exe

In this way I measured the reachable bandwidth for three different scenarios, if applicable on the specific machine:

- (i) **local:** Here the core and the memory belong to the same socket in the system.

- (ii) **remote level 1:** Here the memory of a remote socket on the same physical board is used. To access the data the QPI can be used by the hardware.

- (iii) **remote level 2:** Here the memory of a remote socket on a different physical board is used. To access the data the second level interconnect of the system (BCS, Numalink or vSMP software + infiniband) is needed.

The results of my tests are shown in figure 2.1 for the read bandwidth. Results for the write bandwidth look similar and are therefore omitted. On all machines, a typical cache behavior can be seen. For small data sizes the access is fast, since the data fits into the caches and is not loaded from memory for all but the first of the 1000 accesses. When the size of the last level cache is exceeded, the performance drops down to the memory bandwidth and stays pretty much constant at this level in all measured cases. The differences in the local performance of the systems is due to different processors, clock speed and memory dims. But it can be observed, that the bandwidth for a remote level 1 access is about 25% to 30% slower than a local access. A remote level 2 access in contrast is about 75% slower on the BCS system and 85% on the Altix machine. On the ScaleMP machine no difference can be observed between remote level 1 and 2, because the software caches all accesses internally and serves the requests from the board local software cache.

Overall, these tests show that the memory bandwidth highly depends of the location of the data in the NUMA system, as expected. Moreover, the tests also show, that on hierarchical NUMA machines, the board local accesses are not penalized by the fact that the systems have a second level interconnect. So, for a programmer it is important to realize that remote memory is not equal on these hierarchical machines. The different levels should be taken into account.

## 2.1.2 Parallel Memory Bandwidth

Since parallel applications in high-performance computing typically use all cores of a system at a time the total bandwidth of a system is more important than the serial bandwidth investigated so far. Thus, I modified the benchmark used in section 2.1.1 to work with several threads on an array and measured the read and write bandwidth. All threads are working on different pieces of the array, so there are no conflicts or synchronization constructs among threads. Threads were

placed in a close binding using the OMP\_PROC\_BIND environment variable provided by OpenMP for thread placement. The close strategy instructs the runtime to fill up all cores and hyperthreads of one socket before the next socket is used.

Figure 2.2: Parallel read and write bandwidth on the Westmere, HP, Altix, BCS and Xeon Phi systems for an increasing number of threads.

Figure 2.2 shows the read and write bandwidth for an increasing number of threads on the different platforms for a memory footprint of 16 MB per thread. (Results for the ScaleMP machine are omitted because ScaleMP's EULA does not allow to publish absolute performance results.) On the Intel Xeon Phi machine the maximum memory bandwidth of about 130 GB/s for reading and 60 GB/s for writing can be achieved with about 120 threads. Beyond this, the bandwidth stagnates. This behavior is typical for UMA systems like the Xeon Phi. The bandwidth rises at the beginning, until enough threads are started to consume the total available bandwidth of the memory controller. With more threads the bandwidth does not raise any further, which leads to the flattened curve in figure 2.2.

On the NUMA systems the bandwidth rises with the number of sockets used and does not stagnate at all. Of course, this is due to the increasing number of memory controllers and memory banks for a larger number of threads. However, it also indicates that the cache coherence on all systems for mostly local memory accesses is low and does not prohibit scaling on such systems.

On all systems the read bandwidth is higher than the write bandwidth, since a write requires a prior read of a cache line which leads to half the bandwidth of a write operation compared to a read operation.

#### 2.1.3 memory\_go\_around

The parallel bandwidth investigated so far is the optimal bandwidth which can be reached on a system. All threads were working on distinct pieces of a shared array which was distributed across the NUMA nodes of the system. Thereby it can be achieved that nearly all accesses to data are served by the local memory of a processor. This is a typical case in dense linear algebra, where matrices and vectors can easily be split between threads, or in embarrassingly parallel algorithms were often all threads work on their own data. However, there also exist many algorithms where some data sharing is required. Here, a certain amount of remote accesses cannot be avoided. To investigate the drop in the available memory bandwidth with remote accesses, a different benchmark is used. The unpublished benchmark was originally designed by Dieter an Mey and only slightly modified for this work to contain automatic thread placement. The benchmark increases the number of remote accesses from step to step and measures the effect on the memory bandwidth reached.

Figure 2.3: The memory\_go\_around benchmark works in n+1 steps. In the first step the memory of the right neighbour is used to measure the bandwidth, in the next step the memory of the next neighbour and so on. This increases the distance between thread and memory in every step, until half of the steps are done, then the distance decreases until it reaches zero in the last step.

The benchmark is called memory\_go\_around and it was first presented in [Schmidl et al., 2013a]. In the first step, every thread initializes its chunk of data and measures the memory bandwidth to access this chunk. This step is similar to the parallel bandwidth test used in section 2.1.2. In the next step, all threads work on the data of their right neighbor, so thread t works on memory initialized by thread  $(t+1) \mod (n)$ , where n is the total number of threads used, as exemplified in figure 2.3. Threads are placed in a way that neighboring threads run as close to

each other as possible. So, I first fill up all hyperthreads of a core, than all cores of a processor and then all processors of a board and all boards in a system. So, there is a high chance that neighboring threads run on the same NUMA node or board. Only the one thread running on the last core of a socket or board will work on data on the next socket or board. In the next steps the distance is increased, since all threads t work on the data of thread  $(t+s) \mod (n)$  in step s. Hence, the number of remote memory accesses rises for the first n/2 steps. Then the number shrinks again until in step n-1 every thread works on the memory of the left neighbor and in step n again on its own local memory.

Figure 2.4: Bandwidth measured with the memory\_go\_around benchmark for n+1 steps with n threads on the Westmere, HP, Altix, BCS, and Xeon Phi system.

Figure 2.4 shows the result for 24 Threads on the Westmere, 64 Threads on the HP, 120 threads on the Xeon Phi and for 128 threads on the Altix and BCS machine. The Xeon Phi machine shows the typical behavior of a UMA system. Since only one memory location exists in the system, it does not matter at all, which thread initialized the data and a constant bandwidth of about 130 GB/s is reached in all turns.

On the other machines the bandwidth declines for the first half of the steps and then rises up again. Of course this is related to the increasing number of remote accesses and the increasing distance between these accesses. On the 2-socket Westmere system, which represents the most typical architecture in HPC, the performance drops rather slow in the first 12 turns until it reaches the minimum of about 50% of the starting performance. On the HP system, the performance

drops down from about 120 to 60 GB/s, so also here about 50% of the performance are still reached, even when all accesses are remote accesses across the whole system. But the curve drops faster than on the Westmere system.

On the Altix and BCS machines the drop is from about 250 to 18 or 8 GB/s which is 6% or 3% of the available maximum bandwidth. Furthermore, the performance drops down very fast starting at turn 1. The performance penalty is much more severe on the hierarchical systems and already reached for a smaller number of remote accesses. This makes it much more important to minimize remote accesses compared to the standard 2-socket Westmere machine, for example. However, if an application does not require a lot of data sharing between the threads, proper data placement or migration can avoid these problems, as I will show in chapter 3.

### 2.1.4 Data Management