# "Stochastic Approaches for Speeding-Up the Analysis of the Propagation of Hardware-Induced Errors and Characterization of System-Level Mitigation Schemes in Digital Communication Systems"

Der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen vorgelegte Dissertation zur Erlangung des akademischen Grades einer Doktorin der Ingenieurwissenschaften

vorgelegt von

Diplom-Ingenieurin Georgia Psychou, M.Sc., aus Tripoli, Griechenland

Berichter: Universitätsprofessor Dr.-Ing. Tobias G. Noll

Universitätsprofessor Dr.-Ing. Holger Blume

Universitätsprofessor Dr.-Ing. Tobias Gemmeke

Tag der mündlichen Prüfung: 29. September 2017

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

# Acknowledgements

The author would like to acknowledge the support of former IMEC Netherlands researchers Jos Huisken and Dr. Tobias Gemmeke, that they provided, during their employment in IMEC Netherlands. During that time, there have been regular discussions on the progress and direction of the work and they offered valuable suggestions, which have made a number of publications and this work possible.

The research results published in this thesis have been in part published earlier in international peer-reviewed conferences and journals. Text, figures and tables are taken, in some cases, one-to-one from such own references.

# Abstract

Today's nano-scale technology nodes are bringing reliability concerns back to the center stage of digital system design because of issues, like process variability, noise effects, radiation particles, as well as increasing variability at run time. Alleviations of these effects can become potentially very costly and the benefits of technology scaling can be significantly reduced or even lost. In order to build more robust digital systems, initially, their behavior in the presence of hardware-induced bit errors must be analyzed. In many systems, certain types of errors can be tolerated. These cases can be revealed through such an analysis. Overhead can be avoided and remedy measures can be applied only when needed. Communication systems are an interesting domain for such explorations: First, they have high societal relevance due to their ubiquity. Second, they can potentially tolerate hardware-induced errors due to their built-in redundancy present to cope with channel noise. This work focuses on analyzing the impact of such errors on the behavior of communication systems. Typically, error propagation studies are performed through time-consuming fault injection campaigns. These approaches do not scale well with growing system sizes.

Stochastic experiments allow a more time-efficient approach. On top, breaking down the system into subsystems and propagating error statistics through each of these subsystems further improves the speed-up and flexibility in the reliability evaluation of complex systems. As an initial step in this thesis, statistical moments are propagated through the signal flows of Linear-Time-Invariant (LTI) blocks. Such a scheme, although fast, can only be applied in the case that the signal lacks autocorrelation. However, autocorrelation can be introduced in the signal due to various reasons, like by signal processing blocks. In that case, other approaches are available to reduce the computational cost of the necessary (repetitive) experiments, like the Principal Component Analysis (PCA). Benefits of such a technique depend on several parameters and, therefore, a more broadly usable technique is required. To address this need, a framework is proposed that exploits the repetitive nature of fault injection experiments for speed-up in LTI blocks. Two cases are distinguished: One, in which all operators of the LTI block act in a linear time-invariant way, and one, in which non-linear operations due to finite wordlengths are present. To complement the subject matter, the broad range of hardware-based mitigation techniques at the higher system level are explored and characterized. In this way, the main properties of each mitigation category are identified and, therefore, suitable choices can be made according to the application needs.

# Contents

| $\mathbf{A}$ | ckno         | wledgements                                                        | :  |

|--------------|--------------|--------------------------------------------------------------------|----|

| $\mathbf{A}$ | Abstract     |                                                                    |    |

| 1            | Introduction |                                                                    |    |

|              | 1.1          | Thesis context and contributions                                   | Ę  |

|              | 1.2          | Thesis outline                                                     | 8  |

| 2            | Bac          | ekground and Context                                               | g  |

|              | 2.1          | Outline                                                            | Ĉ  |

|              | 2.2          | Target systems and random processes                                | Ĉ  |

|              |              | 2.2.1 Target systems characteristics                               | Ĝ  |

|              |              | 2.2.2 Relevant terms from statistics and probability theory        | 12 |

|              | 2.3          | Error injection and propagation studies                            | 13 |

|              |              | 2.3.1 Error injection                                              | 14 |

|              |              | 2.3.2 Error propagation                                            | 16 |

|              | 2.4          | Framework overview                                                 | 19 |

|              | 2.5          | Correlation between the error and error-free signal and comparison |    |

|              |              | with noise sources                                                 | 21 |

|              | 2.6          | Summary and link to next chapter                                   | 26 |

| 3            | Pro          | pagation of Corrupted, Uncorrelated Signal                         | 27 |

|              | 3.1          | Outline                                                            | 27 |

|              | 3.2          | Motivation and preliminaries                                       | 27 |

|              |              | 3.2.1 Statistical characteristics of the considered signal         | 28 |

|              |              | 3.2.2 Effects of error injection on Gaussian PMFs                  | 29 |

|              |              | 3.2.3 Linear transformation of normal random variables             | 31 |

|              | 3.3          | Propagating the corrupted signal using statistical moments         | 32 |

|   |                | 3.3.1  | Set-up and observation                                                                                  | 32 |

|---|----------------|--------|---------------------------------------------------------------------------------------------------------|----|

|   |                | 3.3.2  | Modeling approach                                                                                       | 36 |

|   | 3.4            | Exper  | imental results and related work discussion                                                             | 38 |

|   |                | 3.4.1  | Experimental set-up                                                                                     | 38 |

|   |                | 3.4.2  | Results                                                                                                 | 39 |

|   |                | 3.4.3  | Related work                                                                                            | 40 |

|   | 3.5            | Limita | ations with using the statistical moments                                                               | 42 |

|   |                | 3.5.1  | Propagating the corrupted signal through LTI blocks                                                     | 42 |

|   |                | 3.5.2  | Additional related work                                                                                 | 52 |

|   | 3.6            | Summ   | ary and link to next chapter                                                                            | 52 |

| 4 | $\mathbf{Pro}$ | pagati | on of Corrupted, Autocorrelated Signal                                                                  | 53 |

|   | 4.1            | Outlin | ıe                                                                                                      | 53 |

|   | 4.2            | Motiva | ation and preliminaries                                                                                 | 53 |

|   |                | 4.2.1  | PCA steps and dimensionality reduction                                                                  | 55 |

|   | 4.3            | Propa  | gating the corrupted signal using PCA                                                                   | 57 |

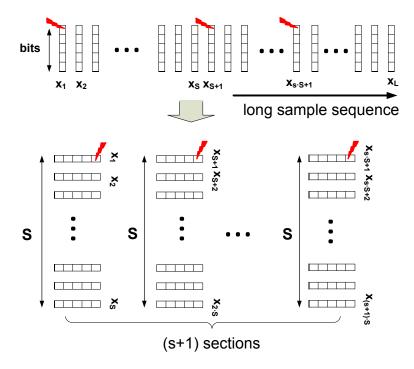

|   |                | 4.3.1  | Data organization for injection experiments                                                             | 57 |

|   |                | 4.3.2  | Illustration of the approach                                                                            | 61 |

|   | 4.4            |        | s and limitations with using the PCA for speeding-up the gation of the corrupted, autocorrelated signal | 66 |

|   | 4.5            | Summ   | ary and link to next chapter                                                                            | 69 |

| 5 | $\mathbf{Pro}$ | pagati | on of Corrupted, Generic Signal                                                                         | 71 |

|   | 5.1            | Outlin | e                                                                                                       | 71 |

|   | 5.2            | Motiva | ation and preliminaries                                                                                 | 71 |

|   |                | 5.2.1  | Effect of finite wordlengths on error propagation                                                       | 72 |

|   | 5.3            | Error  | propagation approach                                                                                    | 74 |

|   |                | 5.3.1  | Error separation: propagation without finite wordlength effects                                         | 74 |

|   |                | 5.3.2  | Error-free terms reuse: propagation combined with finite wordlength effects                             | 75 |

|   |                | 5.3.3  | Reduction of computational complexity                                                                   | 77 |

|   | 5.4            | Result | s                                                                                                       | 80 |

|   |                | 5.4.1  | Set-up                                                                                                  | 80 |

|   |                | 5.4.2  | Without non-linear effects                                                                              | 81 |

|   |                | 5.4.3  | Including non-linear effects                                                                            | 81 |

|   | 5.5            | Summ   | ary and link to next chapter                                                                            | Ω1 |

| 6             |              |         | cation of Hardware-Based Resilience Techniques at t  |   | 0 = |

|---------------|--------------|---------|------------------------------------------------------|---|-----|

|               | Hig          | ner A   | bstraction of Digital Systems                        | , | 85  |

|               | 6.1          | Outlir  | ne                                                   |   | 85  |

|               | 6.2          | Introd  | $\operatorname{luction}$                             |   | 85  |

|               | 6.3          | Conte   | ext and useful terminology                           |   | 86  |

|               |              | 6.3.1   | Resilient digital system design                      |   | 86  |

|               |              | 6.3.2   | Computing terminology                                |   | 86  |

|               |              | 6.3.3   | Rationale of the classification and its presentation | • | 87  |

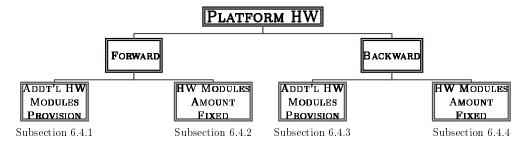

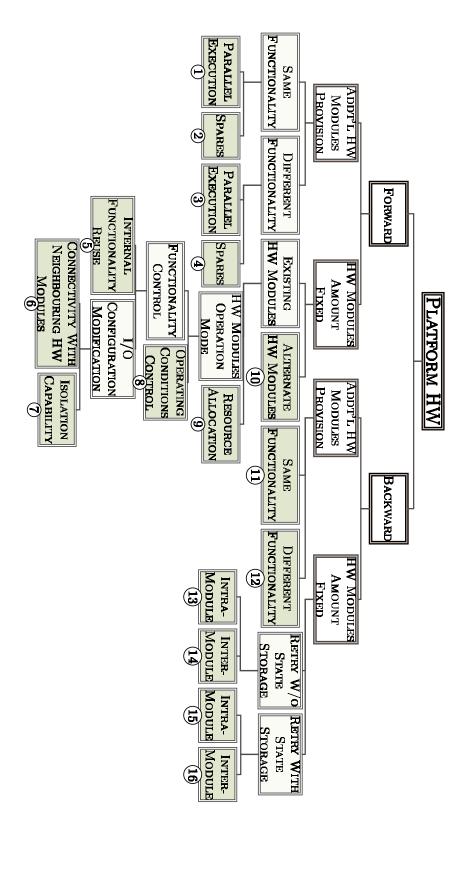

|               | 6.4          | Platfo  | orm hardware mitigation techniques                   | • | 88  |

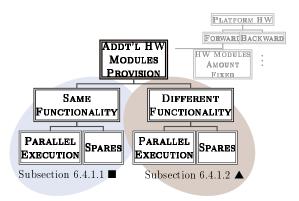

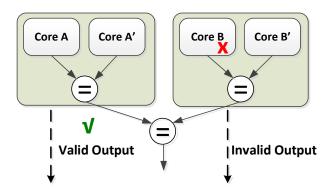

|               |              | 6.4.1   | Forward execution - Additional HW modules provision  | • | 89  |

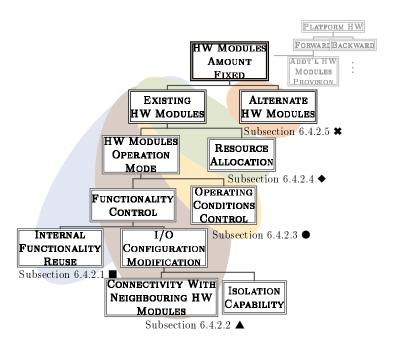

|               |              | 6.4.2   | Forward execution - HW modules amount fixed          | • | 93  |

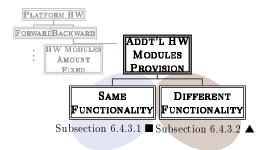

|               |              | 6.4.3   | Backward execution - Additional HW modules provision |   | 97  |

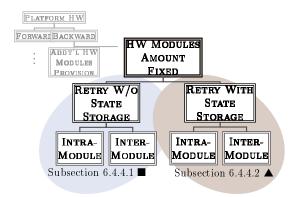

|               |              | 6.4.4   | Backward execution - HW modules amount fixed         |   | 98  |

|               |              | 6.4.5   | Overall platform hardware classification             | 1 | 02  |

|               | 6.5          | Summ    | nary                                                 | 1 | .02 |

| 7             | Cor          | ıclusio | ns                                                   | 1 | 05  |

| Li            | st of        | Publi   | cations                                              | 1 | 07  |

| $\mathbf{Li}$ | ${ m st}$ of | Terms   | s and Symbols                                        | 1 | 13  |

# List of Figures

| 1.1  | Thesis focus within the reliability assessment and mitigation flow                                                     | 6  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Detection operation in binary baseband communication system                                                            | 10 |

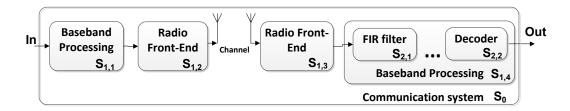

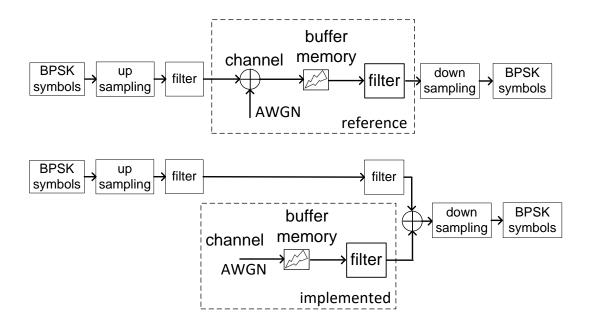

| 2.2  | Example of BPSK-based communication line                                                                               | 15 |

| 2.3  | Both signal values change by the same magnitude but in different directions leading to different amplitudes            | 16 |

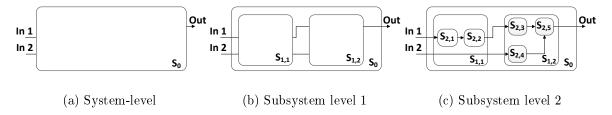

| 2.4  | Views of the same system at different abstractions                                                                     | 17 |

| 2.5  | Views of the error injection and propagation in a system at different abstractions                                     | 17 |

| 2.6  | Example of splitting a communication system into subsystems                                                            | 18 |

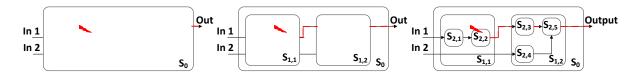

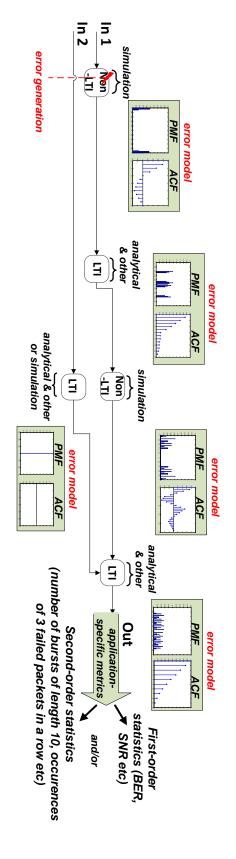

| 2.7  | Error signal generation and propagation through the system blocks using a mixture of techniques                        | 20 |

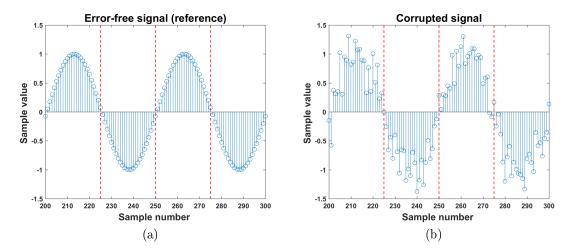

| 2.8  | Two periods of the error-free (a) and the corrupted-by-channel-noise (b) sinusoidal signal                             | 22 |

| 2.9  | Channel-induced error signal (a) modeled and (b) resulting after the interaction with the error-free sinusoidal signal | 22 |

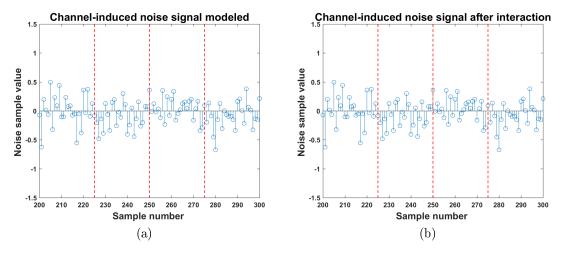

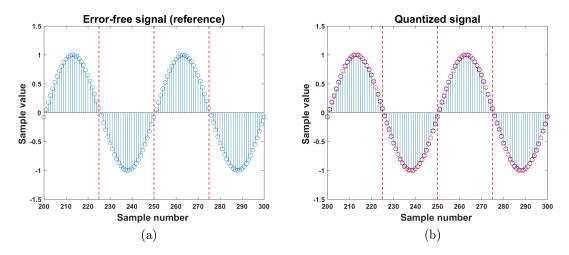

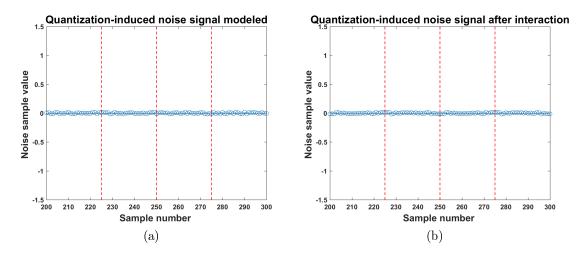

| 2.10 | Two periods of the non-quantized (a) and the quantized (b) sinusoidal signal                                           | 23 |

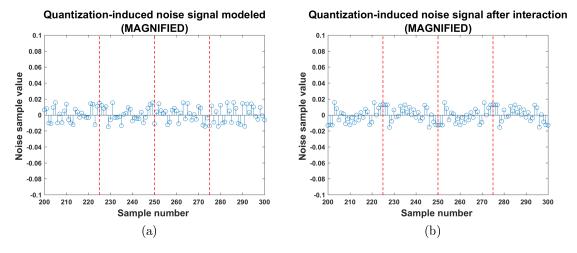

| 2.11 | Quantization noise signal (a) modeled and (b) resulting after the interaction with the error-free sinusoidal signal    | 24 |

| 2.12 | Quantization noise signal (a) modeled and (b) resulting after the interaction with the error-free sinusoidal signal    | 24 |

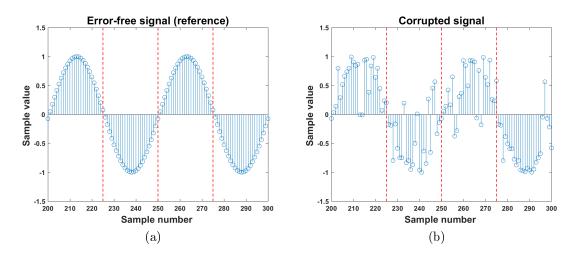

| 2.13 | Two periods of the error-free (a) and the corrupted-by-bit-errors (b) sinusoidal signal                                | 25 |

| 2.14 | Bit-flip signal (a) and error signal (b) $\hdots$                                                                      | 26 |

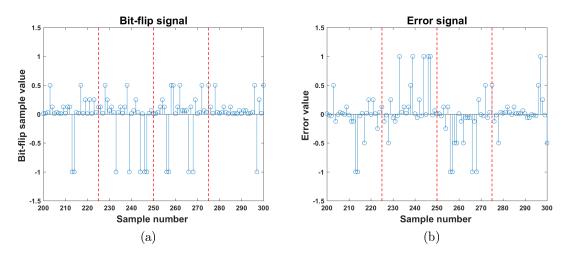

| 3.1  | Bit-flip samples PMF and effect of single bit-flips on signal PMF                                                      | 29 |

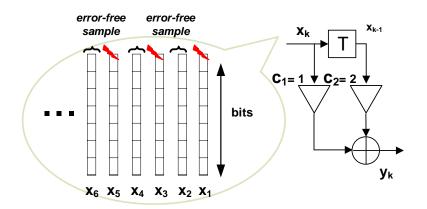

| 3.2  | Error injection in simple signal-flow (2-tap FIR filter)                                                               | 33 |

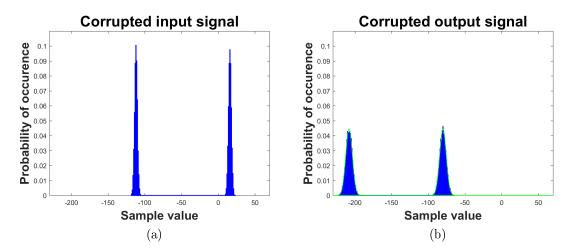

| 3.3  | PMF at the filter input and output when $\nu_f = 7$ is corrupted at the input (2- $tap$ filter)                        | 34 |

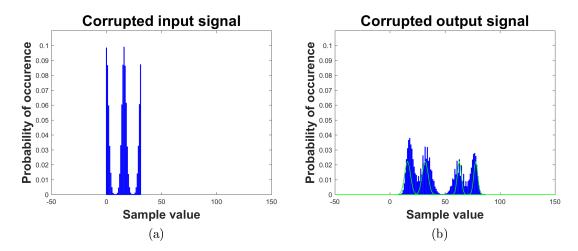

| 3.4  | PMF at the filter input and output when $\nu_f = 4$ is corrupted at the input (2-tap filter)                                                                 | 36 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | PMF at the filter input and output when $\nu_f = 4$ is corrupted at the input (5-tap filter)                                                                 | 36 |

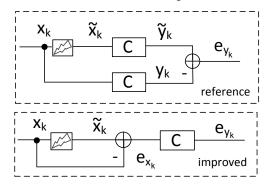

| 3.6  | Illustration of reference set-up vs. the implemented set-up to efficiently propagate bit-errors on the noise distribution through the filter at the receiver | 39 |

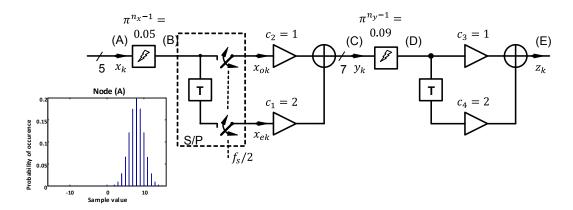

| 3.7  | Data path 1                                                                                                                                                  | 42 |

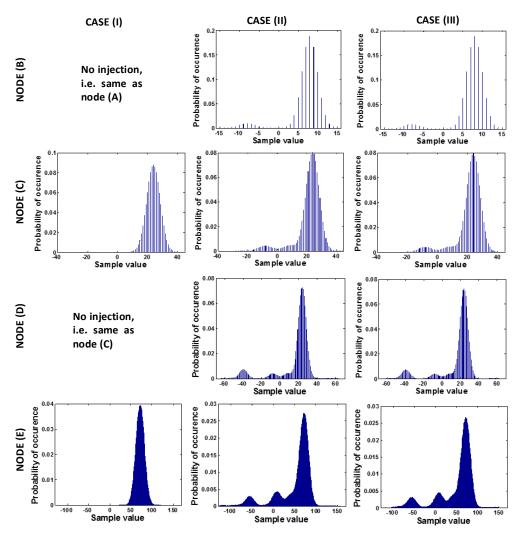

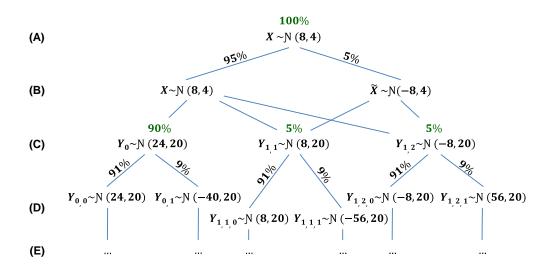

| 3.8  | PMFs of the signal at the different nodes of the data path $1 \dots \dots$                                                                                   | 43 |

| 3.9  | Creation of Gaussian components at data path 1                                                                                                               | 45 |

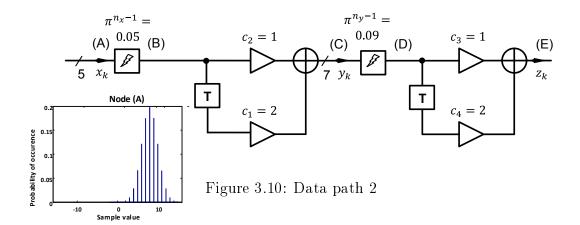

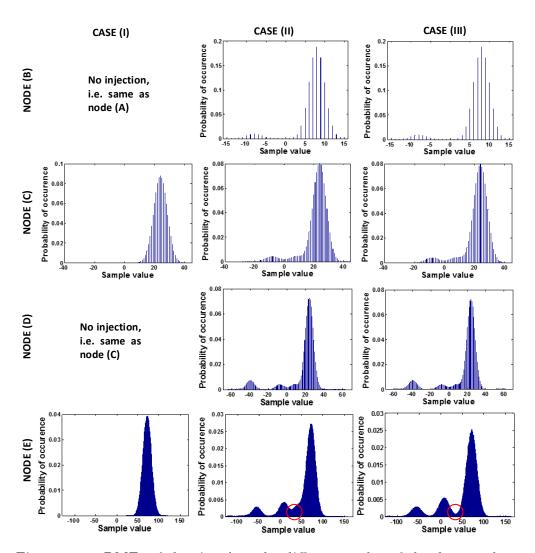

| 3.10 | Data path 2                                                                                                                                                  | 46 |

| 3.11 | PMFs of the signal at the different nodes of the data path $2 \dots \dots$                                                                                   | 47 |

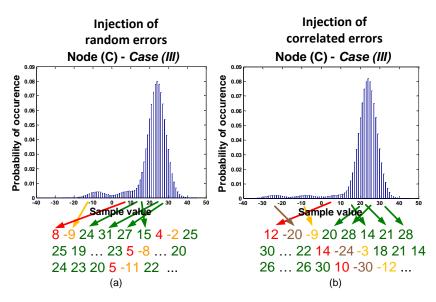

| 3.12 | Internal correlation due to the filter in the first section of data path 2                                                                                   | 48 |

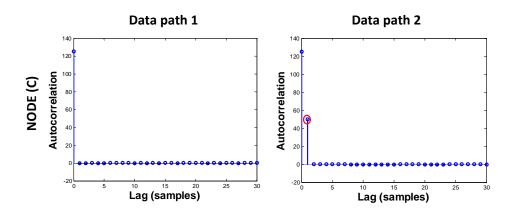

| 3.13 | ACF plots at node (C) for data path 1 and 2                                                                                                                  | 49 |

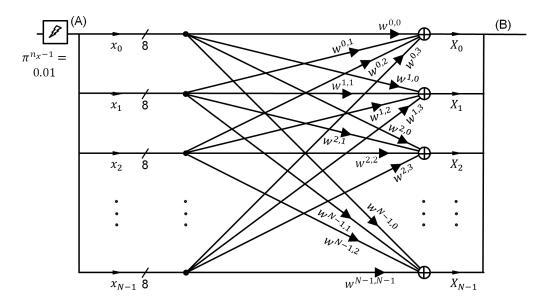

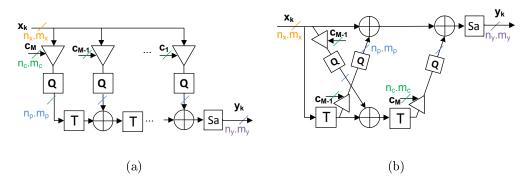

| 3.14 | DFT signal flow                                                                                                                                              | 50 |

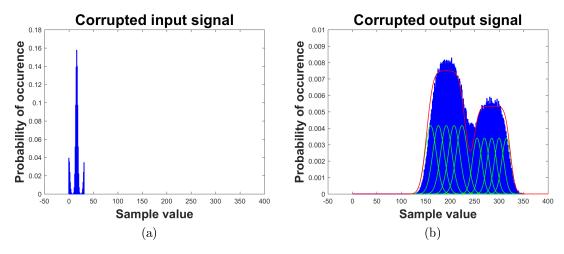

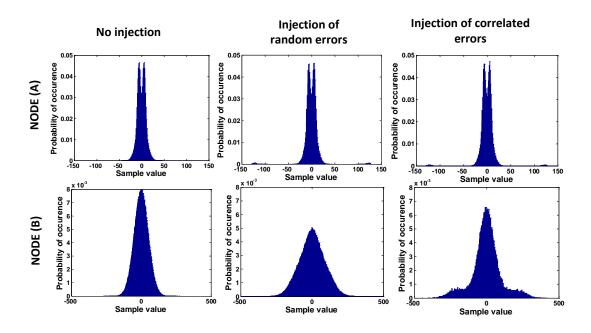

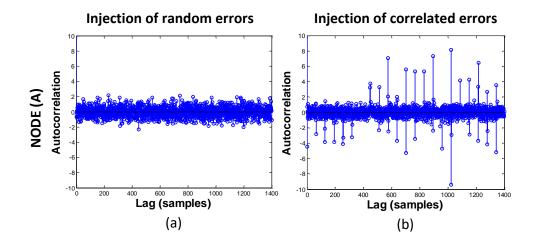

| 3.15 | Input (node (A)) and output (node (B)) PMF after injection experiments in DFT block                                                                          | 51 |

| 3.16 | ACF plots at node (A) of the DFT block                                                                                                                       | 51 |

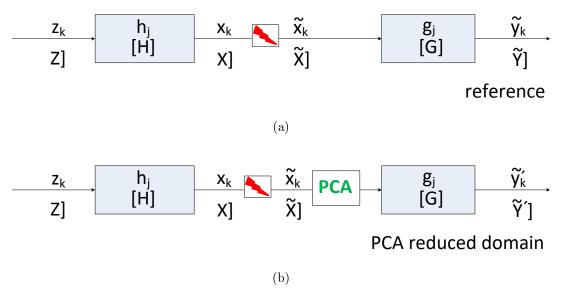

| 4.1  | Set-up for propagating the corrupted, autocorrelated signal through the $G$ operator in the reference domain (a) and in the reduced PCA domain (b)           | 54 |

| 4.2  | Modified injection rate in order to speed-up the error injection campaign                                                                                    | 58 |

| 4.3  | Filter output when a single error sample is placed at the input                                                                                              | 59 |

| 4.4  | A long sample sequence is re-organized into sections of length $S$                                                                                           | 60 |

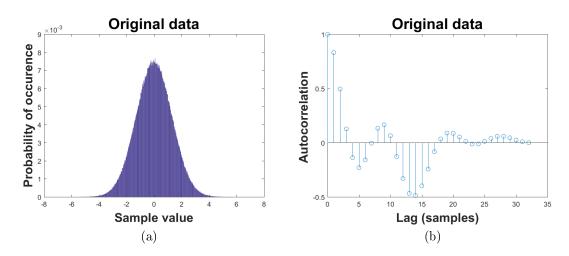

| 4.5  | PMF (a) and ACF (b) plot of the original autocorrelated signal                                                                                               | 63 |

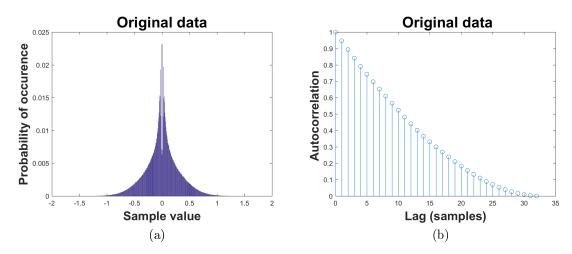

| 4.6  | PMF (a) and ACF (b) plot of the autocorrelated signal after truncation (10 dimensions kept)                                                                  | 64 |

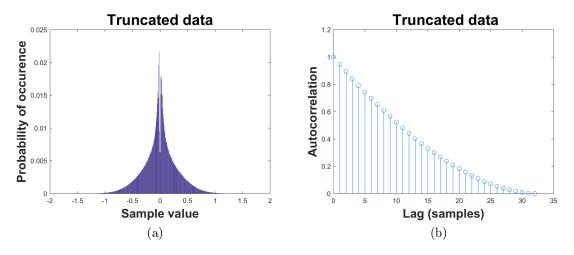

| 4.7  | PMF (a) and ACF (b) plot of the reference corrupted signal $\widetilde{Y}$                                                                                   | 65 |

| 4.8  | PMF (a) and ACF (b) plot of the re-projected (from PCA) corrupted signal $Y = \widetilde{Y}$                                                                 | 65 |

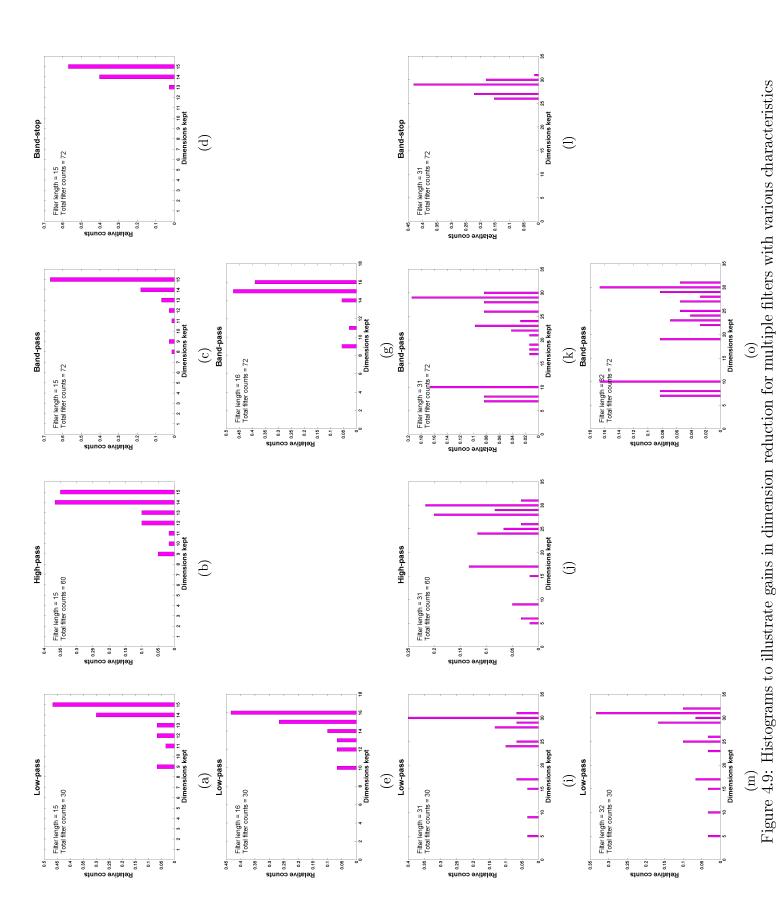

| 4.9  | Histograms to illustrate gains in dimension reduction for multiple filters with various characteristics                                                      | 67 |

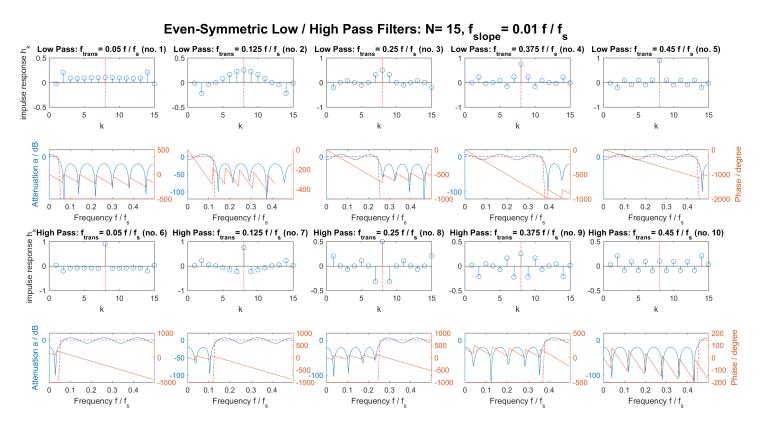

| 4.10 | Impulse and frequency responses of 5 representative low-pass filters (two upper rows) and 5 representative high-pass filters (two lower rows).               | 68 |

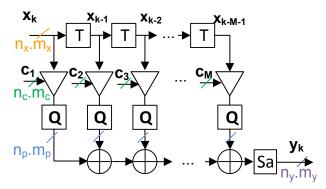

| 5.1  | An example of non-linear operations due to the finite wordlengths in a direct-form filter                                                                    | 72 |

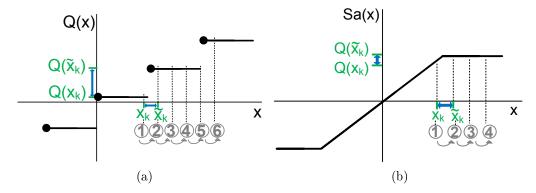

| 5.2  | on error values                                                                                | 74  |

|------|------------------------------------------------------------------------------------------------|-----|

| 5.3  | Two functionally equivalent approaches to calculate the error signal at the output             | 75  |

| 5.4  | SFGs for transposed and lattice (only 2 stages) filters                                        | 79  |

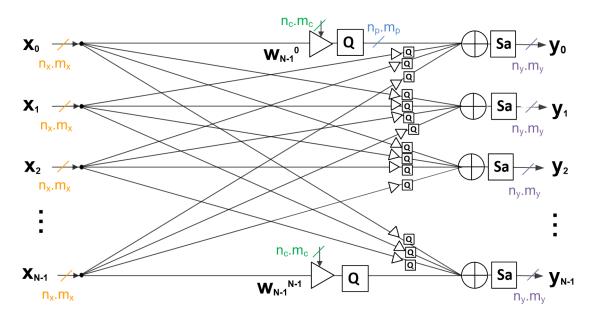

| 5.5  | SFG for a DFT block of length $N$                                                              | 79  |

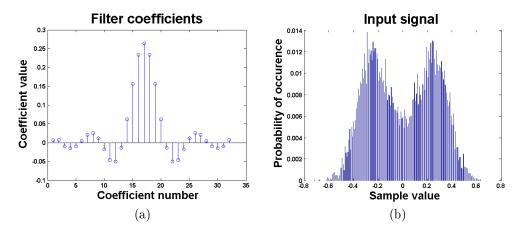

| 5.6  | Coefficients for the 32-tap filter and PMF of the input signal                                 | 80  |

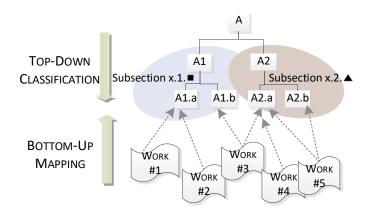

| 6.1  | Top down splitting to create the classification tree and mapping of the related work           | 87  |

| 6.2  | Basic classification $^1$ for techniques at the platform $HW \ldots \ldots$                    | 89  |

| 6.3  | Classification for forward techniques that require additional HW modules                       | 90  |

| 6.4  | Lockstep execution in a pair-and-spare structure                                               | 91  |

| 6.5  | Read out (7,4) Hamming codeword and syndrome generation for zero and one error with correction | 93  |

| 6.6  | Classification for forward techniques that keep the amount of HW modules fixed                 | 94  |

| 6.7  | Classification for backward techniques that require the provision of additional HW modules     | 97  |

| 6.8  | Classification for backward techniques that reuse existing HW modules                          | 98  |

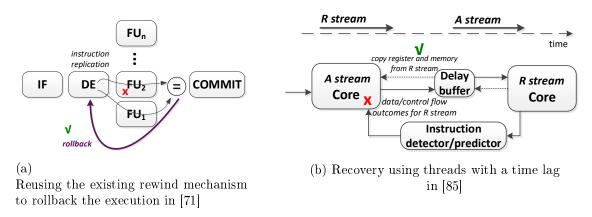

| 6.9  | Illustration of concepts in the platform-HW $backward$ category 1                              | 00  |

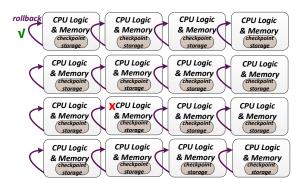

| 6.10 | A local error can trigger all the CMP cores to roll-back in global checkpointing schemes       | 101 |

| 6.11 | Overall proposed classification for techniques at the platform HW 1                            | .03 |

The boxes in the classification figures include hyperlinks to the text. By clicking on each of the boxes, the reader will be transferred to the corresponding section in the text.

# List of Tables

| 3.1 | Propagation of distribution $\mathcal{N}(16,2)$ through 2-tap FIR filter when $\nu_f = 7$ is flipped          | 3  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Propagation of distribution $\mathcal{N}(16,2)$ through 2-tap FIR filter when $\nu_f = 4$ is flipped          | 3  |

| 3.3 | Comparison for 16-, 32-, 64-tap filter (input signal: $\mu$ =0, $\sigma$ =0.562)                              | 4  |

| 3.4 | Skewness and kurtosis at the DFT output                                                                       | 49 |

| 4.1 | Parameters used in the current illustration                                                                   | 6  |

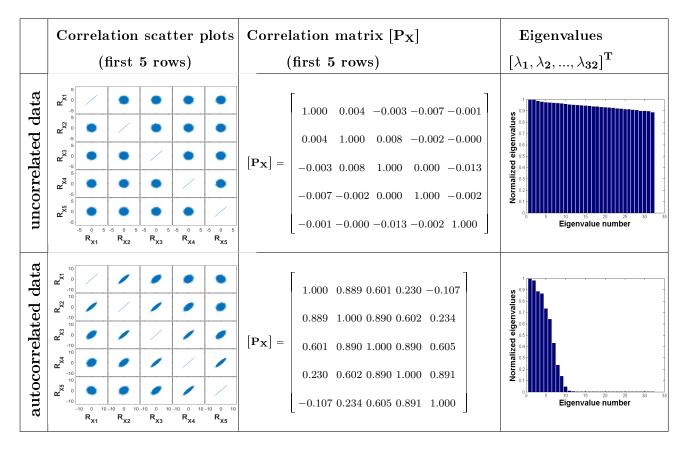

| 4.2 | Correlation among first 5 rows and eigenvalues for uncorrelated and autocorrelated data                       | 6  |

| 4.3 | Computational cost for filtering (through filter 2) the autocorrelated data (autocorrelated through filter 1) | 6  |

| 5.1 | A small illustration of the effect of quantization on error propagation                                       | 7  |

| 5.2 | Results for 32-tap direct-form filter under different input wordlengths without non-linear effects            | 8  |

| 5.3 | Results for 8-bit input wordlength under different direct-form filter lengths without non-linear effects      | 8  |

| 5.4 | Erroneous (non-masked) sample counts for 32-tap direct-form filter .                                          | 8  |

| 5.5 | Results for 32-tap direct-form filter under different input wordlengths with non-linear effects               | 8  |

| 5.6 | Results for 8-bit input wordlength under different direct-form filter lengths with non-linear effects         | 8  |

| 5.7 | Results for 16-bit input wordlength under different all-zero lattice filter lengths with non-linear effects   | 83 |

| 5.8 | Results for 16-bit input wordlength under different DFT block lengths with non-linear effects                 | 8  |

| 7.1 | LTI Processing of Stationary Random Process in the Principle Component Analysis (PCA) Domain                  | 10 |

| 7.2 | Trade-offs in HW-based resilience techniques-Part 1                                                           |    |

|     | -                                                                                                             |    |

| 7.3 | Trade-offs in HW-based resilience techniques-Part 2 | . 111 |

|-----|-----------------------------------------------------|-------|

| 7.4 | Trade-offs in HW-based resilience techniques-Part 3 | . 112 |

# Chapter 1

# Introduction

The early concerns of John von Neumann [91] regarding building reliable computing entities out of unreliable components were largely forgotten with the gradual replacement of vacuum tubes by transistors and the following high-scale transistor integration [58]. Now, after some decades, reliability has come back to the forefront in the context of modern CMOS technology. The current reliability concerns originate from mechanisms that occur both during the manufacturing process and during the system's operational lifetime. The anomalous physical conditions that are created from these effects are called **faults**. Such anomalous cases include (permanent) physical defects or (temporal) deviations of physical properties. Typically, in CMOS circuits, faults cause deviations of the electrical potential of the circuit nodes and may manifest as (logic bit) errors captured at a logic circuit storage element e.g. flip-flop or a memory cell. In case the fault does not manifest as error, it is considered to be masked. Depending on the circuit operation, errors can persist in the memory element for long and/or propagate through the whole circuit. They may cause failures at system level. In that case, the system is not able anymore to fulfill its specification.

Some of the prevalent physical mechanisms, which contribute to the manifestation of faults and errors, are briefly discussed in the following:

- (a) Mechanisms that concern devices include:

- (i) Radiation particles [5], [62] e.g. due to ionizing alpha-particles (generated in the package) or due to high-energy cosmic rays may lead to bit-flips. The particles generate (many) electron-hole pairs along their trajectory through the semiconductor material. In the electrical field of the depletion region of a reverse-biased pn-junction, electrons and holes get separated by Coulomb forces leading to charge packets. Depending on the amount of charge and impedance state of the associated electrical circuit nodes, their electric potential is altered significantly.

In case the electric potential at the input of a logic storage element at strobe time, e.g. of a flip-flop, deviates from the expected voltage intervals

- $[V'^{1'}_{max}, V'^{1'}_{min}]$  or  $[V'^{0'}_{max}, V'^{0'}_{min}]$  for the two logic levels, a wrong bit is stored. In addition, these faults can manifest as errors in the memory cells. In the early days, only Dynamic Random Access Memories (DRAMs) were affected, since, in DRAMs, the information is represented by electric charge on a floating (small) capacitance. A particle hit can lead to a significant alteration of the charge packet and, thereby, corrupt the stored bit. Later, due to the decreased feature sizes, Static Random Access Memories (SRAMs) were affected as well. In SRAM cells, the information is stored electronically in a feedback loop. A particle hit can cause the cell to flip from one to the other stable operating point. Today, in nano-scale technologies, as already mentioned, also logic circuit reliability is affected by radiation-induced faults. Often, together with timing violation faults (caused e.g. due to temporarily lower supply voltage), radiation-induced faults are considered as a major source for transient errors and called soft errors.

- (ii) Bias Temperature Instability (BTI) [53], [5], [86], [51] called NBTI for pfet and PBTI for nfet devices, is a time-dependent degradation mechanism, which causes shifts in the device threshold voltage. It is caused by applying a bias voltage at the device at high temperature. The mechanism is based on so-called traps that are present at the oxidesubstrate interface as well as in the gate oxide (e.g. due to impurities). The effect of traps is the creation of hole-electron pairs (capture effect) and their release again (emission effect), which causes temporal variations in the device properties. The variations in the device properties lead in turn to variations in the delay and noise-margin properties of logic circuits and stored electric charges in memory cells. During "no-stress" periods (with gate voltage grounded) devices can recover (at least partially); the time constants for capture and emission have a very wide span, ranging from nanoseconds up to days or longer. In smaller devices, the BTI impact is more significant as the effect of a trap charge is more significant on a tiny device.

- (iii) Hot Carrier Injection (HCI) [53] refers to a degradation effect, according to which, highly ("hot") accelerated (from the electric field of the gate) channel carriers cause impact ionization or can be injected into the oxide. In nfet devices Channel Hot Electron (CHE) and in pfet devices Channel Hot Hole (CHH) effects take place. Again, this effect causes variations of the device properties.

- (iv) **Time-Dependent Dielectric Breakdown** (TDDB) [53], [5], [55] is a degradation effect that occurs due to long lasting tunnel currents through the gate oxide caused by relatively small electric fields and forming filamentary shorts between the gate and substrate. Initially, the mechanism leads to variations of the device threshold voltage. In the end, the gate oxide breaks leading to permanent defects.

- (v) Random Telegraph Noise (RTN) [5] is based on similar mechanisms as BTI but it has much smaller time constants (from subsect down to the subns domain) and causes rapid threshold voltage and thereby current fluctuations. This effect is considered to have more of a statistical nature.

- (b) Mechanisms that concern wires include:

- (i) **Electromigration** (EM) [53], [5] refers to the physical movement of metal atoms in a wire due to high current density, resulting in an increased wire resistance or even in a permanent break. Increased resistances affect interconnect delay or IR drop (see below) in the supply network. The effect can be (partly) reversed by applying current in the opposite direction.

- (ii) Electromagnetic coupling (crosstalk) [5] effects, are due to coupling capacitances between circuit nodes and mutual inductances between circuit loops. In the dominating case of capacitive coupling, a rapid voltage transition on a circuit node (called the aggressor) enforces an alteration of the electric potential of a neighboring node (called the victim). The result is a noise pulse on a quite victim node or, in case that the victim node simultaneously features a transition in opposite direction, an increased delay (the latter being called "noise on delay").

- (c) Mechanisms that are based on intra-die and inter-die correlations include:

- (i) The **IR drop** [5] is the Ohmic voltage drop caused by the interconnect wire resistance. It mainly affects the supply network where it causes dynamic "supply voltage droops" and contributes to the supply voltage noise. Supply voltage droops affect gate delay and supply voltage noise leads to noisy voltage levels at the gate outputs.

- (ii) The **di/dt droop** [5] is the voltage drop over inductance during rapid transitions of the current flowing through it. It also mainly affects the supply network and causes supply voltage droops and contributes to the supply voltage noise as well.

- (iii) **Temperature variation** [10] is caused due to heat flux, created at varying locations on the die depending on the activity (and indirectly the system blocks' functionality). Temperature variations are spatially and temporarily distributed and affect delay and noise margin.

The effects of dynamic IR and di/dt drop on the supply network are similar and designers do take this effect into account and add a margin. Moreover, the supply voltage can be stabilized by applying properly dimensioned buffer capacitances (so-called decoupling capacitances or decaps) across the whole supply network.

(d) Finally, significant enabling components for the aforementioned mechanisms include:

- (i) Process variations [10], [42], which take place at manufacturing time (e.g. Random Dopant Fluctuation (RDF)).

- (ii) Circuit topology and operating parameters (e.g. voltage, frequency).

- (iii) Input workload (e.g. duty cycle, bit pattern etc).

- (iv) Environmental conditions (e.g. heat coming from neighbouring systems).

Having discussed the basic mechanisms, it is important to underline the aspect of different vulnerability for the two logic states, which is relevant for the selection of an error model at the bit level.

Temporal deviations of the electric potential of circuit nodes can be caused due to noise pulses and/or incomplete previous logic level transitions (so-called timing violations). At strobe time, the electric potential at the input of a storage element may either be shifted to a higher (towards plus infinity) or lower (towards minus infinity) value. It can be concluded, that faults, which induce a positive potential shift, can *only* lead to a bit error in storage elements, whose input should be in the low-('0') state. In the same reasoning, faults, which induce a negative potential shift can *only* lead to a bit error on input nodes, which should be in the high-('1') state.

As it is known, chains of CMOS gates feature the capability of level regeneration due to a steep transition in their voltage transfer characteristics. This capability is quantitatively described by the so-called noise margin NM of a gate. Generally, the noise margin is not symmetric concerning the two logic levels, i.e.  $NM_{'1'} \neq NM_{'0'}$ . This can happen due to intentional device dimensioning ("skew"), device parameter variability ("mismatch"), temporal device parameter fluctuation (RTN), temporal or permanent device aging (e.g. due to HCI, BTI, EM) etc. As a consequence, the impact of a circuit node potential shift in general is different for the two logic states or the other way around: the two logic states feature different vulnerability to a potential shift.

Despite the difference in the vulnerability that the two logic states exhibit, the bit-flip error model is widely applied as an error injection model in reliability analysis of digital systems. It describes the probability that a bit is flipped from 1 to 0 or from 0 to 1 at a certain instance of time. This means that the separate probabilities for a flip-to-1- and flip-to-0-error somehow have to be combined (i.e. averaged) to a bit-flip probability. As this is the most well-established error model, we will use the term (functional) bit-flip errors to capture this class of errors, with the worst case manifestation toward the end user being a complete system failure on the expected system service.

The manifested bit-flip errors can be temporary or permanent [9], [10]. Temporary errors include transient and intermittent errors. Transient errors are non-deterministic (concerning time and location), e.g. as a result of a fault due to a particle strike. While the causing faults typically last for one cycle only, the resulting errors may persist longer due to propagation and storing. Transient

errors are considered "external fault"-induced errors and need to be characterized by their average rate of occurrence. Intermittent errors occur repeatedly but non-deterministically in time at the same location and last for one cycle or even for a long (but finite) period of time. Main causes for intermittent errors are design weaknesses, aging and wear-out (e.g. due to BTI, HCI, EM, silicon-wafer direct bonding (SDB) etc.), and parametric faults, not detected as errors during test (as errors due to them are triggered under rare conditions only). They are considered "internal fault"-induced errors and need to be statistically characterized by their (average) rate of occurrence and (average) time of duration. In contrast, permanent errors persist forever after their first occurrence. Causes for permanent errors are fabrication defects not detected during test, accelerated aging and wear-out. Moreover, the bit-flip errors may be spatially or temporarily correlated, forming burst errors [70], [79].

In a similar way that whole systems can be viewed using different abstraction layers with transistors and wires being the building components for gates, storage elements, memory and processing blocks, also reliability effects can manifest and be viewed across the system abstraction layers. Especially, the bit-flip allows the connection of the physical fault mechanisms with the higher system abstractions, where, often, more useful interpretations of the impact of faults on the system can take place. These interpretations can then be provided as input to the designer in order to derive appropriate countermeasures.

### 1.1 Thesis context and contributions

Undeniably, having a more robust system is the ultimate goal of studying the fault mechanisms and their propagation. Having quantitative information on how the faults manifest and propagate through the system allows the researcher and the designer to come up with system-specific, efficient mitigation solutions. So, reliability assessment and resilience and mitigation techniques form two complementary sub-domains within the domain of reliability of digital systems. Reliability assessment [72] includes the derivation of appropriate models for faults and error mechanisms, the various ways to intentionally introduce them in the system, the study of their propagation and impact and the derivation of appropriate metrics that quantify this impact. Resilience and mitigation techniques, as the name implies, include all those approaches that make systems more robust to errors. They cover a broad range of approaches, from static design-time up to demand-driven runtime techniques, that, for example, mask the effect of errors or prevent future occurrences [69].

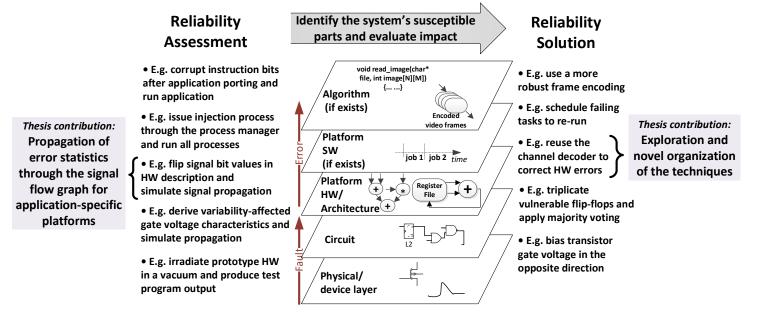

Both reliability assessment and resilience/mitigation techniques can be performed at various abstraction levels of the system leading to different benefits and costs. The left-hand side of Fig. 1.1 shows some examples of how reliability assessment is performed across the abstraction layers. More information can be found in [72]. The right-hand side is complemented with examples of mitigation

actions at the various layers. In practice, the exact mitigation decision should be based on a careful trade-off analysis based on the demands of the system under consideration. In Fig. 1.1, the two contributions of this thesis are sketched.

Figure 1.1: Thesis focus within the reliability assessment and mitigation flow

Reliability assessment sub-domain. Regarding the assessment part, the focus is on deriving efficient ways to propagate bit-flips through the system. Traditionally, at this abstraction layer, such a study has been performed through system simulation and/or emulation. There is a variety of tools with different characteristics that can be used for such a study. Typically, the hardware (HW) is provided in a descriptive form (i.e. using a hardware description language) and ported on the corresponding tool. Then, errors can be injected in different forms: through replacing hardware components (e.g. a NAND with a NOR gate) in the HW description [35], through altering data signals for a specific amount of time by using appropriate commands [35] (instead of altering hardware components), by reusing the scan-chains [23], through introducing extra components (e.g. multiplexers) that allow the injected signal to be introduced instead of the correct one [50] to name some examples. Sometimes, FPGAs [50] or HW emulator environments [16] are used to speed-up such a process. Despite the good accuracy provided by such tools, the execution time to perform repetitive experiments as well as the migration and general engineering effort to set-up the injection frameworks are issues to be avoided (whenever possible) for the designers. Therefore, there is an ongoing demand for improving such frameworks or finding alternatives. Exploiting the characteristics of one's specific context is a starting point for finding attractive alternatives.

The context of this work, in terms of target applications and platforms, is defined by the focus on communication systems. There are some common characteristics of such systems. The hardware is composed to a significant extent of non-flexible parts (ASIC-style). This is the case for example, for Personal Area Network (PAN) and Body Area Network (BAN) systems. Quite often, in communication systems, the application input signal is viewed as a stochastic signal with certain statistical characteristics. This gives the flexibility to make use of the signal statistics in order to find efficient ways to propagate the error signal. For this, the system signal flow is a sufficient system model and a detailed hardware description of the system is not required as the main objective is that the signal statistics at the output are accurate.

Having as starting point the bit-flip model, efficient ways are explored in this thesis to study the propagation of bit-flips through communication systems. Analytical and statistical approaches are employed to avoid the time-consuming system simulation. This is enabled by choosing appropriate models to represent errors as they propagate through the system, decomposing the system into blocks and exploiting linearity in a stochastic framework. On top, contrary to earlier works, the effect of non-linearities on the error propagation (due to operations like saturation and quantization in the block internals) are considered. More specifically, the core elements of this contribution are:

- (i) We discuss possibilities and limitations in employing analytical methods, like using statistical moments, to derive signal statistics in the context of hardware-induced bit-flips. The focus is on the so-called Linear-Time-Invariant (LTI) blocks. We show that purely analytical approaches can have limited use in the context of estimating the impact of hardware-induced bit errors, due to the correlation that exists between the errors and the signal.

- (ii) We discuss possibilities and limitations in using a mathematical transform, the Principal Component Analysis (PCA), to speed-up error injection experiments.

- (iii) We propose a framework that exploits the repetitive nature of fault injection experiments to speed-up experiments for LTI blocks. We distinguish between the cases that all the operators from the input to the output of the LTI block act in a linear time-invariant way and the case that non-linear operations due to finite wordlengths take place.

Reliability solution sub-domain. Once the error propagation has been studied and the impact is evaluated, an appropriate mitigation scheme has to be selected. The second contribution in this thesis regards mitigation. Given the larger overhead required to mitigate faults at the circuit level, it may be preferable to seek higher level solutions. Here, we provide an exploration and novel classification of hardware-based schemes at the higher system abstraction in the mitigation domain. More specifically, the core elements of this contribution are:

- (i) An comprehensive overview of the domain of functional reliability techniques at the (micro-)architectural level is presented, using a systematic, hierarchical top-down splitting into sub-classes. Pros and cons of each sub-class are identified.

- (ii) Multiple representative prior and state-of-the-art publications are mapped to these categories to illustrate the concepts involved.

### 1.2 Thesis outline

Chapters 2, 3, 4, 5 contain the first part of our contribution in the reliability assessment sub-domain. Chapter 2 gives the context of the error statistics propagation study including relevant definitions. Chapter 3 discusses our findings while considering the propagation of statistical moments of corrupted, uncorrelated signals through LTI blocks. Chapter 4 explores the possibilities in using the Principal Component Analysis to speed-up the error injection experiments. Chapter 5, illustrates the generic framework for propagating a corrupted signal through LTI blocks that include internally non-linear operations due to finite wordlengths. Chapter 6 is the contribution in the mitigation sub-domain and, more specifically, it presents a novel, systematic classification of hardware-based mitigation techniques along with discussing multiple examples per class. Chapter 7 summarizes and concludes the work.

# Chapter 2

# Background and Context

### 2.1 Outline

Chap. 2 provides the context of the current work, including the motivation to handle the system complexity for injection experiments and relevant definitions. Sec. 2.2 describes the target systems and characteristics of signals in such systems. Sec. 2.3 provides background information on the characteristics of error injection and propagation studies. In addition, the error model is introduced. Sec. 2.4 gives an overview of the stochastic framework being used, under which, the proposed approaches (presented in the following chapters) fall under. Sec. 2.5 illustrates the characteristics of the bit error model as compared to two other noise sources: quantization noise and channel noise. Sec. 2.6 summarizes the main elements that constitute the general framework.

# 2.2 Target systems and random processes

# 2.2.1 Target systems characteristics

Digital communication systems. In communication systems information is transmitted from a sender to a receiver over a channel. Namely, the information signal is not known beforehand to the receiver. The channel is exposed to noise and distortions. Both the information and noise signals can be represented using random processes. Especially digital communication has now become a standard due to its various advantages, among which, the fact that digital hardware is cheap, area-efficient and "reliable". Digital communication systems operate on signals that are specified at discrete time points (achieved through sampling) and discrete amplitude levels (achieved through quantization).

Signal processing and representation. The system transforms the input information signal in such a way so that the probability is in the best way

increased that the signal will be distinguished at the channel output. Among the issues that have to be handled during this transformation are the channel noise, symbol interference, synchronization between the transmitter and the receiver. One prominent transformation example is the processing of the signal by the scrambler before it gets transmitted. Through the scrambler, the data gets randomized so that long sequences of zeros and ones are avoided; this makes the received data pseudorandom, i.e. close to ideal binary random sequence with each signal taking the value 0 and 1 with a 0.5 probability [88]. This makes the signal representation by a random process very fitting. Interleaving and modulation are other processing steps in communication systems. Channel noise is an additive noise (does not depend on the transmitted signal). For wireline communication systems, this noise is characterized by a Gaussian process. For other systems, typically multiple paths exist and more complicated models are required [24].

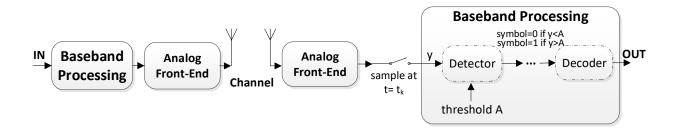

**Performance evaluation.** As the signal communication cannot be error-free, the effort of designers is focused on reducing the error probability so that the accuracy of the received digital signal improves. To derive this probability, either the process is analytically characterized or statistics are gathered by repeating the experiment a sufficient amount of times. To illustrate this, the simple example of threshold detection in a binary channel is used, as shown in Figure 2.1. Symbols 0 and 1

Figure 2.1: Detection operation in binary baseband communication system

are transmitted with equal probability over the channel using a negative and a positive pulse respectively. Each pulse is sampled at peak amplitude y (at time instance  $t = t_k$ , with k indicating the time index). If the sampled value y is bigger than the threshold A (= 0 here), the detector reads a 1; in the opposite case, it reads a 0. However, y contains the original pulse peak amplitude plus a noise amplitude, which ranges from  $-\infty$  to  $+\infty$ . Therefore, a received 0 can be read as 1 and vice versa. To find this error probability, the experiments are repeated N times  $(N \to \infty)$  [44], so that the process can be characterized (unless the error probability can already be derived analytically). Often, and depending on the objectives, the baseband system model (i.e. the system without modulation) is only analyzed in such an error probability study. The results can be extended to the passband

(or bandpass) model.<sup>1</sup> To evaluate the performance of the communication system, typically metrics, such as the Bit Error Rate (BER), are used. BER indicates the number of erroneous bits out of the total number of received bits. The erroneous bits are found by comparing the error-free implementation—that is, in the absence of channel noise—with the implementation in the presence of noise. Sometimes, variations of this metric are used, like the Packet Error Rate (PER).

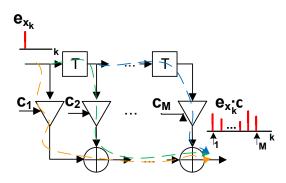

LTI blocks. A significant part of the system blocks are linear time-invariant (LTI) blocks. As the name implies, the characteristic properties of LTI blocks are homogeneity, additivity (necessary and sufficient properties for linearity) and shift-invariance. LTI blocks may have memory or be memoryless. They include arithmetic (rather than decision making) operators and more specifically, they are composed of linear operators such as adders, constant multipliers, constant shifters. Examples of LTI blocks include: memory blocks, interleavers, some types of multiplexers, Finite Impulse Response (FIR) filters, Discrete Fourier Transform (DFT) blocks.

A LTI block is fully characterized by its impulse response [57]. Here, the focus is on non-recursive, discrete-time and discrete-value (digital) LTI blocks that are causal. Assuming input samples  $x_k$ , output samples  $y_k$  and an impulse response  $c_n$ , the block output can be calculated by the superposition of the impulse response weighted and shifted according to the corresponding input samples. An alternative way to represent LTI blocks is by using their difference equation (here for non-recursive LTI blocks):

$$y_k = \sum_{n=1}^{M} c_n \cdot x_{k-(n-1)}. \tag{2.1}$$

By appropriately describing the values of  $x, y, c_n, M$  (real- or complex-valued, vectors or matrices) in Eq. 2.1 all possible digital LTI blocks can be represented. For example, in a Discrete Fourier Transform (DFT) block, the x, y are vectors, M = 1 and  $c_1$  is a matrix. In case of a direct-form FIR filter,  $c_n$ , with  $1 \le n \le M$ , are the filter coefficients and x, y are scalars.

Often, the random process at the output of LTI blocks can be derived analytically or at reduced cost using other mathematical methods for a given random process at the input of the system. LTI blocks are the focus of this study.

$<sup>^1</sup>$ In radio-based communication systems before transmission, typically the signal has to be upconverted to a higher frequency band, the so-called *passband*. Consequently, at receive-side the received signal has to be down-converted. For the sake of simplicity and efficiency, in system simulation often the whole chain of up-converter, radio channel (i.e., the *passband-channel model* including amplifiers as well as filters etc. on transmit- and receive-side), and down-converter (including carrier recovery) is replaced by a typically complex-valued equivalent *baseband-channel model*. Moreover, in today's digital communication-system simulation frequently also the Digital-to-Analog (D/A) and Analog-to-Digital (A/D) converters (including clock recovery) are hidden in the equivalent *discrete baseband-channel model* [8, 15].

### 2.2.2 Relevant terms from statistics and probability theory

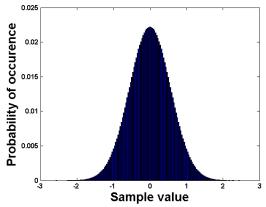

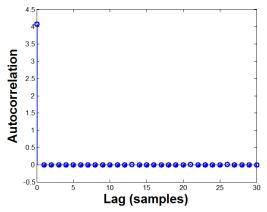

Signal statistical characteristics. As often done in digital signal processing, the digital signal x is modeled as a realization of a random process, with the signal samples  $x_k$  being discrete-state Random Variables (RVs) at discrete time instances k. The random process has certain statistical characteristics, like the statistical moments mean  $\mu_X$ , variance  $\sigma_X^2$  etc. and/or a Probability Mass Function (PMF). PMFs provide information on the probability distribution of the amplitudes of the discrete signal, like Probability Density Functions (PDFs) do for continuous variables. Fig. 2.2a shows a PMF example for normally-distributed discrete signals. In order to have a complete characterization of the random signal, information on how these amplitudes are interrelated over time is needed on top. For many applications, certain averages are used, like the autocorrelation [60]. For a timediscrete signal x the Autocorrelation Function (ACF) of lag l is defined as  $r_{xx,l}$  $E[x_{k+l} \cdot x_k^*]$  with E[.] being the expected value and (.)\* being the complex conjugate of a complex-valued sample value. It is often visualized by plotting the sample autocorrelation values versus the time lags (or sample lags), as shown in Fig. 2.2b. In case of a so-called wide-sense stationary process,  $r_{xx,l}$  does not depend on time index k. For a white random process the autocorrelation is zero (except at lag 0). In this case (see Fig. 2.2b), no identifiable relationship among the samples can be observed. In general, both types of information, probability mass functions (PMFs) and autocorrelation are required in order to fully characterize a stationary The relations among random variables can be described using functions other than the PMF and autocorrelation, like the characteristic function, the moment-generating function and others [60]. Covering an in-depth analysis of all the alternative ways is out of the thesis scope. A random signal after hardwareinduced bit flips have been injected will be called *corrupted signal*. The error of a corrupted signal sample  $\tilde{x}_k$  is denoted by  $e_k = \tilde{x}_k - x_k$  and will be called **error** signal sample.

(a) Probability Mass Function plot of normally distributed discrete signals

(b) Autocorrelation plot of a white process

Accuracy Evaluation. The accuracy between a precise model and an approximated one can be measured in different ways, depending on the objectives. Here, we present one well-established means, used for comparing probability distributions.

The Kullback Leibler divergence or KL divergence [48] is a measure of the difference between two probability distributions P and Q, when Q is used to approximate P. It represents the amount of information lost with this approximation; therefore, the smaller the KL value, the closer the distributions are. For discrete probability distributions P and Q, the Kullback Leibler divergence from Q to P is defined to be

$$D_{KL}(P \parallel Q) = \sum_{i} P(i) \cdot \log \frac{P(i)}{Q(i)}.$$

(2.2)

Namely, it is the expectation of the logarithmic difference between the probabilities P and Q, where the expectation is taken using the probabilities P. The quantity  $\log \frac{1}{p}$  is a measure of the surprise when an event, which has probability p, actually occurs (e.g. a highly improbable outcome is very surprising). To acquire an estimate of the average value of the surprise involved with a whole set of events, that follow a probability distribution P, the previous is extended. For every possible outcome i associated with a probability P(i), the  $\log \frac{1}{P(i)}$  is weighted by P(i) and all products are summed. This gives the entropy of the probability distribution P, which is defined as

$$H(P) = \sum_{i} P(i) \cdot \log \frac{1}{P(i)}.$$

(2.3)

Cross-entropy can be interpreted as a measure of the surprise when a wrong distribution Q is assumed while the data actually follows a distribution P. It is defined as

$$H(P,Q) = \sum_{i} P(i) \cdot \log \frac{1}{Q(i)}.$$

(2.4)

The KL divergence is then the difference of the cross-entropy H(P,Q) and the entropy of P, H(P). Namely, it gives a measure of the "additional" surprise when Q is wrongly assumed (rather than the actual P) compared to when P (the correct one) is assumed.

# 2.3 Error injection and propagation studies

Error injection campaigns (sometimes in literature called fault injection campaigns independent of the system abstraction) consist of repetitive simulation experiments (or executions on a prototype system), during which, values at selected points are modified to mimic a fault effect. An elementary error injection experiment corresponds to one simulation run of the target system [97], with one or more bits being corrupted. In general, a huge amount of elementary error injection

experiments are required in order to include all nodes of interest, all bit positions within a node and all system states. A node in this context designates a location in the system control- or data-path, at the input or output of its basic components, such arithmetic units, memories, registers. In such campaigns, the goal is to perform the following two actions efficiently: (1) error injection-selection of nodes, bits, system states to be corrupted and mimicking of the fault effect in a manner so that useful information regarding the vulnerability of the system is derived, and (2) error propagation-selection of the system representation and propagation of the corrupted signal to the system output (or to another point of interest, from which the impact on the system can be extrapolated). Efficiency, in this context, refers to minimizing the required time and/or the computational complexity to perform such an analysis.

### 2.3.1 Error injection

**Injection points.** Ideally, information on the impact of every bit in every node for every system state would be desired; this would lead to an *exhaustive* error injection campaign. In a system with n flip-flops, and without pruning any of the system states (i.e. without pruning non-reachable during normal execution system states), the state-space cardinality is  $2^n$ . This makes an exhaustive campaign impossible and has made it imperative to look for alternatives.

A selective error injection campaign examines the impact of only a subset of the flip-flops. The selection of this subset is performed on several possible criteria, depending on the system and the designer's objective. One direction is that the selected bit positions to be explored are deterministically chosen using some direct or indirect knowledge regarding their importance. This knowledge may concern their vulnerability to certain fault effects (for example flip-flops closer to nodes with specific interconnect distance, signal directions, switching times and driver strength can be more vulnerable to crosstalk effects) and is derived by lower-level fault models (such as transistor-level models) [66, 76]. Their importance may also be provided by the role they play in the system functionality (e.g. control bits) or that they are representative for a group of bit positions [52]. In the latter case, the designer's deep understanding of the system functionality may be a decisive factor for the selection. A second direction is that the subset to be explored is randomly chosen, so that a desired confidence is achieved [16, 22]. The points in the sampling space (which consists of the total amount of flops and system states) may be equally probable or may be assigned a weight according to their relative probability of occurrence. Sometimes combinations of the injection approaches are implemented.

In this work it is assumed that all bits of a word can be potentially corrupted with equal probability, similar to [39]. The focus is on propagating efficiently the errors through system blocks (see below). So, the assumption is that the errors have occurred earlier at the internals of a block (within a system) and manifest at the input of the block of interest. For example, the errors occur in the memory buffer just before the filter block in the baseband model of a BPSK

communication line, as depicted in Fig. 2.2. We focus on propagating the errors through the filter block in this case.

Figure 2.2: Example of BPSK-based communication line

Bit error model assumption. To simplify this discussion and without loss of generality, we assume integer signal samples represented by a non-redundant two's complement notation composed of n bits. We use  $\nu$  to denote the bit position as used in the two's complement notation, i.e. the sample of the time discrete signal x at time instance k (subscript) is:

$$x_k = -x_k^{n-1} \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} x_k^{\nu} \cdot 2^{\nu}, \tag{2.5}$$

where  $x_k^{\nu}$  is the bit in position  $\nu$ , with weight  $2^{\nu}$ , and  $x_k^{n-1}$  is the Most Significant Bit (MSB) sign bit <sup>2</sup>.

An erroneous bit-flip at time instance k in bit position  $\nu$  is denoted by the flip-error bit  $\epsilon_k^{\nu}$ . The **bit-flip sample**  $[\epsilon_k^{n-1},...,\epsilon_k^1,\epsilon_k^0]$  can be described like a signal sample

$$\epsilon_k = -\epsilon_k^{n-1} \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} \epsilon_k^{\nu} \cdot 2^{\nu}. \tag{2.7}$$

Clearly, after some bit-flips the erroneous signal sample  $\tilde{x}_k$  becomes

$$\widetilde{x}_{k} = -\widetilde{x}_{k}^{n-1} \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} \widetilde{x}_{k}^{\nu} \cdot 2^{\nu}

= -(x_{k}^{n-1} \oplus \epsilon_{k}^{n-1}) \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} (x_{k}^{\nu} \oplus \epsilon_{k}^{\nu}) \cdot 2^{\nu}$$

(2.8)

with  $\widetilde{x}_k^{\nu} = x_k^{\nu} \oplus \epsilon_k^{\nu}$  being the erroneous sample bit in bit position  $\nu$ . The effect of the bit-flipping(s) can also be described by adding an error sample  $e_k = -e_k^{n-1} \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} e_k^{\nu} \cdot 2^{\nu}$  to the error-free signal sample in every bit position:

$$\widetilde{x}_k = x_k + e_k = -(x_k^{n-1} + e_k^{n-1}) \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} (x_k^{\nu} + e_k^{\nu}) \cdot 2^{\nu}.$$

(2.9)

From Eq. 2.9, 2.8, 2.5, it follows that:

$$e_{k} = \widetilde{x}_{k} - x_{k} = -(x_{k}^{n-1} \oplus \epsilon_{k}^{n-1}) \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} (x_{k}^{\nu} \oplus \epsilon_{k}^{\nu}) \cdot 2^{\nu} + x_{k}^{n-1} \cdot 2^{n-1} - \sum_{\nu=0}^{n-2} x_{k}^{\nu} \cdot 2^{\nu}$$

$$= -(x_{k}^{n-1} \oplus \epsilon_{k}^{n-1} - x_{k}^{n-1}) \cdot 2^{n-1} + \sum_{\nu=0}^{n-2} (x_{k}^{\nu} \oplus \epsilon_{k}^{\nu} - x_{k}^{\nu}) \cdot 2^{\nu}$$

(2.10)

$$x_k = -x_k^{n-1} \cdot 2^{n-1} + \sum_{\nu=-m}^{n-2} x^{\nu} \cdot 2^{\nu}.$$

(2.6)

Accordingly, the notation for a whole word is given by n.m, with the "." denoting the radix point.

$<sup>^{2}</sup>$ In the more general case of a signal with n integer bits (including the sign bit), and m fractional bits, the equation is equal to

with the error sample digit  $e_k^{\nu}$ :

$$e_k^{\nu} = x_k^{\nu} \oplus \epsilon_k^{\nu} - x_k^{\nu} = (-1)^{x_k^{\nu}} \cdot \epsilon_k^{\nu} = (1 - 2 \cdot x_k^{\nu}) \cdot \epsilon_k^{\nu} \in \{-1, 0, 1\}.$$

(2.11)

It is worth noticing that due to the addition  $mod_2(\oplus)$  (bit-wise exclusive OR) in Eq. 2.8 a bit-flip results in an error contribution being dependent on the signal sample value.

When the error-free signal sample gets corrupted by the bit-flip sample, the amplitude of the signal will be modified by a quantity as big as the error magnitude<sup>3</sup>. Fig. 2.3 depicts this effect for two different two's complement 8-bit samples. In both cases the bit-flip sample has the magnitude 16 (2<sup>4</sup>). Corrupting the two samples with this bit-flip sample will change their amplitude by the quantity 16. In the first case, the value 16 will be subtracted. In the second case, the value 16 will be added.

Figure 2.3: Both signal values change by the same magnitude but in different directions leading to different amplitudes.

### 2.3.2 Error propagation

**System defined scope.** Fig. 2.4 shows three views of the same system. First, in Fig. 2.4a the system is viewed as a black box with only inputs and outputs. Then, in Fig. 2.4b, the system is split into a number of subsystems, with each one having its own inputs and outputs. Fig. 2.4c shows a more fine-grained decomposition of the same system. Each of these views can be useful according to the context.

Fig. 2.5 shows the same system abstractions after an error has been injected. Several elements can help to identify a suitable scope for error injection and propagation experiments: There are two subsystems (or blocks) that are not affected by the injected error, i.e. the blocks  $S_{2,1}$ ,  $S_{2,4}$ . Namely, in case the system is considered as in Fig. 2.5a or even Fig. 2.5b, these two subsystems will execute (and thus cost execution time) without contributing any new information compared

<sup>&</sup>lt;sup>3</sup>magnitude of a variable is the measure of how far, regardless of direction, its quantity differs from zero while amplitude is the measure of how far, and in what direction, that variable differs from zero

Figure 2.4: Views of the same system at different abstractions

to the information acquired by the error-free execution of these two blocks. In Fig. 2.5a (and potentially also Fig. 2.5b), a masked error cannot be identified until it reaches the system output. Having the information sooner allows the researcher to halt system execution and save computation time. In Fig. 2.5a, it does not become visible whether a specific block contributes significantly (asymmetrically) to the error propagation (for example, by forwarding it in multiple paths), and, thus, insight is missed. It becomes clear, that in the given context, there are several disadvantages in considering the system as a whole compared to examining the subsystems separately.

(a) Error(s) at system-level (b) Error(s) at subsystem level 1 (c) Error(s) at subsystem level 2

Figure 2.5: Views of the error injection and propagation in a system at different abstractions

To efficiently handle complexity, instead of considering the complete chain of subsystems during error propagation, each subsystem can be studied separately. In the general case, this requires that no feedback loops are present among the subsystems under study. Then, by applying appropriate inputs, namely inputs with the same characteristics as in the case that the whole chain of system blocks would execute together, correct output results can be derived at a lower complexity cost. In cases that the information and/or error signal can be statistically characterized (and potentially represented by a random process) at the input of the block, new ways of efficiently handling the complexity of propagation become available. Fig. 2.6 shows a projection of the system decomposition concept onto communication systems, which constitute the focus application domain for this work.

When decomposing the system into subsystems, a trade-off is present between reducing complexity by considering stand-alone blocks and increasing

complexity by handling information in a very fine-grain manner and having to reintegrate fine-grain information in the system context [61]. Therefore, a compromise is required. In our context, working at the level of groups of primitive operators—operators like multiplications and additions—achieves a good compromise and is compatible with using as error model the bit-flip. An additional criterion for deciding on the level of the decomposition is that the function of the blocks can be potentially analytically or otherwise mathematically modeled; such is the case, for example, with LTI blocks.

Figure 2.6: Example of splitting a communication system into subsystems

System functional model. Simulation-based techniques use a system model to propagate the errors. The model description can be closer to the hardware implementation (bit- and cycle-accurate e.g. using hardware description language models) or more abstract, depending on the type of information and accuracy required. The trade-offs involved among system models of different abstraction typically involve accuracy versus simulation time. As, in our case, the signal statistics are of interest, a bit-true functional system model is sufficient. A bit-true model uses the same number system and precision (like rounding or truncation) as the prototype hardware would. Simulations are a safe way to derive the necessary reliability data, as they can be applied to any type of system, but typically quite time-consuming; especially, due to the repetitive nature of error injection campaigns. In this work, simulation implementations constitute the reference implementations (as the most established means for such an analysis) and are performed in Matlab.

Analytical and other mathematical techniques are alternative-to-simulation approaches to calculate the signal statistics in a manner that the result is equivalent with the statistics that would be derived by performing system simulation(s); i.e. so that the signal statistical parameters are equal between the two approaches. For example, through analytical approaches, closed-form expressions can be used to derive certain statistical parameters when linear transformations take place. Using such an approach is typically much more time-efficient compared to performing system simulation, but can be only applied to systems with specific characteristics (i.e. in the aforementioned example, systems with linear operators); therefore, sometimes a combination between simulation-based and mathematical-transform-based methods can be the optimal solution. In this work we employ

analytical and other mathematical methods to speed-up the computations required in fault injection campaigns. Some of these techniques have been used since a long time in the domain of analyzing the effect of quantization noise [94, 54] but cannot be reused in a similar way due to the inherently different nature of hardware-induced errors (see Sec. 2.5 for more details).

### 2.4 Framework overview

To handle the simulation complexity in communication systems, stochastic analysis is a promising direction. According to the stochastic approach, the system's response is modeled in a statistical way. This can be achieved in any system by gathering sufficient data from the results of simulations based on random system states and input sequences. However, when, on top, the signal is considered as a stochastic process (i.e. a non-countable infinity of random variables), a number of tools become available which allow the representation and propagation of such data through system models. The signal then can be completely characterized by the PMF and ACF. Therefore, having these two functions available inbetween system blocks provides us with all the necessary information to derive the final system output metrics. If needed, random data can be generated according to the given PMF and ACF, using techniques, like the copulas [21].

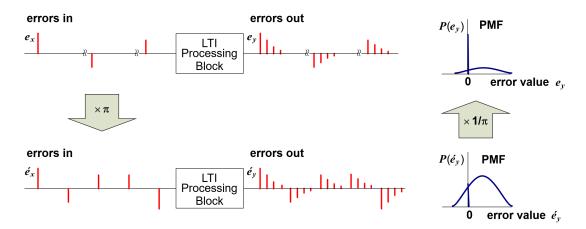

Fig. 2.7 shows a conceptual illustration of the framework, within which, the proposed approaches, presented in the following chapters, operate. An example system with two inputs In1, In2 and one output Out is composed by a mixture of LTI and non-LTI blocks. The error signal is generated and propagated through the various blocks until it reaches the system output. The error signal, characterized by the PMF and ACF, can be propagated through the non-LTI blocks by performing simulation (random data can be generated by using techniques like copulas) and through the LTI blocks using analytical and other mathematical methods. The latter is the focus of this study. When the error signal reaches the output, appropriate error metrics can be derived exploiting the PMF or the ACF. In summary, the components that synthesize the proposed error propagation framework are the following:

- The system is de-composed into subsystems and blocks. Each of these can then be examined as a stand-alone subsystem/block, assuming no closed loops. The propagation of the information can occur through a combination of simulation for non-LTI blocks and analytical and other mathematical techniques for LTI blocks (as a way to achieve computational speed-up).

- Statistics is an effective way to represent the information at the input and output of the block under investigation for communication systems as statistical metrics are of interest anyhow. On top, if the signal is represented as a stochastic process, analytical and other methods become available for the propagation through the LTI blocks. The error signal can be represented by

# OVERVIEW OF THE ERROR PROPAGATION FRAMEWORK

Figure 2.7: Error signal generation and propagation through the system blocks using a mixture of techniques

both the PMF and the ACF as these characterize fully a stochastic process.

- The error metrics of interest at the system output are application-specific, and typically include first-order statistical metrics, like the BER, and/or second-order statistical metrics, like a sequence of missed packets of a specific length. PMF and ACF are required to cover both types of metrics.

- To construct an error model at the input of a block, an increased error injection percentage may be assumed in order to accelerate the procedure of gathering sufficient statistics.

# 2.5 Correlation between the error and error-free signal and comparison with noise sources

As mostly done in literature, a bit-flip error model is assumed here. These models describe the probability of a bit-flip from 0 to 1 or 1 to 0 at a specific bit position in the digital signal samples. The bit-flip probability for bit position  $\nu$  with weight  $\pm 2^{\nu}$  is denoted by  $\pi^{\nu}$ . In case of a 0-to-1 flip in bit position  $0 \le \nu < n-2$  the sample value is corrupted by an error of  $+2^{\nu}$  and a 1-to-0 flip yields an error of  $-2^{\nu}$ . For bit position  $\nu = n-1$  (i.e. the sign bit in two's complement representation) the opposite signs have to be applied. The physically underlying mechanism leading to the bit-flips is also modeled as a random process, called bit-flip mechanism in this work.

Other sources of errors typically studied in signal processing and, more specifically, communication systems include the quantization noise (which manifests itself when the floating-point implementation of the system is turned into a fixed-point) and the noise that is introduced from the channel of the communication system. Both of these noise sources have been studied for a long time in the literature. All three sources of errors are additive and can be modeled as random processes; however, they have different characteristics. At this point the goal is especially to illustrate the differences of bit errors and the other two noise sources regarding their correlation with the information signal. For the illustration, a 20 kHz sinusoidal signal of amplitude 1 is used as reference; it represents the information signal before any errors are added.

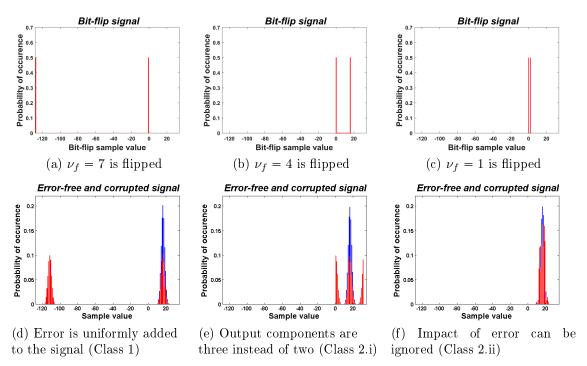

Channel noise. Channel noise is the noise that is introduced on the information signal through the channel. In case the sources of noise are the electronic components and amplifiers at the receiver, the channel noise can be characterized statistically as a Gaussian process [93]. Actually, this model is the predominant one in communication system analysis and design. Information signal and channel noise are typically additive. Fig. 2.8 shows two periods of the reference error-free sinusoidal signal and the same signal after it has been corrupted by Gaussian channel noise with  $\mu = 0$  and  $\sigma^2 = 0.2509$ . To improve the visibility, three red, vertical, dotted lines

split the graphs into four half-periods. The same splitting is performed in all figures of this section. Fig. 2.9 shows the channel noise for the corresponding two periods of

Figure 2.8: Two periods of the error-free (a) and the corrupted-by-channel-noise (b) sinusoidal signal

the sinusoidal signal, before and after the interaction with the sinusoidal signal. It is obvious that there is no difference between the two noise signals, i.e. the channel noise is independent of the information signal.

Figure 2.9: Channel-induced error signal (a) modeled and (b) resulting after the interaction with the error-free sinusoidal signal

Quantization noise. Quantization is the process of mapping values from a bigger (and possibly continuous) set of values to a smaller (discrete) set. In practice, for digital systems, this means either the mapping of analog values onto discrete