# Performance Modeling and Prediction for Dense Linear Algebra

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

# Elmar Peise, Master of Science

aus Aachen, Deutschland.

Berichter: Universitätsprofessor Paolo Bientinesi, Ph.D.

Universitätsprofessor Dr. rer. nat. Matthias Müller

John Gunnels, Ph.D.

Tag der mündlichen Prüfung: 30. November 2017

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

# Abstract

This dissertation introduces measurement-based performance modeling and prediction techniques for dense linear algebra algorithms. As a core principle, these techniques avoid executions of such algorithms entirely, and instead predict their performance through runtime estimates for the underlying compute kernels. For a variety of operations, these predictions allow to quickly select the fastest algorithm configurations from available alternatives. We consider two scenarios that cover a wide range of computations:

To predict the performance of blocked algorithms, we design algorithm-independent performance models for kernel operations that are generated automatically once per platform. For various matrix operations, instantaneous predictions based on such models both accurately identify the fastest algorithm, and select a near-optimal block size.

For performance predictions of BLAS-based tensor contractions, we propose cache-aware micro-benchmarks that take advantage of the highly regular structure inherent to contraction algorithms. At merely a fraction of a contraction's runtime, predictions based on such micro-benchmarks identify the fastest combination of tensor traversal and compute kernel.

# Acknowledgments

First and foremost, I would like to express my sincere gratitude to my advisor Paolo Bientinesi. While guiding me through my studies, he always embraced my own ideas and helped me shape and develop them in countless discussions. While he granted me freedom in many aspects of my work, he always had time for anything between a quick exchange of thoughts and extensive brainstorming sessions. Beyond our professional relationship, we enjoyed twisty puzzles and board games in breaks from work, long game nights, and annual trips to SPIEL. I consider my self lucky to have spend my time as a doctoral student with him and his research group.

The HPAC group proved to be much more than a collection of researchers working on remotely associated projects; my colleagues were not only a source of incredibly valuable discussions and feedback regarding my work, we also indulged in various unrelated arguments and exchanges over lunch and at many other occasions. My thanks go to Edoardo Di Napoli, Diego Fabregat-Traver, Paul Springer, Jan Winkelmann, Henrik Barthels, Markus Höhnerbach, Sebastian Achilles, William McDoniel, and Caterina Fenu, as well as our former group members Matthias Petschow, Roman Iakymchuk, Daniel Tameling, and Lucas Beyer.

I am grateful for financial support from the Deutsche Forschungs-Gemeinschaft (DFG) through grant GSC 111 (the graduate school AICES) and the Deutsche Telekomstiftung. Their programs not only funded my work, but opened further opportunities in the form of seminars and workshops, and connected me with like-minded students from various disciplines.

The RWTH IT CENTER provided and maintained an extremely reliable infrastructure central to my work: the RWTH COMPUTE CLUSTER. I thank its

staff not only for ensuring smooth operations but also for their competent and detailed responses to my many inquiries and requests regarding our institute's cluster partition.

The AICES service team did their best to shield me from the bureaucracy of contracts, stipends, and reimbursements. I am grateful they allowed me to focus solely on my research.

Even more important than a gratifying work environment is forgetting about it every once in a while. My friends played a bigger role in this effort than probably most of them know, whether we were simply spending time hanging out or playing games, went swimming, climbing or playing badminton, or taught swimming and worked as lifeguards. You are too many to enumerate, but you know who you are.

Finally, but most importantly, none of this would have been possible without the endless and uncompromising support of may parents. You are the reason I grew into the person I am today. Danke!

| 1 | Intr | oduct  | ion                                             | 1  |

|---|------|--------|-------------------------------------------------|----|

|   | 1.1  | Perfor | mance Modeling for Blocked Algorithms           | 3  |

|   |      | 1.1.1  | Motivation: Blocked Algorithms                  | 4  |

|   |      | 1.1.2  | Prediction through Performance Models           | 9  |

|   | 1.2  | Micro  | -Benchmarks for Tensor Contractions             | 10 |

|   |      | 1.2.1  | Motivation: Tensor Contraction Algorithms       | 10 |

|   |      | 1.2.2  | Prediction through Micro-Benchmarks             | 13 |

|   | 1.3  | Relate | ed Work                                         | 14 |

|   |      | 1.3.1  | Dense Linear Algebra Libraries and Algorithms   | 15 |

|   |      |        | 1.3.1.1 BLAS and LAPACK                         | 15 |

|   |      |        | 1.3.1.2 Blocked Algorithms                      | 16 |

|   |      |        | 1.3.1.3 Alternatives to Blocked Algorithms      | 17 |

|   |      |        | 1.3.1.4 Distributed-Memory and Accelerators     | 18 |

|   |      | 1.3.2  | Performance Measurements and Profiling          | 19 |

|   |      | 1.3.3  | Performance Modeling and Predictions            | 19 |

|   |      | 1.3.4  | Tensor Contractions                             | 21 |

| 2 | Per  | formaı | nce Effects and Measurements                    | 23 |

|   | 2.1  | Perfor | emance Effects for Dense Linear Algebra Kernels | 24 |

|   |      | 2.1.1  | Library Initialization Overhead                 | 24 |

|   |      | 2.1.2  | Fluctuations                                    | 25 |

|   |      |        | 2.1.2.1 Background and System Noise             | 25 |

|   |      |        | 2.1.2.2 Intel Turbo Boost                       | 27 |

|   |      |        | 2.1.2.3 Distinct Long-Term Performance Levels   | 29 |

|   |      | 2.1.3  | Thread Pinning                                  | 30 |

|   |     | 2.1.4  | NUMA Effects                                 | 31 |

|---|-----|--------|----------------------------------------------|----|

|   |     | 2.1.5  | Caching                                      | 33 |

|   |     | 2.1.6  | Summary                                      | 34 |

|   | 2.2 | Measu  | rements and Experiments: ELAPS               | 34 |

|   |     | 2.2.1  | The Sampler                                  | 35 |

|   |     | 2.2.2  | The ELAPS PYTHON Framework                   | 38 |

|   | 2.3 | Summ   | nary                                         | 41 |

| 3 | Per | formar | nce Modeling                                 | 43 |

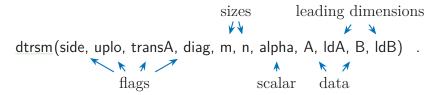

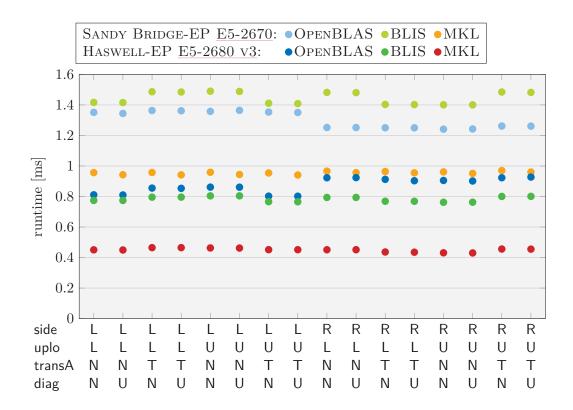

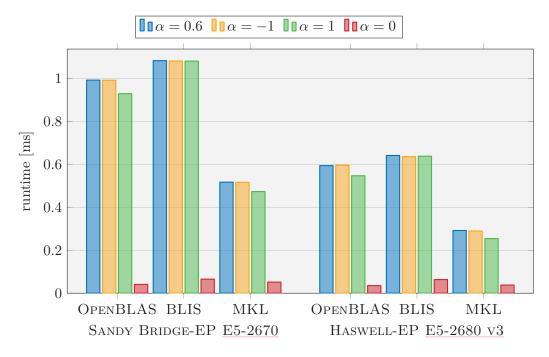

|   | 3.1 | Kerne  | d Argument Analysis                          | 44 |

|   |     | 3.1.1  | Flag Arguments                               | 47 |

|   |     | 3.1.2  | Scalar Arguments                             | 49 |

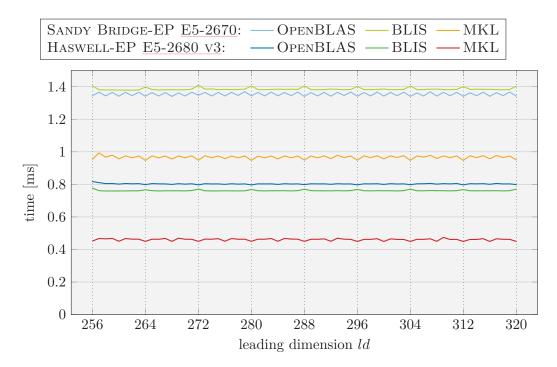

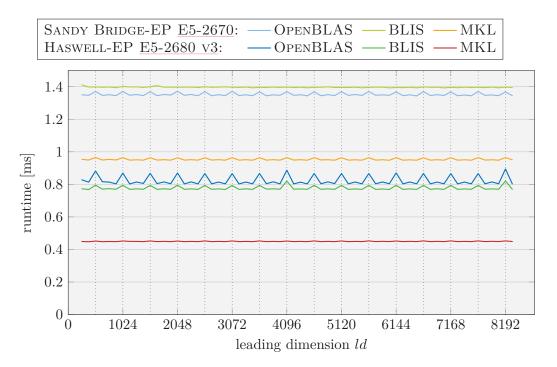

|   |     | 3.1.3  | Leading Dimension Arguments                  | 51 |

|   |     |        | 3.1.3.1 Alignment to Cache-Lines             | 51 |

|   |     |        | 3.1.3.2 Set-Associative Cache Conflicts      | 52 |

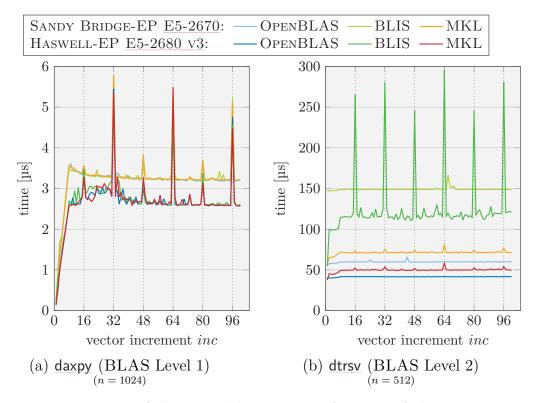

|   |     | 3.1.4  | Increment Arguments                          | 55 |

|   |     | 3.1.5  | Size Arguments                               | 57 |

|   |     |        | 3.1.5.1 Smalls Scale Behavior                | 58 |

|   |     |        | 3.1.5.2 Piecewise Polynomial Behavior        | 59 |

|   |     | 3.1.6  | Data Arguments                               | 61 |

|   |     | 3.1.7  | Summary                                      | 63 |

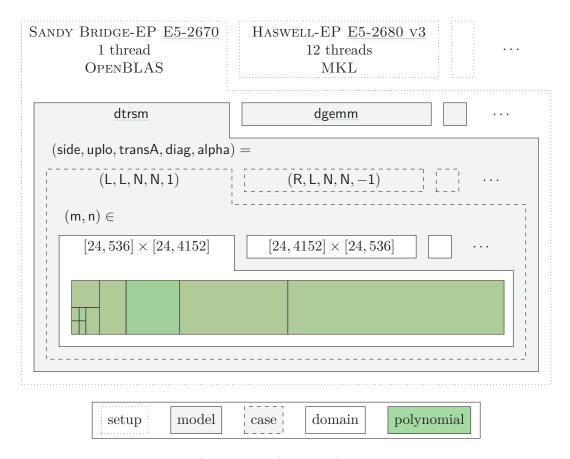

|   | 3.2 | Model  | l Generation                                 | 64 |

|   |     | 3.2.1  | Model Structure                              | 65 |

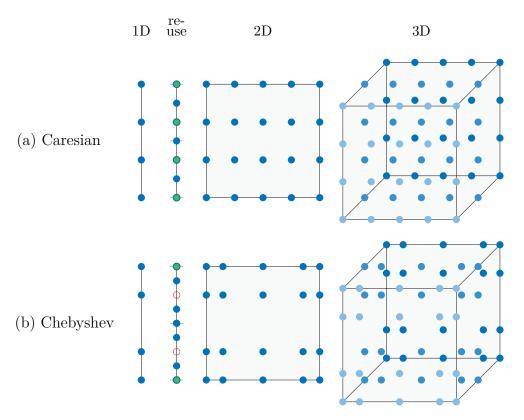

|   |     | 3.2.2  | Sample Distribution                          | 67 |

|   |     | 3.2.3  | Repeated Measurements and Summary Statistics | 69 |

|   |     | 3.2.4  | Relative Least-Squares Polynomial Fitting    | 70 |

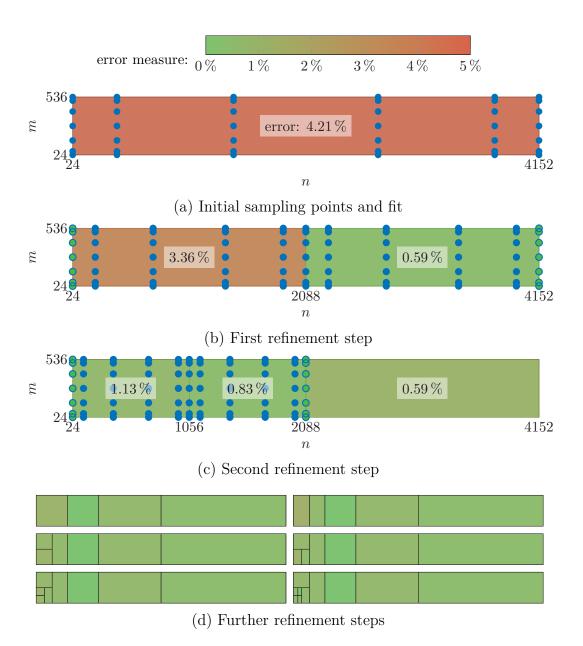

|   |     | 3.2.5  | Adaptive Refinement                          | 72 |

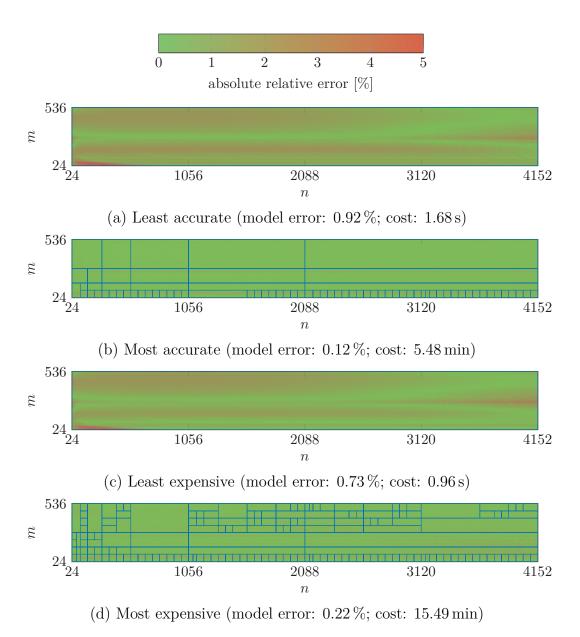

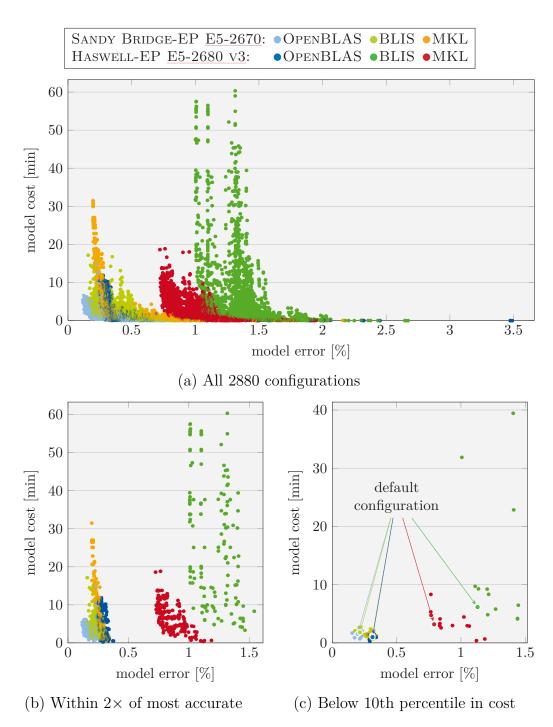

|   | 3.3 | Model  | Generator Configuration                      | 75 |

|   |     | 3.3.1  | Configuration Parameters                     | 75 |

|   |     | 3.3.2  | Trade-Off and Configuration Selection        | 77 |

|   |     | 3.3.3  | Variations of the Default Configuration      | 83 |

|   | 3.4 | Summ   | nary                                         | 83 |

|   |     |        |                                              |    |

| 4 Mo | del-Ba | sed Predictions for Blocked Algorithms                               |

|------|--------|----------------------------------------------------------------------|

| 4.1  | Perfor | rmance Prediction                                                    |

| 4.2  | Accur  | acy Quantification                                                   |

| 4.3  | Accur  | acy Case Study: Cholesky Decomposition                               |

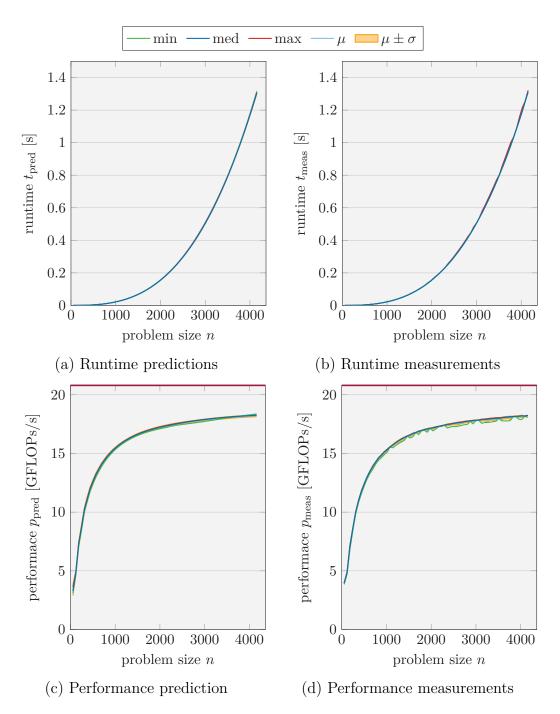

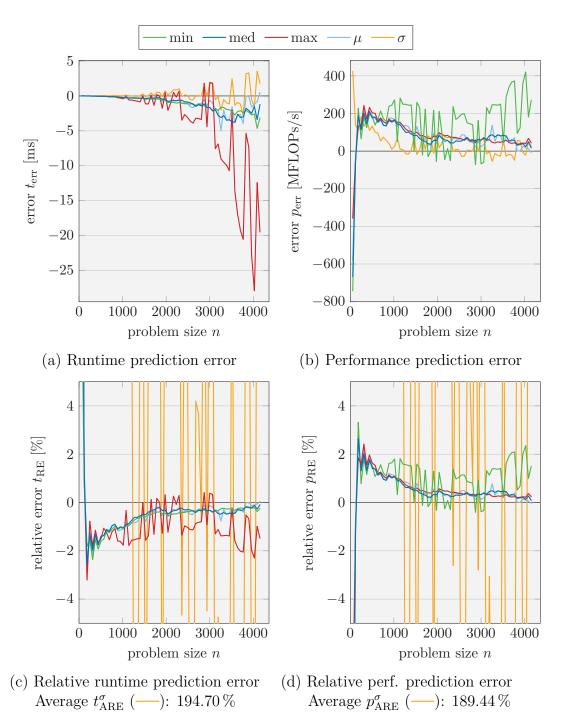

|      | 4.3.1  | Varying Problem Size                                                 |

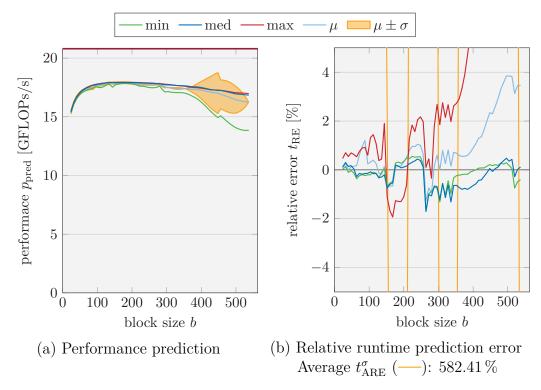

|      | 4.3.2  | Varying Block Size                                                   |

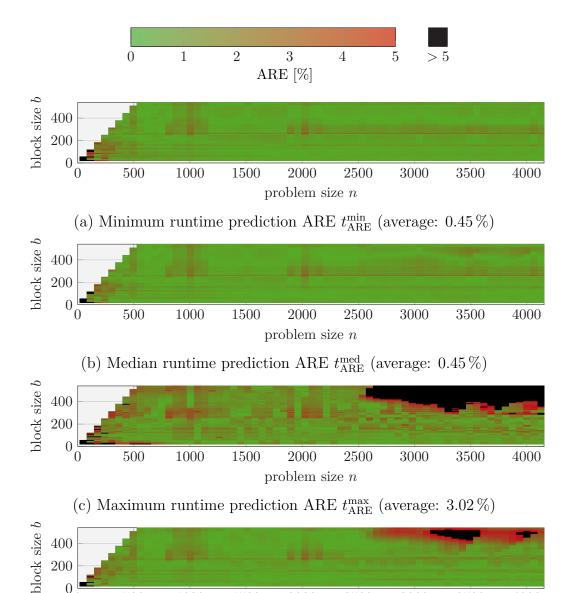

|      | 4.3.3  | Varying Problem Size and Block Size                                  |

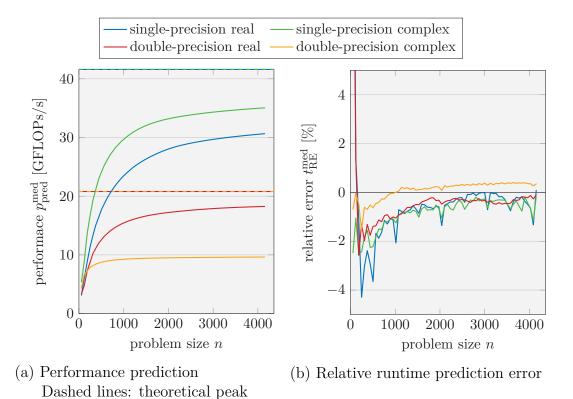

|      | 4.3.4  | Other Data-Types                                                     |

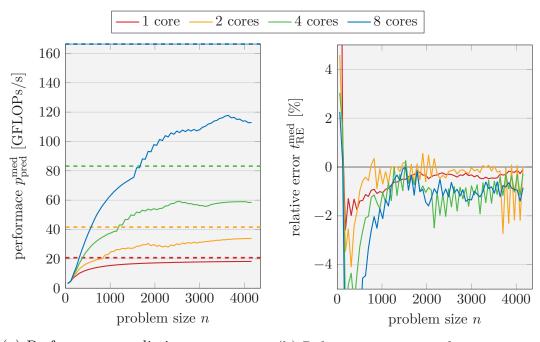

|      | 4.3.5  | Multi-Threaded BLAS                                                  |

|      | 4.3.6  | Summary                                                              |

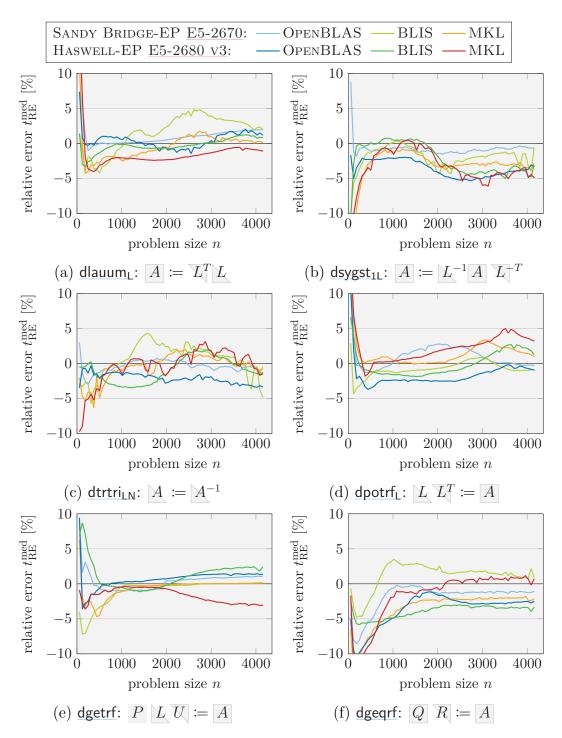

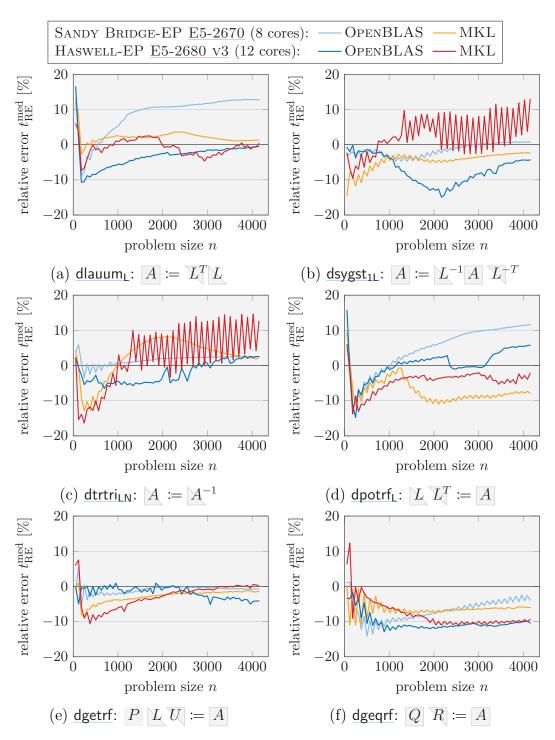

| 4.4  | Accur  | eacy Study: Blocked LAPACK Algorithms                                |

|      | 4.4.1  | Single-Threaded BLAS                                                 |

|      | 4.4.2  | Multi-Threaded BLAS                                                  |

|      | 4.4.3  | Summary                                                              |

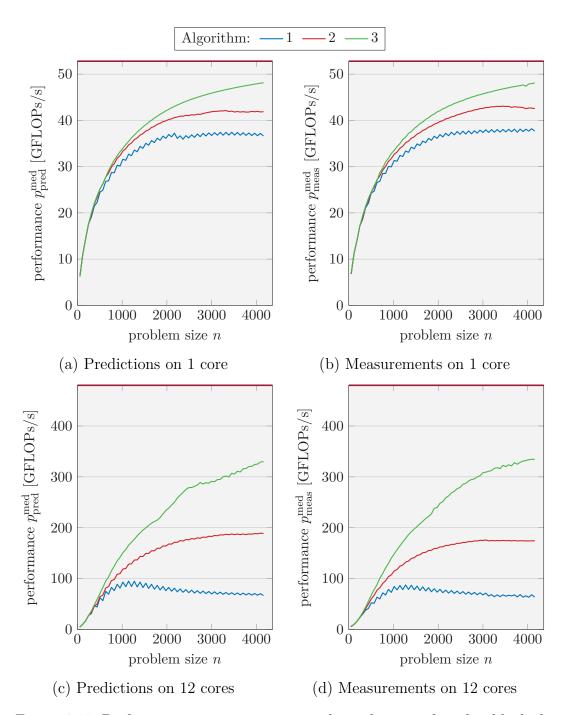

| 4.5  | Algori | ithm Selection                                                       |

|      | 4.5.1  | Cholesky Decomposition                                               |

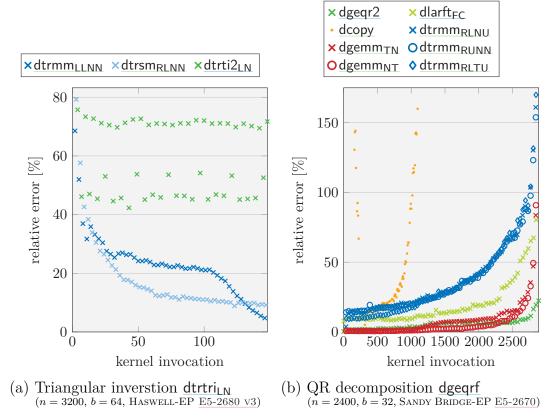

|      | 4.5.2  | Triangular Inversion                                                 |

|      | 4.5.3  | Sylvester Equation Solver                                            |

|      |        | 4.5.3.1 Algorithms                                                   |

|      |        | 4.5.3.2 Algorithm Selection                                          |

|      | 4.5.4  | Summary                                                              |

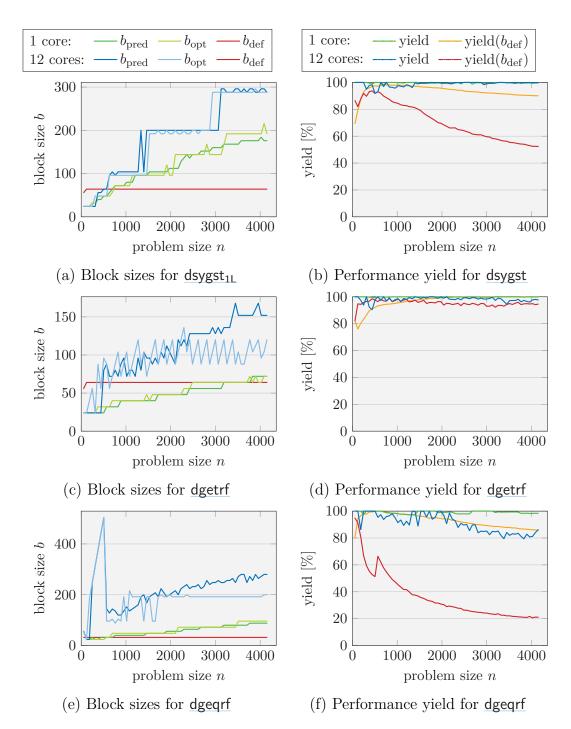

| 4.6  | Block  | Size Optimization                                                    |

|      | 4.6.1  | Cholesky Decomposition                                               |

|      | 4.6.2  | Triangular Inversion                                                 |

|      | 4.6.3  | LAPACK Algorithms                                                    |

| 4.7  | Summ   | nary                                                                 |

| Cad  | che Mo | odeling and Prediction                                               |

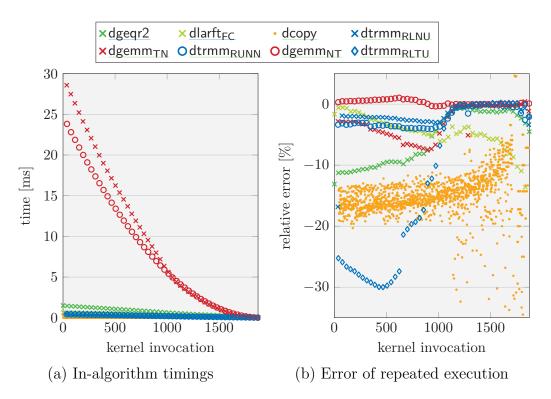

| 5.1  | Case   | Study: QR Decomposition on a Harpertown $\underline{\text{E5450}}$ . |

|      | 5.1.1  | Timing Kernels in LAPACK's <u>dgeqrf</u>                             |

|      | 5.1.2  | Cache-Aware Timings                                                  |

|      | 5.1.3  | Modeling the Cache                                                   |

|              |     | 5.1.4  | Varying the Setup                                            | 144 |

|--------------|-----|--------|--------------------------------------------------------------|-----|

|              | 5.2 | Applie | cation to Other Algorithms                                   | 146 |

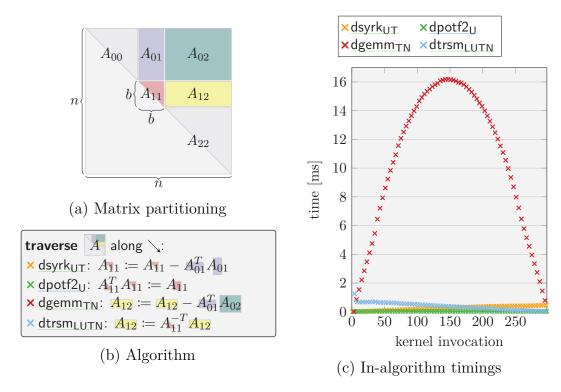

|              |     | 5.2.1  | Cholesky Decomposition: dpotrf <sub>U</sub>                  | 147 |

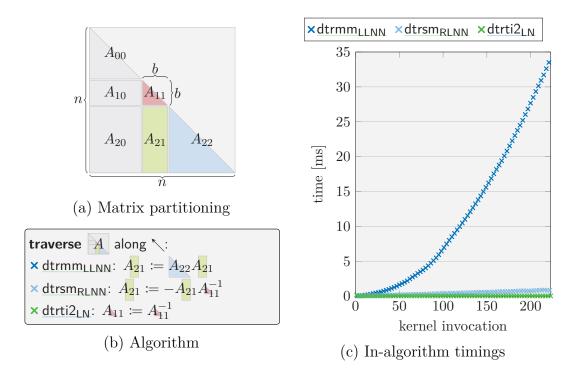

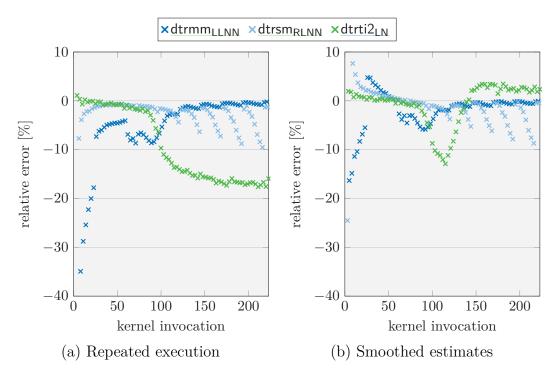

|              |     | 5.2.2  | Inversion of a Triangular Matrix: dtrtri <sub>LN</sub>       | 148 |

|              |     | 5.2.3  | Summary                                                      | 149 |

|              | 5.3 | Feasib | oility on Modern Hardware                                    | 150 |

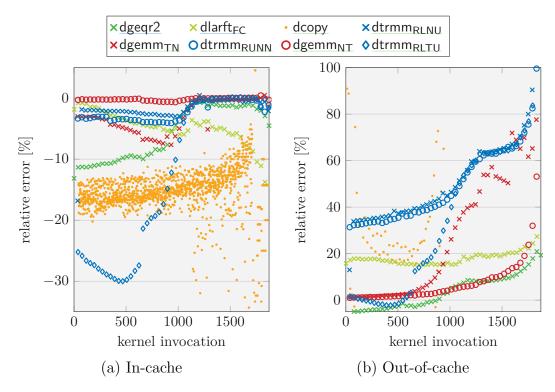

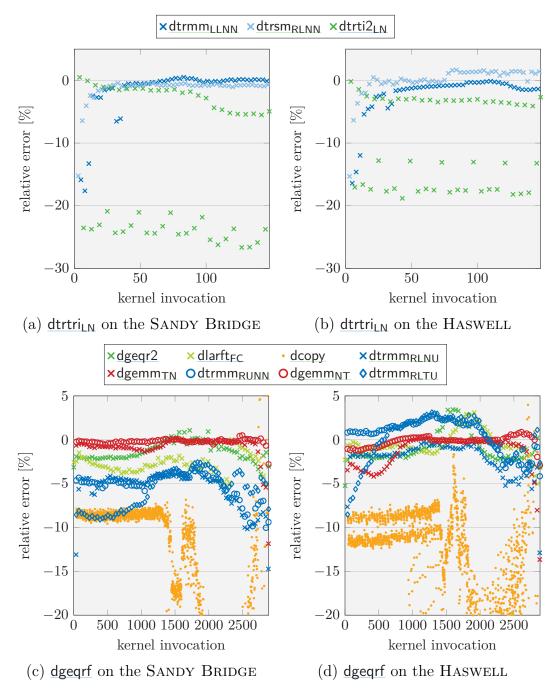

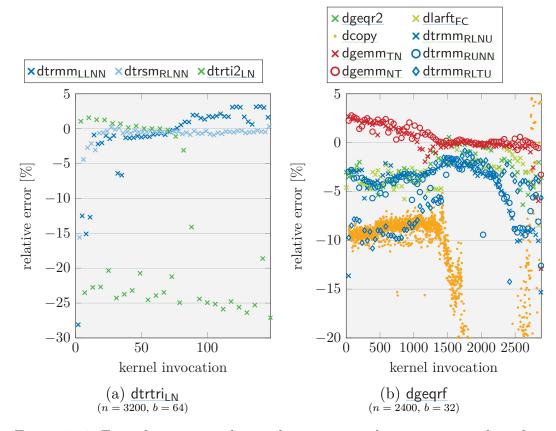

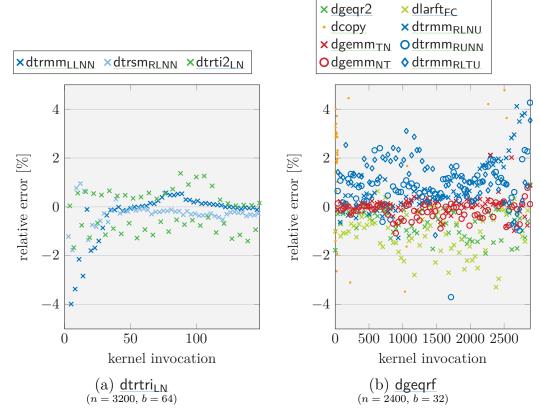

|              |     | 5.3.1  | In- and Out-of-Cache Timings                                 | 151 |

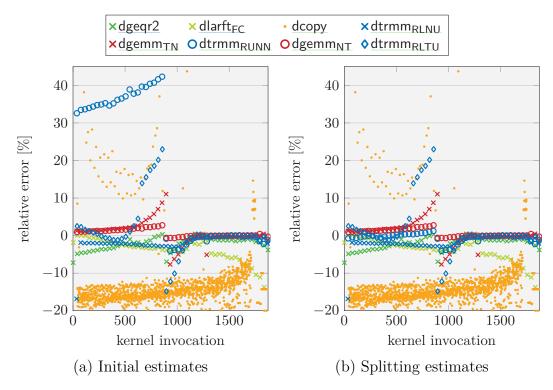

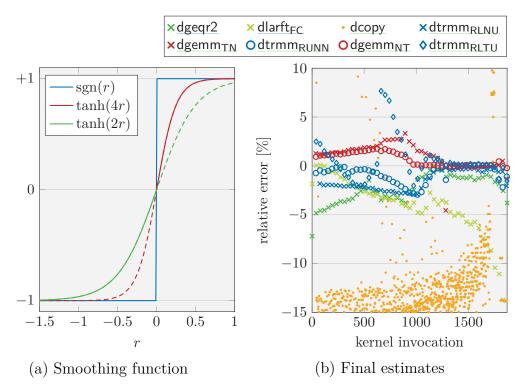

|              |     | 5.3.2  | Algorithm-Aware Timings                                      | 155 |

|              | 5.4 | Summ   | nary                                                         | 157 |

| 6            | Mic | ro-Bei | nchmarks for Tensor Contractions 1                           | .59 |

|              | 6.1 | Algori | ithm Generation                                              | 160 |

|              | 6.2 | Runtin | me Prediction                                                | 164 |

|              |     | 6.2.1  | Example Contraction: $C_{abc} := A_{ai}B_{ibc}$              | 165 |

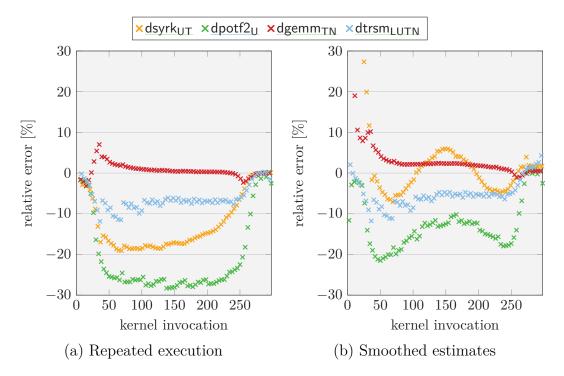

|              |     | 6.2.2  | Repeated Execution                                           | 167 |

|              |     | 6.2.3  | Operand Access Distance                                      | 169 |

|              |     | 6.2.4  | Cache Prefetching                                            | 174 |

|              |     | 6.2.5  | Prefetching Failures                                         | 176 |

|              |     | 6.2.6  | First Loop Iterations                                        | 177 |

|              | 6.3 | Result | ts                                                           | 179 |

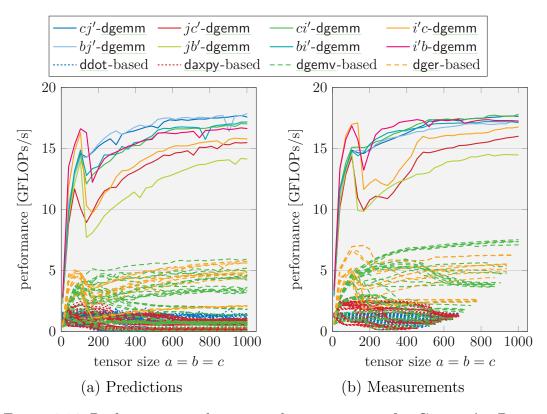

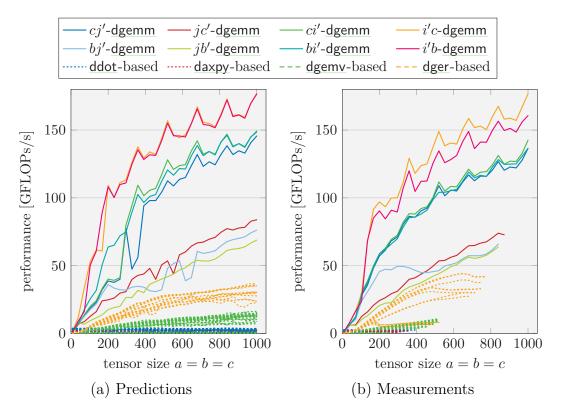

|              |     | 6.3.1  | Changing the Setup for $C_{abc} := A_{ai}B_{ibc}$            | 180 |

|              |     | 6.3.2  | Vector Contraction: $C_a := A_{iaj}B_{ji} \dots \dots \dots$ | 181 |

|              |     | 6.3.3  | Challenging Contraction: $C_{abc} := A_{ija}B_{jbic}$        | 182 |

|              |     | 6.3.4  | Efficiency Study                                             | 186 |

|              | 6.4 | Summ   | nary                                                         | 187 |

| 7            | Cor | clusio | $_{ m n}$                                                    | 89  |

|              | 7.1 | Outlo  | ok                                                           | 190 |

| $\mathbf{A}$ | Ter | minolo | ogy: Performance and Efficiency 1                            | 91  |

|              | A.1 | Workl  | oad                                                          | 192 |

|              |     | A.1.1  | Floating-Point Operations                                    | 192 |

|              |     | A.1.2  | Data Volume and Movement                                     | 194 |

|              |       | A.1.3 Arithmetic Intensity               | 195 |

|--------------|-------|------------------------------------------|-----|

|              | A.2   | Runtime                                  | 197 |

|              | A.3   | Performance and Attained Bandwidth       | 198 |

|              | A.4   | Hardware Constraints                     | 199 |

|              | A.5   | Efficiency                               | 202 |

|              |       | A.5.1 Compute-Bound Efficiency           | 202 |

|              |       | A.5.2 Bandwidth-Bound Efficiency         | 204 |

|              |       | A.5.3 The Roofline Model                 | 205 |

|              | A.6   | Other Metrics                            | 208 |

| В            | Den   | se Linear Algebra Routines and Libraries | 209 |

|              | B.1   | Storage Format                           | 209 |

|              |       | B.1.1 Scalars                            | 210 |

|              |       | B.1.2 Vectors                            | 210 |

|              |       | B.1.3 Matrices                           | 210 |

|              | B.2   | Basic Linear Algebra Subprograms         | 211 |

|              |       | B.2.1 BLAS Level 1                       | 212 |

|              |       | B.2.2 BLAS Level 2                       | 213 |

|              |       | B.2.3 BLAS Level 3                       | 214 |

|              | B.3   | LINEAR ALGEBRA PACKAGE                   | 218 |

|              | B.4   | Implementations                          | 225 |

| $\mathbf{C}$ | Har   | dware                                    | 229 |

|              | C.1   | Harpertown E5450                         | 229 |

|              | C.2   | Sandy Bridge-EP E5-2670                  | 230 |

|              |       | IVY Bridge-EP E5-2680 v2                 | 230 |

|              | C.4   | Haswell-EP E5-2680 v3                    | 231 |

|              | C.5   | Broadwell 17-5557U                       | 232 |

| Li           | st of | Examples                                 | 233 |

| Li           | st of | Figures                                  | 237 |

| List of Tables | 243 |

|----------------|-----|

| Bibliography   | 245 |

Software developers in scientific computing are often faced with performance-critical decisions such as the choice of algorithms, configuration parameters, hardware platforms, and software libraries. This dissertation presents novel techniques and tools to guide such decisions for dense linear algebra computations with accurate yet fast performance predictions. These predictions avoid the otherwise common exhaustive execution and timing of all potential alternatives, and thereby shorten the decision-making process both in compute time and developer effort.

The task of accurately predicting the performance of dense linear algebra algorithms is particularly challenging due to the complexity of the performance-related factors: The runtime of compute-kernels is not only non-linear in the problem size due to multi-threading and kernel-internal caching effects, but is also influenced by data locality and caching in sequences of such kernels. As a result, analytical performance predictions are either extremely rough and complex, or hardware-dependent; in contrast, this work investigates measurement-based techniques that are tailored to represent the kernel-specific performance effects.

The goal of measurement-based predictions is to estimate the performance of an algorithm both accurately and notably faster than the algorithm execution itself. These requirements lead to two practical alternatives as the basis for performance predictions: an algorithm-independent database of performance models for the building blocks that are automatically generated once per platform, or micro-benchmarks that execute a fraction of the algorithm's building blocks and extrapolate their runtime. Neither of these alternatives is applicable in all situations, and which one is more suitable depends on the type algorithm. By addressing two different types of operations that are at

the core of many dense computations, this work investigates both alternatives: Blocked algorithms are predicted through algorithm-independent performance models, and tensor contraction algorithms are predicted through cache-aware micro-benchmarks.

#### Contributions

The main contributions of this work are the following:

- ELAPS, a lightweight yet portable and universal performance measurement framework for dense linear algebra routines and algorithms,

- Methods and tools for the automated generation of highly accurate performance models for compute kernels,

- Model-based performance predictions of blocked algorithms for optimal algorithm selection and configuration,

- A study on the influence of caching on kernel invocations within blocked algorithms, and

- Cache-aware micro-benchmarks to predict BLAS-based tensor contractions for optimal algorithm selection.

#### Outline

The remainder of this dissertation is structured as follows:

- Chapter 1 proceeds to introduce blocked algorithms and tensor contractions, and motivates our performance prediction goals in Sections 1.1 and 1.2. It concludes with an overview of related work in Section 1.3.

- Chapter 2 addresses common performance characteristics of compute kernels, and introduces ELAPS, a novel framework for performance measurements that serves as the basis for the following Chapters.

- Chapter 3 presents the design and automatic generation of performance models, and analyzes their accuracy.

- Chapter 4 uses such models to predict the runtime and performance of blocked algorithms and subsequently select platform-specific optimal algorithm configurations.

- Chapter 5 studies the influence of caching on the runtime of compute kernels within blocked algorithms and the feasibility of accounting for caching effects in predictions.

- Chapter 6 is devoted to predicting the performance of BLAS-based tensor contractions. It describes the creation of cache-aware micro-benchmarks that, for a given contraction, allow to identify the fastest algorithm(s).

- Chapter 7 concludes this dissertation, summarizes the presented techniques and results, and gives an overview of potential extensions of this work.

The main chapters are supplemented by three appendices:

- Appendix A introduces readers new to high-performance computing to performance-related terminology and concepts.

- Appendix B gives an overview of the BLAS and LAPACK interfaces, their kernels used in this work, and relevant implementations.

- Appendix C details the hardware used throughout this work.

# 1.1 Performance Modeling for Blocked Algorithms

We aim to predict the performance of blocked algorithms with the goals of 1) selecting the fastest algorithm from a set of mathematically equivalent alternatives, and 2) tuning their algorithmic block size. In the following, Section 1.1.1 introduces the concept of blocked algorithms, and exposes their inherent optimization challenges, and Section 1.1.2 gives a brief overview of our approach to address these challenges using on performance models.

Readers familiar with blocked algorithms and the influence of block sizes may skip the introduction to these concepts in Section 1.1.1, and focus on our prediction approach in Section 1.1.2 on Page 9.

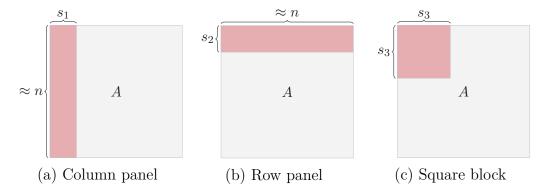

## 1.1.1 Motivation: Blocked Algorithms

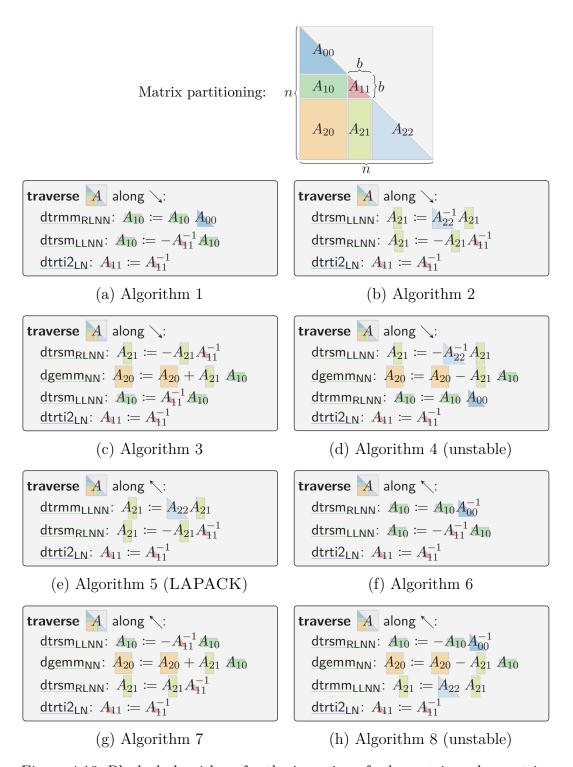

Blocked algorithms are commonly used to exploit the performance of optimized BLAS Level 3 kernels<sup>1</sup> in other matrix operations, such as decompositions, inversions, and reductions. Every blocked algorithm traverses its input matrix (or matrices) in steps of a fixed block size; in each step of this traversal, it exposes a set of sub-matrices to which it applies a series of updates. Through these updates, it progresses with the computation and obtains a portion of the operation's result; once the matrix traversal completes, the entire result is computed.

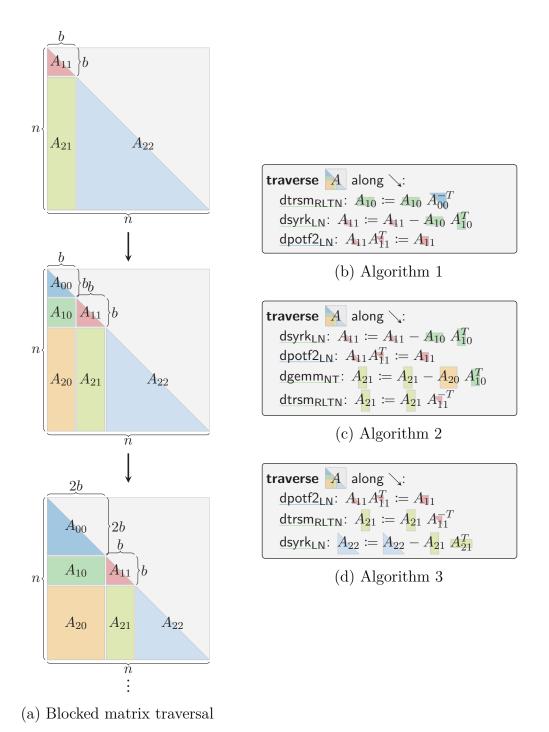

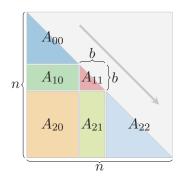

Example 1.1: Blocked algorithms for the Cholesky decomposition Figure 1.1 illustrates blocked algorithms for a simple yet representative operation: the lower-triangular Cholesky decomposition

$$L$$

$L^T \coloneqq A$

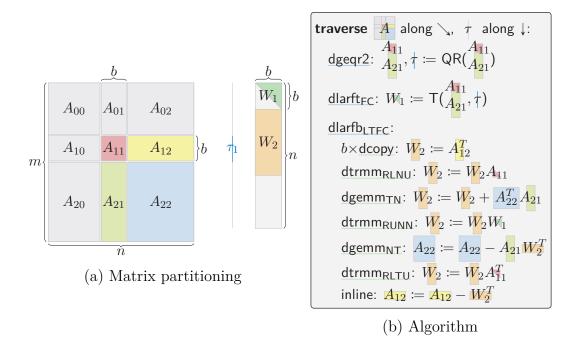

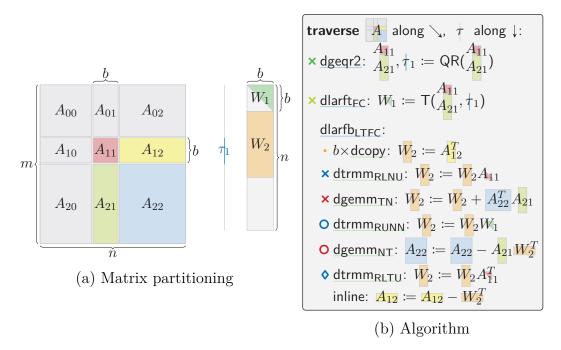

of a symmetric positive definite (SPD) matrix  $A \in \mathbb{R}^{n \times n}$  in lower-triangular storage (LAPACK:  $\underline{\mathsf{dpotrf}}_{\mathsf{L}^2}$ ). For this operation there exist three different blocked algorithms. Each algorithm traverses A diagonally from the top-left to the bottom-right  $\searrow$  and computes the Cholesky factor  $\underline{L}$  in place. At each step of the traversal, the algorithm exposes the sub-matrices shown in Figure 1.1a and makes progress by applying the algorithm-dependent updates in Figures 1.1b to 1.1d. Before these updates, the sub-matrix  $A_{00}$ ,

<sup>&</sup>lt;sup>1</sup> The Basic Linear Algebra Subprograms (BLAS) form the basis for high-performance in dense linear algebra. See Appendices A and B.

<sup>&</sup>lt;sup>2</sup> Appendix B gives an overview of the BLAS and LAPACK routines used throughout this work. When specified, the subscripts indicate the values of the flag arguments, which identify the variant of the operation; e.g., in  $\underline{dpotrf}_L$  the L corresponds to the argument uplo indicating a lower-triangular decomposition.

Figure 1.1: Blocked algorithms for the lower-triangular Cholesky decomposition.

which in the first step is of size  $0 \times 0$ , already contains a portion of the Cholesky factor L; after the updates, the sub-matrices  $A_{10}$  and  $A_{11}$  also contain their portions of L, and in the next step become part of  $A_{00}$ . Once the traversal reaches the bottom-right corner (i.e.,  $A_{00}$  is now of size  $n \times n$ ), the entire matrix is factorized.

Blocked algorithms pose two optimization challenges:

- For each operation there typically exist several *alternative algorithms*, which are mathematically equivalent in exact arithmetic; however, even if such algorithms perform the same number of floating point operations, they may differ significantly in performance.

- For each algorithm, the *block size* influences the number of traversal steps and the sizes and shapes of the exposed sub-matrices, and thus the performance of the kernels applied to them.

What makes matters more complicated is that the optimal choice depends on various factors, such as the hardware, the number of threads, the kernel implementations, and the problem size.

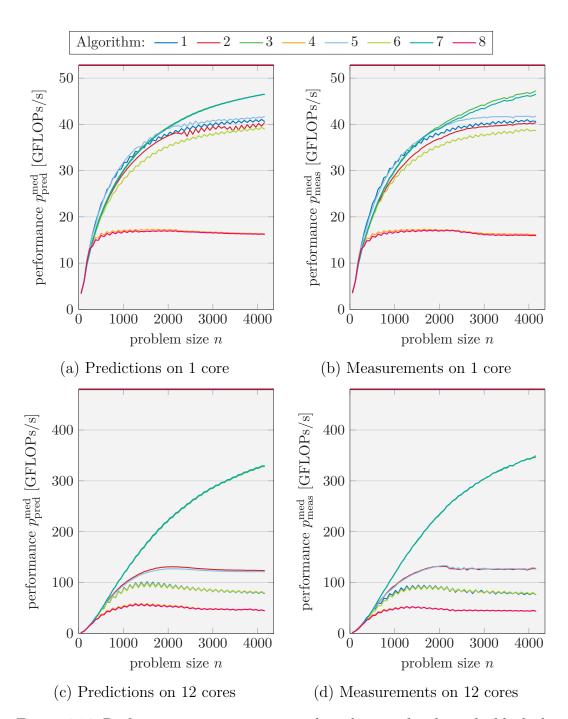

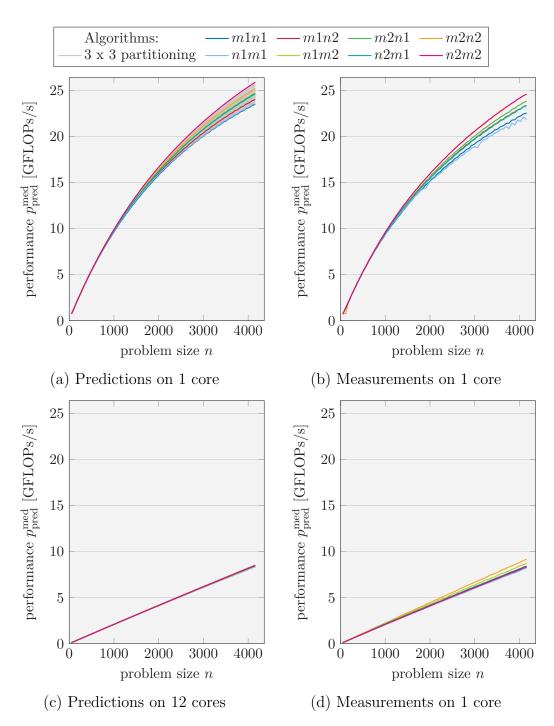

#### Example 1.2: Performance of alternative algorithms

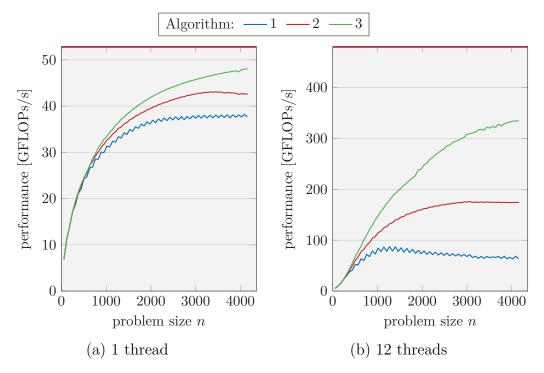

Figure 1.2 shows the performance of the three blocked Cholesky decompositions from Figure 1.1 with block size b=128 and increasing problem size n on a 12-core HASWELL-EP <u>E5-2680 v3</u><sup>3</sup> with single- and multi-threaded OPENBLAS.

In both the single- and multi-threaded scenarios, algorithm 3 (—) is the fastest among the three alternatives for all problem sizes. On a single core and for problem size n=4152, it is 27.40% and 12.89% faster than, respectively, algorithms 1 (—) and 2 (—), and it reaches up to 91.01% of the processor's theoretical peak performance (red line — at the top of the plot). On all 12 of the processor's cores, algorithm 3 (—) still reaches an efficiency of 69.70%, and outperforms algorithms 1 (—) and 2 (—) by, respectively,  $5.21\times$  and  $1.92\times$ .

<sup>&</sup>lt;sup>3</sup> Appendix C provides an overview of the processors used throughout this work.

Figure 1.2: Performance of the three blocked Cholesky decomposition algorithms.

(b = 128, HASWELL-EP E5-2680 V3, OPENBLAS, median of 10 repetitions)

Although algorithm 3 (—) is clearly the fastest in this and many other scenarios, LAPACK's dpotrf<sub>L</sub> implements algorithm 2 (—).

For other operations, the choice becomes more complicated, since no single algorithm is the fastest for all problem sizes and scenarios. For instance, for the single-threaded inversion of a lower-triangular matrix  $A := A^{-1}$ , two different algorithms are the fastest for small and large matrices; with the performance differing by up to 13% in either direction (Section 4.5.2).

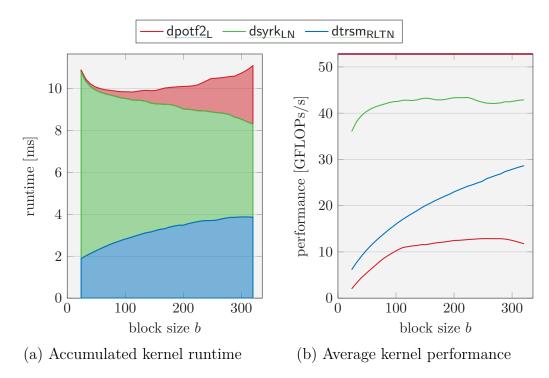

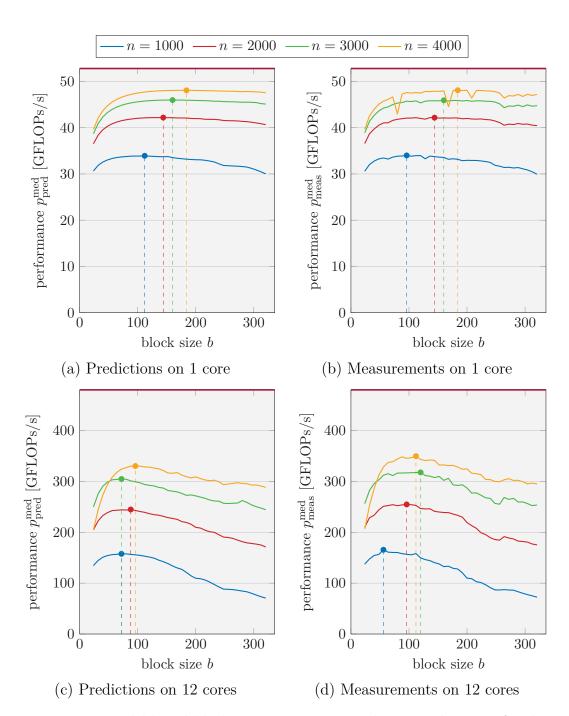

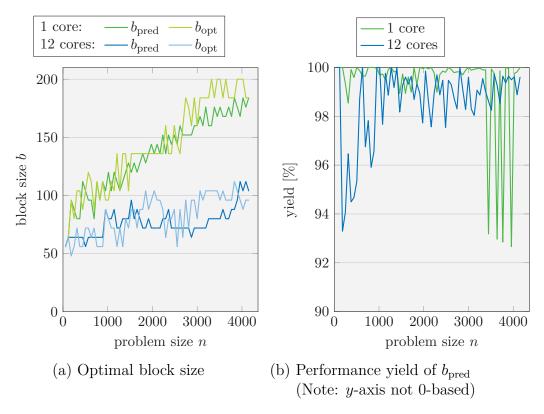

#### Example 1.3: Influence of the block size on performance

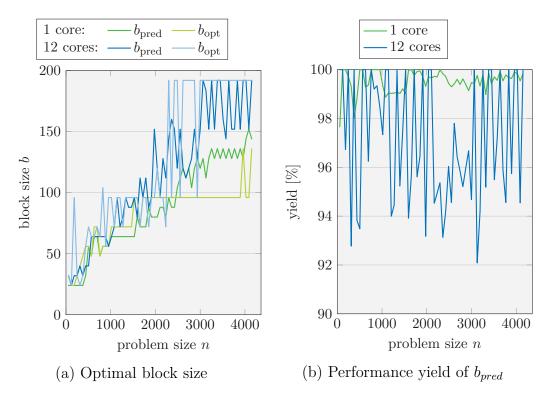

Let us consider the blocked Cholesky decomposition algorithm 3 (— in Figure 1.2) with fixed problem sizes n=1000, 2000, 3000, and 4000 and varying block size b. Figure 1.3 presents the performance of these algorithm executions for 1 and 12 threads on the HASWELL-EP <u>E5-2680 v3</u> using OPENBLAS: Single-threaded, the optimal block size increases from b=96

Figure 1.3: Performance of the blocked Cholesky decompositions algorithm 3 for varying block sizes.

(HASWELL-EP E5-2680 v3, OPENBLAS, median of 10 repetitions)

for n=1000 to b=184 for n=4000. On 12 cores, on the other hand, the performance is less smooth and the optimal choices for b are between 56 and 112.

Figure 1.3 demonstrates the importance of selecting the block size dynamically: If we use b=184, which is optimal for n=4000 on one core, for n=1000 on 12 cores we only reach 77.62% of the algorithm's optimal performance. On the other hand, LAPACK's default block size b=64 (which is close to the optimal b=56 for n=1000 on 12 cores) would reach 95.95% of the optimal single-threaded performance for n=4000.

## 1.1.2 Prediction through Performance Models

Naturally, both the best algorithm and its optimal block size for a given scenario (operation, problem size, hardware, kernel library, multi-threading) can be determined through exhaustive performance measurements; however, this is extremely time consuming and thus often impractical. Instead we aim to determine the optimal configuration without executing any of the alternative algorithms. For this purpose, we use the hierarchical structure of blocked algorithms: Their entire computation is performed in a series of calls to a few kernel routines; hence, by accurately estimating the runtime of these kernels, we can predict an entire algorithm's runtime and performance.

In order to estimate the kernel runtimes, let us study how these kernels are used: In each algorithm execution, the same set of kernels is invoked repeatedly—once for each step of the blocked matrix traversal. Each invocation, however, works on operands of different size depending on the progress of the algorithms' traversal, the input problem size, and the block size. In short, we need to estimate the performance of only a few kernels, yet with potentially wide ranges of operand sizes.

Our solution is *performance modeling*, as detailed in Chapter 3: Based on a detailed study of how a kernel's arguments (i.e., flags, operand sizes, etc.) affect its performance, we design performance models in the form of piecewise multivariate polynomials. These models are generated automatically once for each hardware and software setup and subsequently provide accurate performance estimates at a tiny fraction of the kernel's runtime.

Using such estimates, we *predict* the *performance* of blocked algorithms, as presented in Chapter 4. These fast predictions prove to be highly accurate, and allow us to both rank the blocked algorithms for a given operation according to their performance, and find near-optimal values for the algorithmic block sizes.

While our models yield accurate performance estimates for individual kernel executions, they do not capture the performance influence of *caching* between kernels. Prior to the invocation of each compute kernel in an algorithm, typically only a portion of its operands are in cache, and loading operands from main

memory increases the kernel runtime. Chapter 5 investigates how caching effects can be accounted for in blocked algorithms, and attempts to combine pure in- and out-of-cache estimates into more accurate prediction. However, while the results look promising on a rather old HARPERTOWN <u>E5450</u>, the analysis reveals that on modern processors the effect caching on kernel performance is so complex that accounting for it in algorithm-independent performance models to further improve our prediction accuracy is infeasible.

# 1.2 Micro-Benchmarks for Tensor Contractions

Tensor contractions play an increasingly important role in various scientific computations, such as machine learning [13], general relativity [62, 64], and quantum chemistry [21, 34]. Following a brief introduction to BLAS-based tensor contraction algorithms and their performance in Section 1.2.1, Section 1.2.2 gives an overview of how predictions based on micro-benchmarks are used to rank alternative algorithms for a given contraction.

# 1.2.1 Motivation: Tensor Contraction Algorithms

Computationally, tensor contractions are generalizations of matrix-vector and matrix-matrix products to operands of higher dimensionality. While BLAS covers contractions of up to two-dimensional operands (i.e., matrices), there are no equivalently established and standardized high-performance libraries for general tensor contractions. Fortunately, just as a matrix-matrix products can be decomposed into sequences of matrix-vector products, higher dimensional tensor contractions can be cast in terms of matrix-matrix or matrix-vector kernels. (A broader overview of alternative approaches is given in Section 1.3.4.)

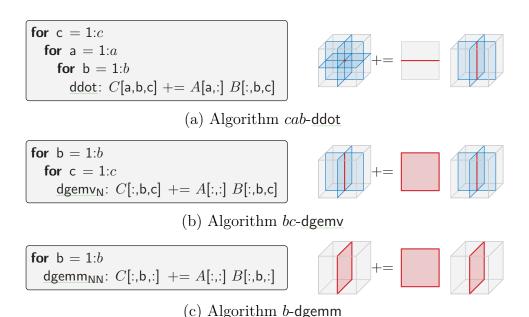

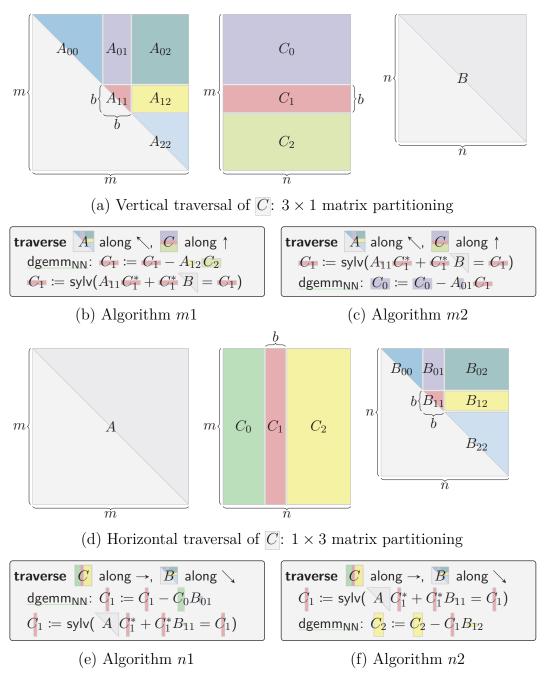

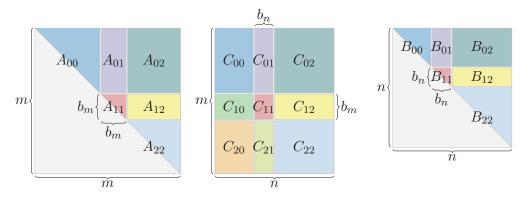

#### Example 1.4: Tensor contraction algorithms

Let us consider the contraction  $C_{abc} := A_{ai}B_{ibc}$  (in Einstein notation), which

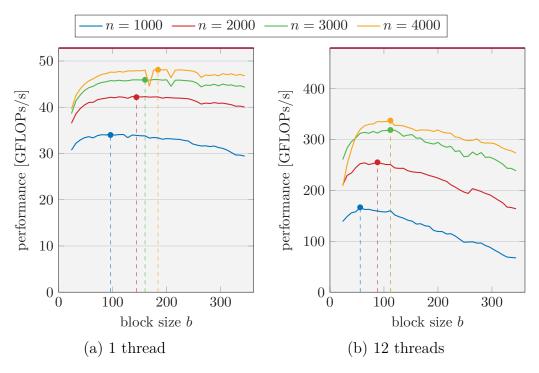

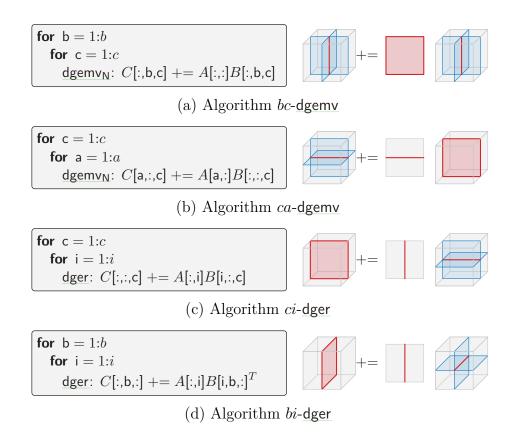

Figure 1.4: Sample of algorithms for the tensor contraction  $C_{abc} := A_{ai}B_{ibc}$ . All slicings are visualized in blue; the kernel operands (the intersections) are in red. The name of each algorithm stems from the dimensions its **for**-loops index and its BLAS kernel.

is visualized as follows:

$$a \quad C := a \quad A \quad i \quad B \quad c$$

The entries  $C[\mathsf{a},\mathsf{b},\mathsf{c}]$  of the resulting three-dimensional tensor  $C \in \mathbb{R}^{a \times b \times c}$  are computed as

$$\forall \mathsf{a} \forall \mathsf{b} \forall \mathsf{c}: \ C[\mathsf{a},\mathsf{b},\mathsf{c}] \coloneqq \sum_{\mathsf{i}} A[\mathsf{a},\mathsf{i}] B[\mathsf{i},\mathsf{b},\mathsf{c}] \ .$$

As further described in Section 6.1, this contraction can be performed by a total of 36 alternative algorithms, each consisting of one or more **for**-loops with a single BLAS kernel at its core. Three examples of such algorithms using BLAS Level 1, 2, and 3 kernels are shown in Figure 1.4. These

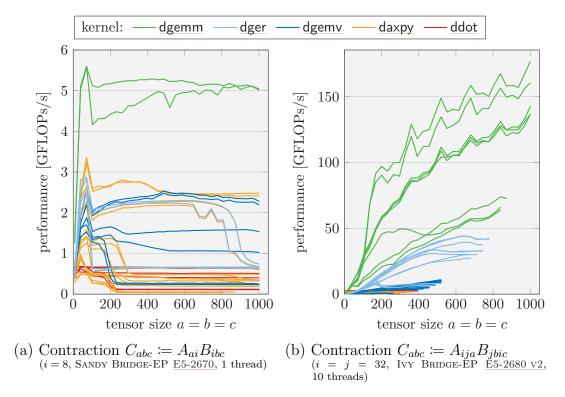

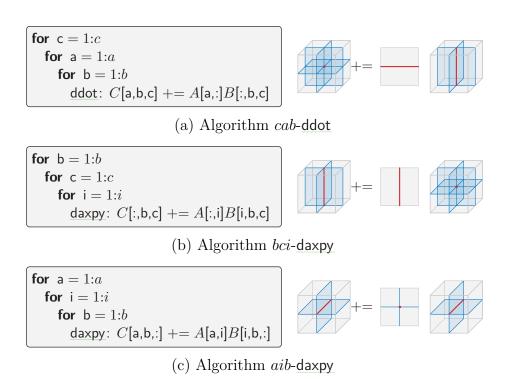

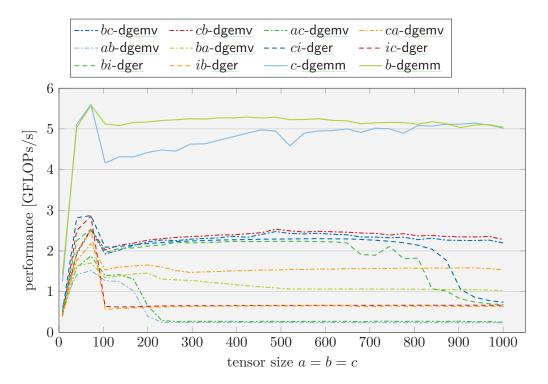

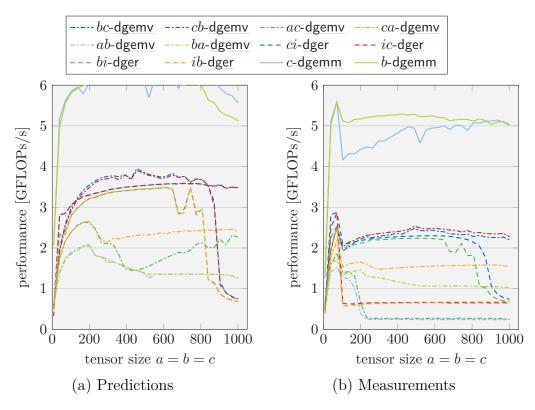

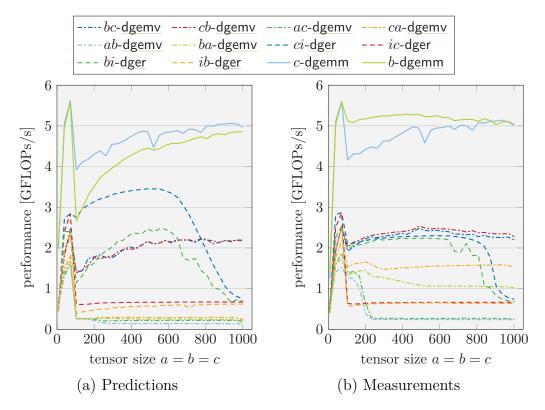

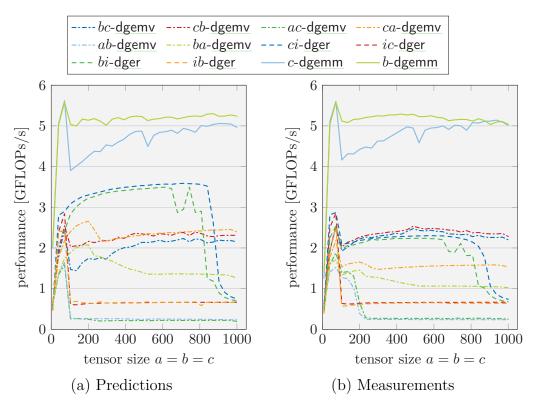

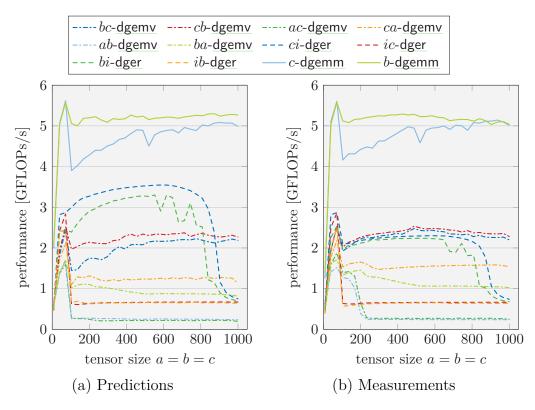

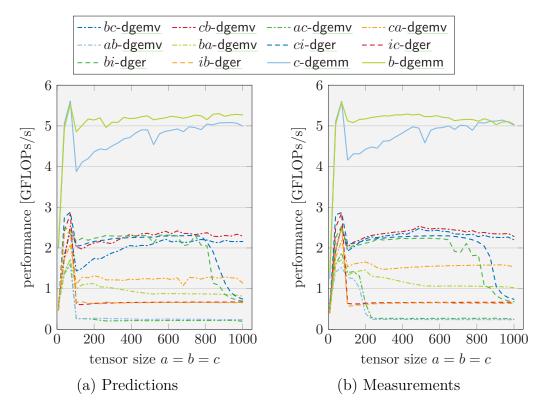

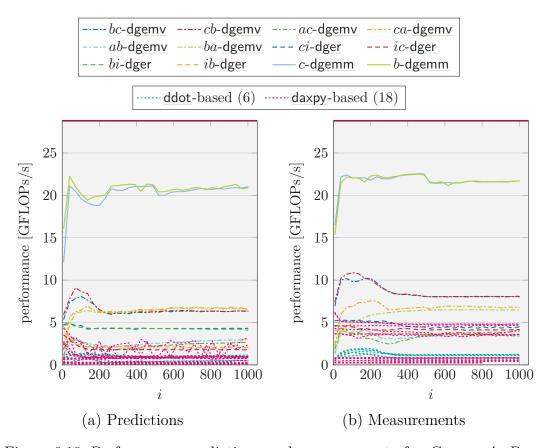

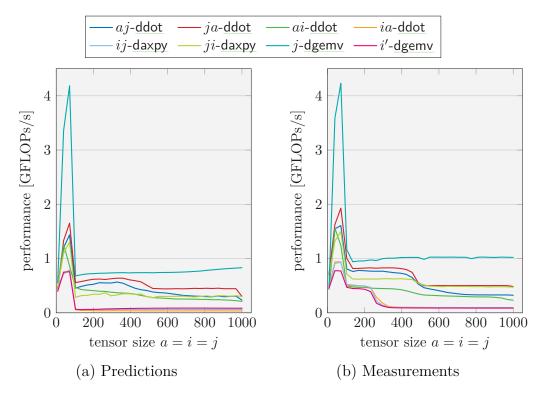

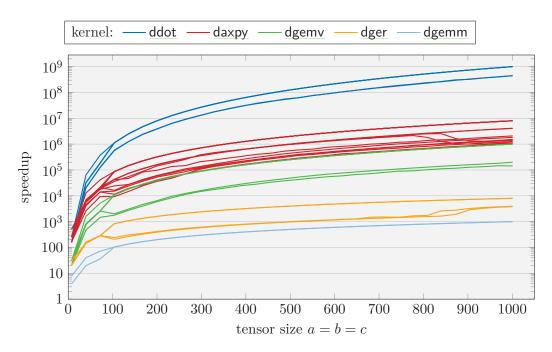

Figure 1.5: Performance of tensor contraction algorithms.

(OpenBLAS, median of 10 repetitions)

algorithms use MATLAB's ":" slicing notation<sup>4</sup> to access matrices and vectors within the tensors A, B, and C; the resulting operand shapes within the tensors passed to the BLAS kernel are shown alongside the algorithms.

Each tensor contraction can be computed via BLAS kernels through many—even hundreds—of algorithms, each with its own performance behavior. The optimization challenge of identifying the fastest among such a set of alternative algorithms is especially difficult due to the in practice commonly encountered skewed dimensions (i.e., one or more dimensions are extremely small) for which most BLAS implementations are typically not optimized.

<sup>&</sup>lt;sup>4</sup> The index ":" in a tensor refers to all elements along that dimension, e.g., A[a,:] is the a-th row of A.

#### Example 1.5: Performance of contraction algorithms

Let us consider the tensor contraction  $C_{abc} := A_{ai}B_{ibc}$  from Example 1.4 with tensors  $A \in \mathbb{R}^{n \times 8}$ ,  $B \in \mathbb{R}^{8 \times n \times n}$ , and thus  $C \in \mathbb{R}^{n \times n \times n}$ ; for n = 100, this can be visualized as follows:

$$a \qquad C \qquad := \ {}^{a}A \qquad {}_{i} \qquad {}^{B}B \qquad c \qquad .$$

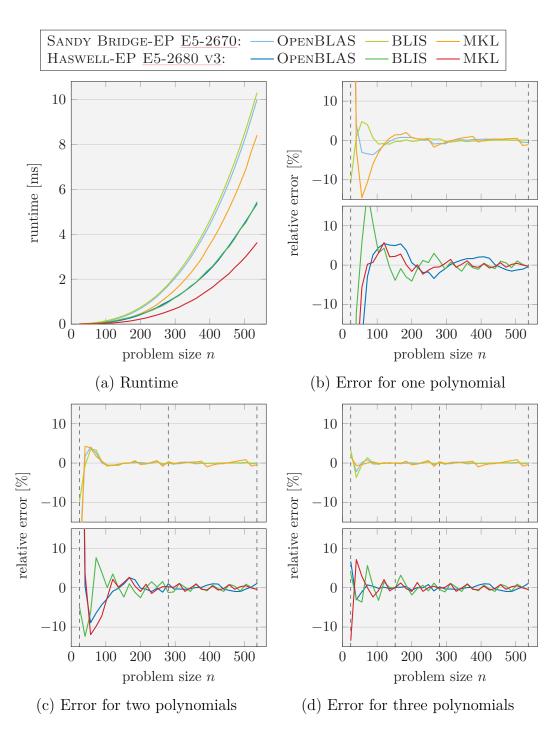

Figure 1.5a presents the performance of all 36 algorithms for this contraction on a HARPERTOWN <u>E5450</u> with single-threaded OPENBLAS. While the two <u>dgemm</u>-based algorithms (——) are clearly faster than the others, they differ in performance by up to 23.32%; with other kernels the difference are even more extreme, exceeding a factor of 60 for the <u>daxpy</u>-based algorithms (——).

Figure 1.5b showcases the performance of algorithms for the more complex contraction  $C_{abc} := A_{ija}B_{jbic}$  on all 10 cores of an IVY BRIDGE-EP <u>E5-2680 V2</u> using multi-threaded OPENBLAS. In this scenario, the performance of the <u>dgemm</u>-based algorithms alone differs by up to  $3\times$ .

One could argue that only <u>dgemm</u>-based algorithms are viable candidates to achieve the best performance; while for the most part this observation is true, due to skewed dimensions, even the performance of only these algorithms can differ dramatically. Furthermore, some contractions (e.g.,  $C_a := A_{iaj}B_{ji}$ ) cannot be implemented via <u>dgemm</u> in the first place. Therefore, we aim at the accurate prediction of any BLAS-based contraction, irrespective of which kernel is used.

# 1.2.2 Prediction through Micro-Benchmarks

At first sight the situation seems similar to the selection of blocked algorithms: We want to avoid exhaustive performance measurements and select the best algorithm *without executing* any of the alternatives; our strategy is once again to predict each algorithm's performance by estimating its invoked kernel's runtime.

However, while performance models accurately estimates the performance of such kernels for many operand sizes, they perform rather poorly for operations with skewed dimensions: For extremely thin or small operands, BLAS kernels exhibit strong size-dependent performance fluctuations, which are impractical to capture and represent in performance models.

While we cannot rely on performance models, analyzing the structure of tensor contraction algorithms suggests a different approach: In contrast to blocked algorithms, a contraction algorithm performs its entire computation in a series of calls to a single BLAS kernel of with operands of fixed size. Based on this observation, we estimate the performance of such calls by constructing a small set of micro-benchmarks that executes the kernel only a few times, and thus performs only a fraction of the algorithm's computation. Since memory locality plays an especially important role in contractions with skewed dimensions, we carefully recreate the stat of the processor's caches within the micro-benchmarks to time the kernel in conditions analogous to those in the actual algorithm.

Based on such micro-benchmarks, we can predict the total runtime of contraction algorithms for tensors of various shapes and sizes. These predictions reliably single out the fastest algorithm from a set of alternatives several orders of magnitude faster than a single algorithm execution.

## 1.3 Related Work

This overview of related research is structured as follows: Section 1.3.1 summarizes the history and state-of-the-art of dense linear algebra (DLA) libraries and algorithms, Section 1.3.2 addresses performance measurements and profiling tools, Section 1.3.3 presents performance modeling and prediction efforts, and Section 1.3.4 discusses developments in high-performance tensor contractions.

## 1.3.1 Dense Linear Algebra Libraries and Algorithms

We begin with a brief history of the fundamental DLA libraries BLAS and LAPACK and prominent implementations in Section 1.3.1.1. We then focus on blocked algorithms and their tuning opportunities in Section 1.3.1.2, and finally give an overview of alternative algorithms and libraries for distributed-memory and accelerator hardware in, respectively, Sections 1.3.1.3 and 1.3.1.4.

#### 1.3.1.1 BLAS and LAPACK

The development of standardized DLA libraries began in 1979 with the inception of the BASIC LINEAR ALGEBRA SUBPROGRAMS (BLAS) [63], a FORTRAN interface specification for, initially, various "Level 1" scalar and vector operations. It was subsequently extended to kernels for "Level 2" matrix-vector [40] and "Level 3" matrix-matrix [39] operations in, respectively, 1988 and 1990. The aim of the BLAS specification is to enable performance portable applications: DLA codes reach high performance on different hardware by using architecture-specific BLAS implementations. Although computer architectures have evolved dramatically in the last 40 years, this principle of performance portability is still at the core of all current DLA libraries.

The BLAS specification is accompanied by a reference implementation [96] that, while fully functional and well documented, is deliberately simple and thus slow; to reach high performance, users instead link with optimized BLAS implementations. The oldest open-source implementation still in use is the AUTOMATICALLY TUNED LINEAR ALGEBRA SOFTWARE (ATLAS) [85, 86, 87, 95], first released in 1997; this auto-tuning-based library's main proficiency is to yield decent performance on a wide range of hardware platforms with little developer and user effort. The first major open-source implementation hand-tuned for modern processors with cache hierarchies was GOTOBLAS [50, 51, 107]. It reaches up to around 90% of a processor's peak floating-point performance for both sequential and multi-threaded Level 3 kernels and good bandwidth-bound performance for Level 1 and 2 operations. After GOTOBLAS's discontinuation in 2010, its code-base and approach were picked up and

extended to more recent processors in the OPENBLAS library [118], which is currently the fastest open-source implementation for many architectures. Also inspired by GOTOBLAS's approach is the fairly recent BLAS-LIKE LIBRARY INSTANTIATION SOFTWARE (BLIS) [73, 81, 82, 97], an open-source framework that provides optimized kernels for basic DLA operations, such as the BLAS, based on one hand-tuned micro-kernel per architecture.

In addition to open-source implementations, many hardware *vendors* maintain and distribute their own high-performance *BLAS*, e.g., INTEL'S MATH KERNEL LIBRARY (MKL) [109], APPLE'S framework ACCELERATE [105], and IBM'S ENGINEERING AND SCIENTIFIC SUBROUTINE LIBRARY (ESSL) [104].

BLAS forms the basis for DLA libraries covering more advanced operations. The earliest library built on top of first BLAS Level 1 and later Level 2 was LINPACK [38, 115], a package of solvers for linear equations and least-squares problems from the 1970s and 1980s. LINPACK together with EISPACK [47, 101], a collection of eigenvalue solvers, was superseded by the LINEAR ALGEBRA PACKAGE (*LAPACK*) [16, 111] in 1992. LAPACK has since been extended with new features and algorithms, and is still under active development. Just like BLAS, LAPACK functions as a de-facto standard interface specification for many advanced DLA operations; libraries such as OPENBLAS and MKL adopt its interface and provide tuned implementations of various routines.

For more details on BLAS and LAPACK, and their kernels and implementations used throughout this work, see Appendix B.

#### 1.3.1.2 Blocked Algorithms

LAPACK uses *blocked algorithms* for most of its dense operations. The core idea behind these algorithms is to leverage a processor's cache hierarchy by increasing the spacial and temporal locality of operands, as well as casting most of an operation's computation in terms of BLAS Level 3 kernels. As a result, complex operations can reach performance levels close to the hardware's theoretical peak.

However, for each operation, there typically exist multiple alternative blocked

algorithms, of which LAPACK offers only one, but not always the fastest. The alternative algorithms for a given operation can be derived from its mathematical formulation systematically [24] and automatically [44, 45]. Based on these principles, LIBFLAME [93, 94, 112] offers many alternative algorithms for each operation, and for several operations provides more efficient default algorithms than LAPACK. In this work we consider LIBFLAME's blocked algorithms for various operations, and aim to predict which of them is most efficient for given scenarios.

Another caveat of blocked algorithms is their block sizes, which need to be carefully tuned to maximize performance. Since this is a well-known aspect of blocked algorithms [23, 84], LAPACK encapsulates and exposes all its tuning parameters in ilaenv, a central routine that is used to configure the library at compile time; for many operations the block sizes used by LAPACK's reference implementation of ilaenv (64 for most algorithms) have been too small on recent hardware for quite some time. Although the necessity of optimizing block sizes is well understood and taken care of by implementations such as MKL, it remains non-trivial, and in fact few end-users and application-developers are aware of it. The automated model-based optimization of the block size for blocked algorithms is the second major goal of this work.

#### 1.3.1.3 Alternatives to Blocked Algorithms

An alternative to blocked algorithms is recursive algorithms, which avoid both the algorithm selection and block-size optimization. They are also known as "cache oblivious" algorithms [27, 46] since they minimize the data-movement between cache levels [53]. Recursion has been suggested for many DLA operations, such as the LU decomposition [49, 77], the Cholesky decomposition [83], triangular matrix inversion [61], two-sided linear systems [19], tall-and-skinny QR factorization [42], and Sylvester-type equation solvers [60, 120].

However, since no readily-available recursion-based library comparable to LAPACK existed, we developed the RECURSIVE LAPACK COLLECTION (ReLAPACK) [1, 121]. RELAPACK provides recursive implementations for

48 LAPACK routines, and outperforms not only the reference implementation but in many cases also optimized libraries such as OpenBLAS and MKL.

A second alternative to blocked algorithms tailored to shared-memory machines are task-based *algorithms-by-blocks*, also known as "block algorithms" or "tiled algorithms". However, these algorithms not only introduce a specialized storage scheme of matrices "by block", but also require custom task scheduling mechanisms. Implementations of such schedulers include QUARK [91] as part of PLASMA [14], DAGUE [26], SMPSs [18], and SUPERMATRIX [33].

#### 1.3.1.4 Distributed-Memory and Accelerators

Distributed-memory machines and super-computers are indispensable for large-scale DLA computations. The first noteworthy extension of the BLAS and the LAPACK to this domain was the SCALABLE LINEAR ALGEBRA PACK-AGE (SCALAPACK) [25, 122], written in FORTRAN and based on BLAS, LAPACK, and the MESSAGE PASSING INTERFACE (MPI). However, SCALAPACK is only sparingly updated (last in 2012), and, instead, the state of the art for distributed-memory DLA is ELEMENTAL [71, 103], an actively developed C++ library, based on LIBFLAME's methodology in and object-oriented and templated programming techniques.

Since accelerators such as Xeon-Phi coprocessors and graphics processors lend themselves well to compute-intensive operations, they are a natural target for DLA codes. While some classic BLAS implementations such as ATLAS, BLIS, and MKL, can be used on the x86-based Xeon Phis, separate libraries are required for graphics processors: NVIDIA's CuBLAS [99] provides high-performance BLAS kernels for Cuda-enabled graphics cards, and Clblas [98] targets OpenCl-capable devices. Furthermore, Matrix Algebra on GPU and Multicore Architectures (Magma) [78, 116] targets Blas and Lapack operations on heterogeneous machines (e.g., CPU + GPU).

## 1.3.2 Performance Measurements and Profiling

Runtime measurements of both application codes and algorithms are crucial in the investigation of performance behaviors, bottlenecks, as well as optimization and tuning in general; hence, numerous tools facilitate such measurements. Simple timers are accessible in virtually any language and environment: e.g., time in Unix, rdtsc in x86 assembly, gettimeofday() in C, omp\_get\_wtime() in OpenMP, tic and toc in MATLAB, and timeit in Python. Several more advanced tools profile executions of functions and communications in applications by tracing or sampling: e.g., GPROF [52, 106], VAMPIR [128], TAU [72, 125], SCALASCA [48, 123], and INTEL's VTUNE [110]. While such tools are invaluable in the performance analysis of application codes, their generality makes them somewhat unwieldy for our purposes of investigating DLA kernel performance. Therefore, we designed Experimental Linear Algebra Performance Studies (ELAPS) [3, 102], a framework for performance measurements and analysis of DLA routines and algorithms, further detailed in Section 2.2.

## 1.3.3 Performance Modeling and Predictions

Predicting and modeling application performance is an important aspect of high-performance computing, and the term "performance modeling" is used to describe many different techniques and approaches. This section gives a brief overview of such approaches with focus on methods for DLA algorithms.

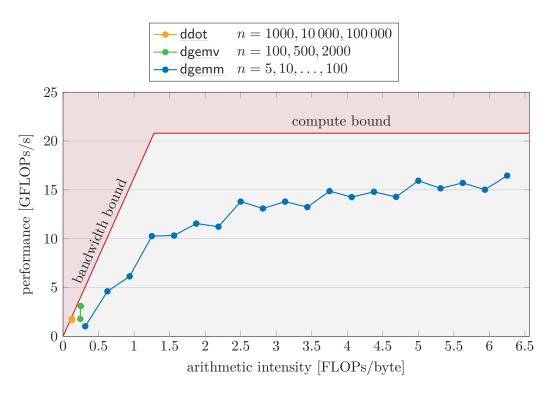

The well-established *Roofline model* [88] does not predict performance, but relates an algorithm's attained performance to the hardware's potential: As detailed in A.5.3, it allows to evaluate an execution's resource efficiency by relating its algorithm's arithmetic intensity and int performance relative to the hardware's peak main-memory bandwidth and floating-point performance. It has been applied, implemented, and extended in numerous publications, such as [59, 65, 70]. Notably, Benner et al. use the roofline model (the arithmetic intensity in particular) to optimize the block size for a blocked matrix inversion algorithm [23].

Model-based performance tuning of BLAS implementations was suggested for both ATLAS [92] and BLIS [66], showing that near-optimal BLAS performance can be reached without measurement-based auto-tuning: Instead they, e.g., select blocking sizes according to the BLAS implementation and the target processor's cache sizes. Note that these approaches are used to tune BLAS kernels, and do not actually predict their performance; hence they cannot serve as a basis for our predictions.

Previous work in our research group by Iakymchuk et al. constructed accurate analytical performance models for small DLA kernels [56, 57]. These models target problems that fit within a HARPERTOWN <u>E5450</u>'s last-level cache (L2), and are based on the number of memory-stalls and arithmetic operations as well as their overlap incurred by specific kernel implementations. As such, they require not only a deep understanding of the processor architecture, but also a detailed analysis of the kernel implementation. While the resulting models yield accurate predictions within a few percent of reference measurements, they are not easily extended to larger problems and other operations. Therefore, this work instead considers automatically generated, measurement-based models.

Alonso et al. construct piecewise runtime and energy models—somewhat similar to those presented in this work—for the BLIS implementations of dgemm and dtrsm [15] on a SANDY BRIDGE-EP E5-2620. However, their approach is based on extensive knowledge of BLIS [66], and their models only represent one degree of freedom (by considering only square matrices or operations on panel matrices with fixed width/height). Their average runtime model accuracy for dgemm and dtrsm is, respectively, 1.5% and 4.5%, with local errors of up to, respectively, 4.5% and 7%. Catalán et al. extend this work to multi-threaded dgemm, dtrsm, and dsyrk in order to predict the performance of a blocked Cholesky decomposition algorithm with fixed block size [32]; their average runtime prediction errors are 3.7% and 2.4%, depending on the parallelization within BLIS. In contrast to these publications, the modeling framework presented in this work, which was developed around the same time, is fully automated, applicable to any BLAS- or LAPACK-like routine, not

limited to one implementation and hardware, and offers models with multiple degrees of freedom.

In a separate effort Yamamoto constructs measurement-based, yet hardware-and *implementation-independent models* in the form of a series of univariate polynomials (one kernel argument is represented by the polynomial, the other varied in the series) for several BLAS Level 3 kernels [89, 90]. These models are used to predict the performance of both a blocked reduction to tridiagonal form [89] and a blocked multishift QR algorithm [90]. The resulting prediction error on an unspecified AMD OPTERON is reported to be below 10% for the single-threaded tridiagonalization, and is on average around 10% for the QR algorithm using multi-threaded BLAS. In contrast, the more general piecewise models proposed in this work yield considerable smaller prediction errors for various blocked algorithms.

Several research projects model the performance of distributed-memory applications. A general purpose approach by Calotoiu et al. builds basic performance models for kernels in application codes based on performance profiling [30, 31], allowing to investigate the complexity and scalability of application components. In the field of distributed-memory DLA, most modeling efforts target Scalar PACK using domain-specific knowledge through, e.g., polynomial fitting [67] or hierarchical modeling of kernels [36].

#### 1.3.4 Tensor Contractions

Tensor contractions are at the core of scientific computations, such as machine learning [13], general relativity [62, 64], and quantum chemistry [21, 34]. Since generally speaking such contractions are high-dimensional matrix-matrix multiplications, they are closely related to BLAS Level 3 operations, and in fact most contractions can be cast in terms of one or more calls to <u>dgemm</u>, either by adding loops or transpositions; this is implemented in many frameworks, such as the Tensor Contraction Engine (TCE) [54, 126], the Cyclops Tensor Framework (CTF) [74, 100], the MATLAB Tensor Toolbox [17, 117], and Libtensor [43, 113].

In contrast to these implementations, which rely on a single algorithm for each contraction (potentially selected through heuristics), previous work in our group by Di Napoli et al. investigated the automated generation of all alternative BLAS-based algorithms [37]. Chapter 6 picks up this work and presents a performance prediction framework for such algorithms that allow to automatically identify the fastest algorithm [6].

More recent and ongoing work in our group by Springer et al. attempts to go break the barrier between contraction algorithms and dgemm implementations. Following the structured design of BLIS [81], they propose code generators that provide high-performance algorithms tailored to specific contraction problems that reach close to optimal performance [75]. Their tools construct numerous alternative implementations, and identify the fastest through a combination of heuristics and micro-benchmarks.

# 2 Performance Effects and Measurements

This work is concerned with predicting the performance of dense linear algebra routines and algorithms through measurement-based performance models and micro-benchmarks. To fully focus on modeling and prediction in the following chapters, we here establish how accurate runtime measurements are obtained, and address common influences on such measurements and their effects. Furthermore, we present a performance measurement tool and framework tailored to dense linear algebra routines that we developed to serve as the foundation for the experiments, models, and benchmarks throughout this work.

In detail, this chapter covers the following material:

- Section 2.1 presents common effects observed when measuring the runtime of dense linear algebra routines. In particular, it addresses library initialization overhead, fluctuations (e.g., due to system noise and varying processor frequency), thread pinning, NUMA effects, and caching.

- Section 2.2 introduces the ELAPS Framework that evolved from the performance measurement tools developed for this work. ELAPS provides the SAMPLER, a low-level tool for measurements of BLAS- and LAPACK-like dense linear algebra routines, as well as a PYTHON framework with a graphical user interface and various utility functions to set up experiments and process their results.

Additionally, for readers new to performance studies, Appendix A provides an introduction into the terminology and concepts of topics such as computational workload, timings, performance, hardware limitations, and efficiency.

|           | OPENBLAS          | BLIS              | MKL               | reference          |

|-----------|-------------------|-------------------|-------------------|--------------------|

| 1st dgemm | $1.10\mathrm{ms}$ | $1.32\mathrm{ms}$ | $8.14\mathrm{ms}$ | $37.96\mathrm{ms}$ |

| 2nd dgemm | $0.90\mathrm{ms}$ | $0.95\mathrm{ms}$ | $0.86\mathrm{ms}$ | $37.93\mathrm{ms}$ |

| overhead  | $0.20\mathrm{ms}$ | $0.38\mathrm{ms}$ | $7.28\mathrm{ms}$ | $0.04\mathrm{ms}$  |

Table 2.1: BLAS library initialization overhead for two identical dgemm<sub>NN</sub>s.  $(m = n = k = 200, \text{Sandy Bridge-EP } \underline{\text{E5-2670}}, 1 \text{ thread})$

# 2.1 Performance Effects for Dense Linear Algebra Kernels

At the core of any study on performance are accurate runtime measurements. However, while in principle, timing a computation is as simple as "start timer—compute—stop timer", obtaining reliable and stable timings is not trivial. In this section, we present the most relevant effects and influences on measurements of dense linear algebra routines; in particular, we address initialization overhead (Section 2.1.1), different types of fluctuations (Section 2.1.2), thread pinning (Section 2.1.3), NUMA effects (Section 2.1.4) and caching (Section 2.1.5).

## 2.1.1 Library Initialization Overhead

Many high-performance dense linear algebra libraries, such as optimized implementations of BLAS and LAPACK, initialize (e.g., detect hardware, allocate buffers, etc.) the first time one of their kernels is invoked. These *initializations* imply an *overhead* that can significantly increase the first library invocation's runtime.

#### Example 2.1: Library initialization overhead

Table 2.1 presents the runtime of two consecutive matrix-matrix multiplications  $C_1 := A_1 \mid B_1 + C_1$  and  $C_2 := A_2 \mid B_2 + C_2$  (dgemm<sub>NN</sub>) with disjoint  $A_1$ ,  $A_2$ ,  $B_1$ ,  $B_2$ ,  $C_1$ ,  $C_2 \in \mathbb{R}^{200 \times 200}$  on a Sandy Bridge-EP E5-2670 with single-threaded OpenBLAS, BLIS, and MKL; the two calls to dgemm<sub>NN</sub> are the first and only invocations of BLAS in program.

The timings show that the libraries have substantially different overheads:

- The reference BLAS implementation has a negligible overhead but is around  $40\times$  slower than the optimized libraries.

- OPENBLAS and BLIS are optimized for the SANDY BRIDGE, and when first invoked, these libraries perform some initializations, such allocating auxiliary buffers, that introduce an overhead of, respectively, 0.20 ms and 0.38 ms.

- In addition to the allocation of auxiliary buffers, MKL dynamically detect the processor architecture to accordingly select optimized kernels.

Hence it has by far the largest overhead of 7.28 ms, which dominates its first invocation's runtime.

Since we mostly use optimized libraries such as OPENBLAS, BLIS, and MKL, we counter the initialization overhead by simply preceding any set of measurements with an unrelated kernel invocation.

#### 2.1.2 Fluctuations

Once the initialization overhead is overcome, repeated timings of the same kernel on the same data may still exhibit significant *performance fluctuations*. Such fluctuations can be caused by a variety of effects, such as background applications and system noise (Section 2.1.2.1), INTEL TURBO BOOST (Section 2.1.2.2), or other changes in processor frequency (Section 2.1.2.3).

#### 2.1.2.1 Background and System Noise

The potentially most disturbing, yet also quite easily avoidable source of fluctuations are other *background processes* competing for the processor's resources.

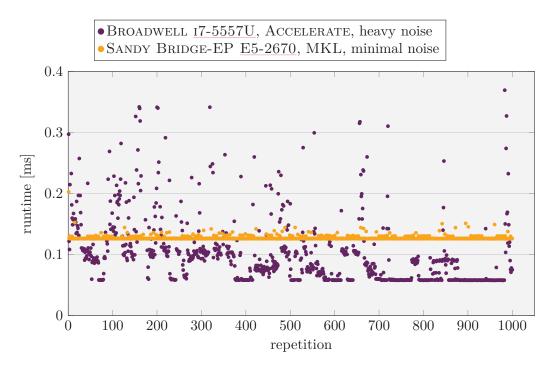

#### Example 2.2: Influence of background noise

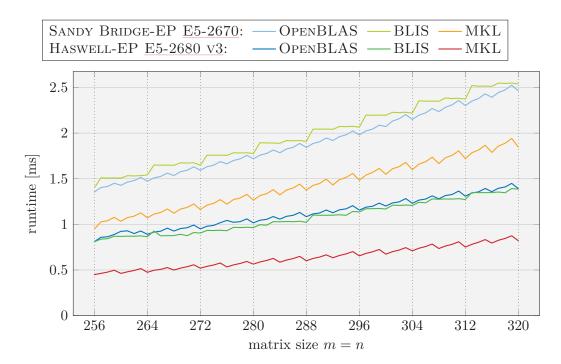

Figure 2.1 presents the runtime of 1000 repetitions of the matrix-matrix multiplication  $C := A B + C (\operatorname{dgemm_{NN}})$  with  $A, B, C \in \mathbb{R}^{100 \times 100}$  on a Broadwell 17-5557U (as part of MacBook Pro with Apple's

Figure 2.1: Runtime fluctuations  $\underline{\mathsf{dgemm}}_{\mathsf{NN}}$  caused by background processes and system noise.

(m = n = k = 100, 1 thread)

framework Accelerate and a Sandy Bridge-EP <u>E5-2670</u> (as part of RWTH's computing cluster) with MKL.

On the Broadwell I7-5557U ( $\bullet$ ) with various other applications running in the background (e.g., browser and music player), the fluctuations are enormous: The measurement standard deviation is over  $4\times$  the mean runtime. On the Sandy Bridge-EP <u>E5-2670</u> ( $\bullet$ ) with no other user applications running during measurements, the fluctuations are already much smaller at 2.36% of the average time. For larger problem sizes, the fluctuations are considerably smaller, and quickly fall below 0.1%.

While these type of fluctuations can be avoided to some extend by ensuring that no other applications run during measurements, they cannot be avoided altogether even with exclusive access to dedicated high-performance hardware—the remaining fluctuations are known as *system noise* [80]. Hence, for our

experiments, models, and micro-benchmarks all our measurements are repeated at least five times and *summary statistics* of the runtime (or performance) are presented, such as the minimum or median.

#### 2.1.2.2 Intel Turbo Boost

Compute-bound dense linear algebra computations, such as BLAS Level 3 and LAPACK-level routines, benefit directly from increased processing frequencies. Therefore, they usually trigger INTEL TURBO BOOST and constantly run at the maximum turbo frequency if possible. Since this frequency cannot be sustained indefinitely on most machines, the processor frequency is eventually lowered and henceforth fluctuates to keep the hardware within its power and thermal limits.

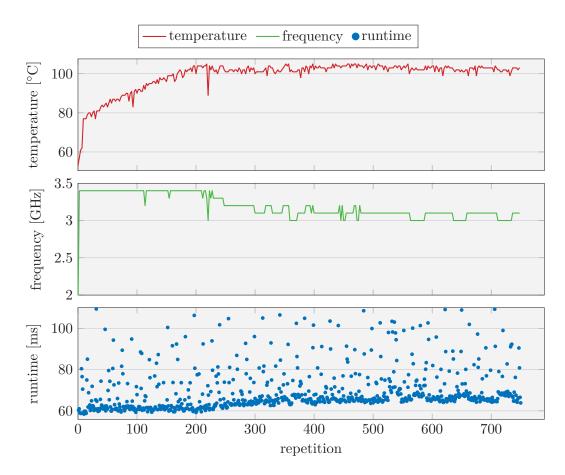

#### Example 2.3: Turbo Boost

Figure 2.2 presents the runtime of repeated matrix-matrix multiplications C := A B + C (dgemm<sub>NN</sub>) with A, B,  $C \in \mathbb{R}^{1300 \times 1300}$  alongside the processor's temperature and frequency<sup>1</sup> on both cores of a Broadwell I7-5557U with multi-threaded Accelerate; in this experiment, no other resource intensive programs run in the background.

In the beginning, the processor is at a cool 53 °C (—) and each dgemm<sub>NN</sub> takes about 60 ms (•) at the maximum turbo frequency of 3.4 GHz (—). The processor temperature increases steadily up to 105 °C around repetition 200 (12 s into the experiment); at this point the frequency is reduced and continuously adjusted between 3 GHz and 3.2 GHz such that this temperature threshold is not exceeded. This change in frequency, as well as its fluctuations towards the end have a direct effect on the dgemm<sub>NN</sub>'s runtime: It increases by about 10 % to roughly 67 ms.

The behavior of Turbo Boost depends enormously on the computation environment: While on a work-station or laptop the processor temperature increases rapidly and the maximum turbo frequency is not sustained for long, on dedicated high-performance compute clusters, efficient cooling allows for the

<sup>&</sup>lt;sup>1</sup> Obtained through the INTELPOWER GADGET.

Figure 2.2: Effect of Turbo Boost on the runtime of dgemm<sub>NN</sub>. (Note: y-axes are not 0-based.) (m = n = k = 1300, Broadwell 17-5557U, 2 threads, Accelerate)

processor to operate at the maximum turbo frequency for much longer, if not indefinitely. However, even in our main computing facilities at the RWTH IT CENTER, we observed notable fluctuations of the frequency below its maximum with negative impacts on our measurement quality and stability.

Throughout this work, we consider processors with and without enabled Turbo Boost. While the performance of these two cases is not directly comparable, we consider our methodologies for both scenarios. In particular, Turbo Boost is disabled on our Sandy Bridge-EP E5-2670 (unless

Figure 2.3: Varying runtime for a skewed dgemm<sub>NN</sub> over a period of time. (m = k = 4000, n = 200, 1 thread, OPENBLAS)

otherwise stated) and enabled on our HASWELL-EP <u>E5-2680 v3</u>—an overview of all hardware configurations is given in Appendix C.

#### 2.1.2.3 Distinct Long-Term Performance Levels

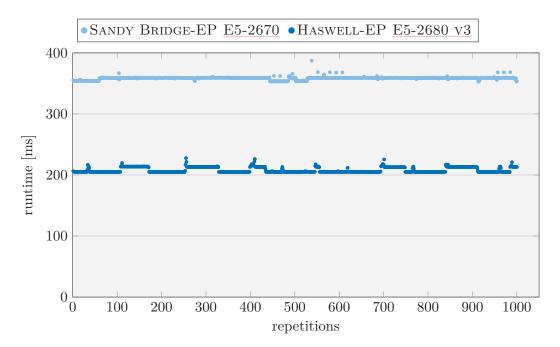

Even with Turbo Boost disabled, a processor's speed is not always fixed to its base frequency and we instead observed jumps between two or more performance levels.

## Example 2.4: Performance levels

Figure 2.3 presents the runtime of 1000 repetitions of the matrix-matrix multiplication  $C := AB + C \text{ (dgemm}_{NN)}$  with  $A \in \mathbb{R}^{4000 \times 4000}$  and  $B, C \in \mathbb{R}^{4000 \times 200}$  on a Sandy Bridge-EP <u>E5-2670</u> and a Haswell-EP <u>E5-2680 v3</u> (both with Turbo Boost disabled) with single-threaded OpenBLAS.

On both machines, we can clearly make out two distinct runtime levels:

on the Sandy Bridge, the measurements jump between  $354\,\mathrm{ms}$  and  $359\,\mathrm{ms}$ , which are  $1.4\,\%$  apart, and on the Haswell with twice the floating-point performance per cycle, the two levels at  $205\,\mathrm{ms}$  and  $213\,\mathrm{ms}$  differ by  $3.9\,\%$ . There is no discernible pattern to the jumps between these levels and the processors commonly stay at the same level for  $10\,\mathrm{s}$  or longer (50 repetitions at  $200\,\mathrm{ms}$  each).

Since we found no means to eradicate this type of fluctuations, we adopt our measurement setups to account for them: Whenever we have more than one measurement point (e.g., varying the routines or problem sizes), we not only repeat each measurement several times in isolation, but also shuffle the repetitions. As a result, the repetitions for each data point are spread across the entire experiment duration and summary statistics such as the minimum and median yield a stable runtime estimate for only one performance level.

In summary, we can avoid or account for various types of fluctuations within our measurements.

# 2.1.3 Thread Pinning

Which processor cores a program runs on is generally controlled by the operating system, and in fact most schedulers every now and then move threads between cores at runtime. However, since dense linear algebra kernels immensely rely on temporal data locality within the cache hierarchy and caches shared across multiple cores, moving or physically separating threads may significantly decrease a computation's efficiency. Counteracting these effects by restricting threads to physical cores is called *thread pinning*.

#### Example 2.5: Thread pinning

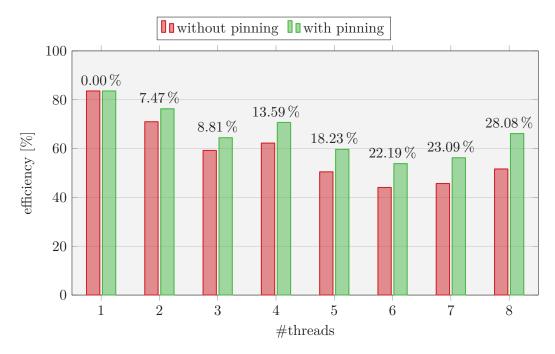

Figure 2.4 presents the compute-bound efficiency (see Appendix A.5) of the matrix-matrix multiplication  $-C := -A - B + -C - (\text{dgemm}_{\text{TN}})$  with  $A \in \mathbb{R}^{2000 \times 64}$ ,  $B \in \mathbb{R}^{2000 \times 2000}$  and  $-C \in \mathbb{R}^{64 \times 2000}$  (an example taken from within LAPACK's blocked dlauum<sub>L</sub>) using OPENBLAS with an increasing number of threads on a two-processor SANDY BRIDGE-EP <u>E5-2670</u> machine with and without thread pinning.

Figure 2.4: Effects of thread pinning on the compute-bound efficiency of a multi-threaded  $\underline{\mathsf{dgemm}}_{\mathsf{TN}}$ . Annotations: speedup of  $\boxed{\hspace{-0.1cm}}$  over  $\boxed{\hspace{-0.1cm}}$ .  $(m = 64, n = k = 2000, \mathtt{Sandy Bridge-EP} \ \mathtt{E5-2670}, \mathtt{OpenBLAS}, \mathtt{median} \ \mathtt{of} \ \mathtt{100} \ \mathtt{repetitions})$

While the single-threaded <u>dgemm\_TN</u> is not affected by pinning, with two threads, the execution pinned to two cores of one socket (11) is 7.47% faster than the unpinned version (11); this difference increases with the number of threads up to 28.08% on 8 cores.

To ensure that BLAS implementations reach their full potential, throughout this work all measurements are performed with threads pinned to the cores of a single processor.

## 2.1.4 NUMA Effects

Multi-core and especially multi-processor high-performance machines feature Non-Uniform Memory Access (NUMA) architectures: Their physical main-memory is divided into distinct NUMA domains, which are connected to individual processors or subset of cores via separate memory channels. While

| Work distribution       | Data distribution |                   |  |  |

|-------------------------|-------------------|-------------------|--|--|

|                         | 1 NUMA domain     | 2 NUMA domains    |  |  |

| 1 processor (8 cores)   | $6.59\mathrm{ms}$ | $6.91\mathrm{ms}$ |  |  |

| 2 processors (16 cores) | $5.79\mathrm{ms}$ | $3.81\mathrm{ms}$ |  |  |

Table 2.2: Effects of data distribution in a NUMA machine on the performance of dgemm<sub>NN</sub>.

(m = k = 4000, n = 8, SANDY BRIDGE-EP E5-2670, MKL, median of 1000 repetitions)

some machines have one NUMA domain per processor, others have one domain per memory controller, which are associated to groups of cores.

Each core can access every NUMA domain by routing traffic through the corresponding memory controller. However, compared to accessing a core's own NUMA domain, accessing remote domains is slower—especially when crossing processor boundaries. Furthermore, a machine's peak memory bandwidth can only be attained by using all of its memory controllers for all NUMA domains.

#### Example 2.6: NUMA effects

Table 2.2 presents the runtime of the almost<sup>2</sup> bandwidth-bound matrix-matrix multiplication  $C := A B + C (\operatorname{dgemm_{NN}})$  with  $A \in \mathbb{R}^{4000 \times 4000}$ , and  $B, C \in \mathbb{R}^{4000 \times 8}$  using MKL on a two-processor SANDY BRIDGE-EP E5-2670 machine with the data and workload both individually either limited to one processor and its single NUMA domain or spread across both. Two effects can be observed:

- Performing the  $\underline{\mathsf{dgemm}_{\mathsf{NN}}}$  on a single processor while spreading the matrices across both NUMA domains increases the runtime by 4.86 % because accesses to remote data are slightly slower.

- Computing on both processors while all matrices are stored in the first NUMA domain results in a speedup over the single-core computation of only 13.82% since all data accesses are handled by the first processor's

<sup>&</sup>lt;sup>2</sup> While this <u>dgemm<sub>NN</sub></u>'s arithmetic intensity is 1.99 FLOPs/byte, on the SANDY BRIDGE-EP <u>E5-2670</u> computations are theoretically bandwidth-bound only below 1.28 FLOPs/byte (see Appendix A.5).

|              | OPENBLAS          | BLIS              | MKL               | reference         |

|--------------|-------------------|-------------------|-------------------|-------------------|

| out-of-cache | $0.60\mathrm{ms}$ | $1.27\mathrm{ms}$ | $0.68\mathrm{ms}$ | $6.81\mathrm{ms}$ |

| in-cache     | $0.33\mathrm{ms}$ | $1.02\mathrm{ms}$ | $0.41\mathrm{ms}$ | $6.63\mathrm{ms}$ |

| overhead     | $0.27\mathrm{ms}$ | $0.25\mathrm{ms}$ | $0.27\mathrm{ms}$ | $0.18\mathrm{ms}$ |

Table 2.3: Influence of caching on the execution time of dgemv.

(m = n = 1000, SANDY BRIDGE-EP E5-2670, 1 thread, median of 100 repetitions)

memory controllers. However, when the matrices are distributed across both NUMA domains, the speedup increases to 72.96% because both computation and memory traffic are now shared between the processors.

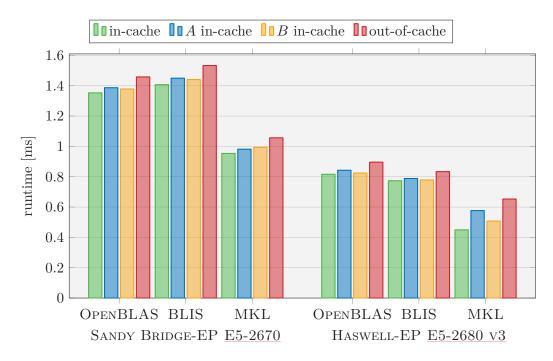

# 2.1.5 Caching

The location of operands in a computer's memory hierarchy—also referred to as the *cache precondition*—can have significant influence on a routine's performance; an operation whose operands already reside in the processor's cache (called an *in-cache* scenario or operating on "warm" data) is faster than the same operation that has to load its operands from the slow main memory (*out-of-cache*, "cold" data). This effect is strongest for bandwidth-bound operations that cannot amortize memory stalls with computations.

#### Example 2.7: Caching

Table 2.3 presents the runtime of the matrix-vector multiplication y := A x + y (dgemv<sub>N</sub>) with  $A \in \mathbb{R}^{1000 \times 1000}$  either in- or out-of-cache<sup>3</sup> and the same  $x, y \in \mathbb{R}^{1000}$  on one core of a Sandy Bridge-EP <u>E5-2670</u> with different BLAS implementations.

Even though the implementations differ by more than  $10\times$  in runtime, the overhead of loading A from main memory is comparable between 0.18 ms and 0.27 ms; for OpenBLAS, this corresponds to a runtime increase of over 80%. Furthermore, the overhead is identical for the two fastest implementations MKL and OpenBLAS, a little lower for the less optimal BLIS, and lowest for the totally unoptimized reference implementation.

The cache precondition of an operation, i.e., which of its operands are where in the memory hierarchy, largely depends on the operation's context within an algorithm or application. Chapters 5 and 6 address caching in more detail.

# **2.1.6** Summary

This section studied various effects on the performance of dense linear algebra computations. While some can be avoided altogether, others can be accounted for by specific measurement setups. In the remainder of this work, all measurements are accordingly configured to yield stable results.

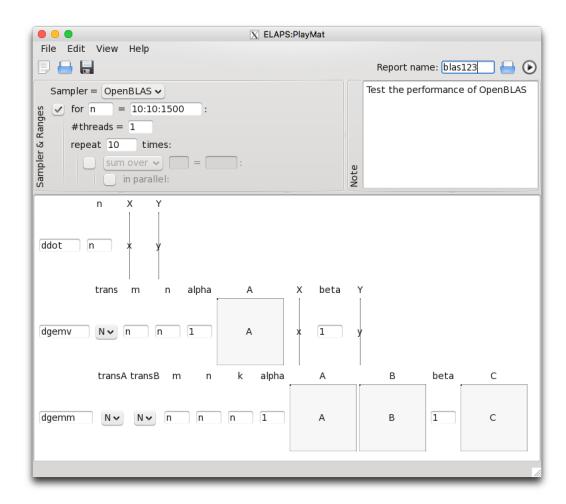

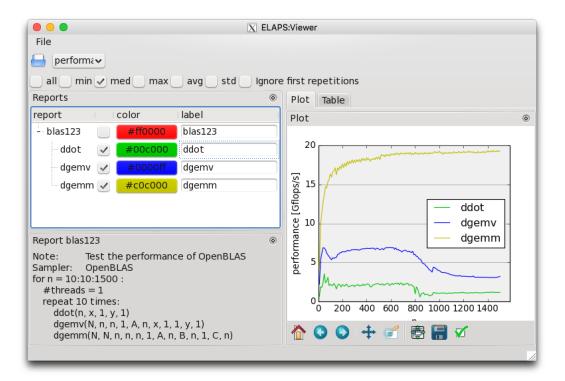

# 2.2 Measurements and Experiments: ELAPS

This section introduces Experimental Linear Algebra Performance Studies (ELAPS), the performance measurement framework that serves as the basis for all experiments, modeling procedures, and benchmarks throughout this work. ELAPS was initially developed specifically for our modeling and benchmarking applications, but has since evolved into a versatile general purpose tool-set for various dense linear algebra performance experiments. It is available as an open-source project on Github [102].

ELAPS consists of two layers: The bottom layer offers the SAMPLER, a low-level tool for runtime and performance counter measurements (Section 2.2.1); the top layer is a PYTHON framework that, among other features, offers user-friendly access to performance experiments and a graphical user interface (Section 2.2.2).

#### **Publication**

The work presented in section is in parts based on research published in:

[3] Elmar Peise and Paolo Bientinesi. The ELAPS Framework: Experimental Linear Algebra Performance Studies. Technical report. Accepter for publication

$<sup>\</sup>overline{}^3$  To place A out of cache, each repetition uses a different memory location for it.

in The International Journal of High Performance Computing Applications. AICES, RWTH Aachen University, Nov. 2016. arXiv: 1504.08035 [cs.PF].

#### 2.2.1 The Sampler

The SAMPLER is a command-line performance measurement tool written in C/C++; it essentially times arbitrary executions of dense linear algebra routines. Each SAMPLER instance typically provides access to all BLAS and LAPACK routines from one—potentially machine-specific—implementation (e.g., OPENBLAS, BLIS, or MKL), but it is easily extended to other routines with similar interfaces at compile time.

At runtime, the input to the Sampler determines which routine invocations are executed and timed. The interface provides the following work-flow:

- 1. Read from standard input a list of *calls*, i.e., routine names with corresponding lists of arguments.

- 2. Execute the specified calls, and measuring their runtime in terms of processor cycles; optionally track further performance counters through the Performance Application Programming Interface (PAPI) [28, 119].

- 3. Print the measured performance numbers to standard output.

The SAMPLER provides configuration options and commands that enable a wide range of performance studies:

- Routine operands can be individually allocated, subdivided, and initialized; this allows to create specific preconditions for calls, such as symmetric positive definite matrices and the placement of operands in the cache hierarchy.

- Any routine that follow the interface conventions of BLAS and LAPACK (see Appendix B) can be sampled.

#### 2 Performance Effects and Measurements

- Parallel regions allow to execute several routines in parallel through OPENMP. Within such regions, sequential blocks allow run parallel sequences of calls instead.

- Hardware counters (e.g., for cache misses or stalls) can be analyzed through PAPI.

We conclude this section with an example of simple performance experiments in the Sampler. A more detailed presentation of the sampler is given in [3], and a complete specification of its interface can be found in its documentation [102].

#### Example 2.8: The Sampler

We interactively start a Sampler linked with OpenBLAS on a Haswell-EP <u>E5-2680 v3</u>. To measure the runtime of the matrix-matrix multiplication C := A B + C (dgemm<sub>NN</sub>) with  $A, B, C \in \mathbb{R}^{1000 \times 1000}$ , we first allocate three double-precision operands of size  $1000 \times 1000 = 10000000$  doubles as follows:

```

dmalloc A 1000000

dmalloc B 1000000

dmalloc C 1000000

```

To also study the number of Level 3 cache misses, we enable the PAPI counter PAPI\_L3\_TCM:

```

set_counters PAPI_L3_TCM

```

Next, we pass five repeated  $\underline{dgemm_{NN}}$ -calls to the Sampler and start the measurements with the command go:

```

dgemm N N 1000 1000 1000 1 A 1000 B 1000 1 C 1000 dgemm N N 1000 1000 1000 1 A 1000 B 1000 1 C 1000 dgemm N N 1000 1000 1000 1 A 1000 B 1000 1 C 1000 dgemm N N 1000 1000 1000 1 A 1000 B 1000 1 C 1000 dgemm N N 1000 1000 1000 1 A 1000 B 1000 1 C 1000 gg

```

After roughly 340 ms, we receive the following output:

```

146867632

47155

143853672

10981

143771180

7144

143439224

6764

143589228

6542

```

Here, each line corresponds to one of the five  $\underline{\mathsf{dgemm}_{NN}}$  invocations, while the first and second entry, respectively, report the number of cycles and Level 3 cache misses. The first  $\underline{\mathsf{dgemm}_{NN}}$  causes considerable more cache misses than the following and has a slightly higher runtime.

Next, we measure y := 1.5x + y (daxpy) with  $x, y \in \mathbb{R}^{100\,000}$  using ad-hoc memory locations for the vectors:

```

daxpy 100000 1.5 [100000] 1 [100000] 1

```

We end the input stream (ctrl+D) and the SAMPLER produces the following output before terminating:

```

209740 760

157047 0

156753 0

157022 0

157088 0

```