## "Accurate Power Estimation of Deep-Submicron VLSI Circuits Considering Delay Effects and Glitches"

von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

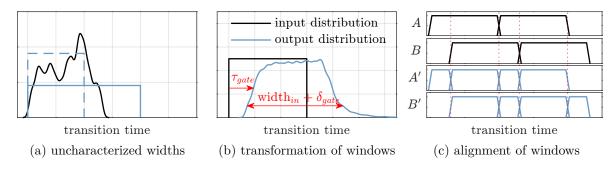

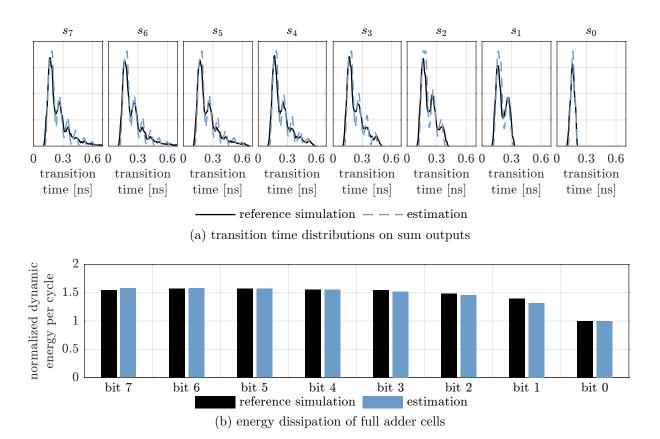

$\label{eq:Michael Meixner, Dipl.-Ing.} \mbox{aus}$   $\mbox{Krefeld}$

Berichter: Universitätsprofessor Dr.-Ing. Tobias G. Noll

Universitätsprofessor Dr. sc. techn. Renato Negra

Universitätsprofessor Dr.-Ing. Tobias Gemmeke

Tag der mündlichen Prüfung: 25. Januar 2019

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

# **Contents**

| 1 | Mot                                              | tivation                                                   |                                                                            | 3  |  |  |

|---|--------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|----|--|--|

| 2 | Intr                                             | oductio                                                    | n                                                                          | 7  |  |  |

|   | 2.1                                              | Contri                                                     | butions to CMOS power consumption                                          | 8  |  |  |

|   | 2.2                                              | Power                                                      | estimation methodologies                                                   | 11 |  |  |

|   |                                                  | 2.2.1                                                      | Macromodels on gate level                                                  | 12 |  |  |

|   |                                                  | 2.2.2                                                      | Macromodels on register-transfer level                                     | 13 |  |  |

|   |                                                  | 2.2.3                                                      | Macromodels on system level                                                | 14 |  |  |

|   | 2.3                                              | Power                                                      | estimation considering real delay effects and glitches                     | 15 |  |  |

|   | 2.4                                              | Power                                                      | consumption and variability                                                | 18 |  |  |

| 3 | Limits of Commercial Gate Level Power Estimation |                                                            |                                                                            | 21 |  |  |

|   | 3.1                                              | Errors                                                     | due to logic simulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 22 |  |  |

|   | 3.2                                              | Errors                                                     | due to energy lookup                                                       | 26 |  |  |

|   | 3.3                                              | Benchmarking of estimation accuracy                        |                                                                            |    |  |  |

|   |                                                  | 3.3.1                                                      | ISCAS85 circuits                                                           | 28 |  |  |

|   |                                                  | 3.3.2                                                      | ISCAS89 circuits                                                           | 31 |  |  |

| 4 | Pro                                              | Probabilistic macromodels considering glitch parameters 35 |                                                                            |    |  |  |

|   | 4.1                                              | Definit                                                    | tion of quantitative glitch metrics                                        | 36 |  |  |

|   | 4.2                                              | Extrac                                                     | etion of power macromodel parameters                                       | 39 |  |  |

|   | 4.3                                              | Buildi                                                     | ng of the characterization library                                         | 44 |  |  |

|   | 4.4                                              | Applie                                                     | eation example                                                             | 46 |  |  |

|   | 4.5                                              | Challe                                                     | nges of the proposed approach                                              | 50 |  |  |

|   |                                                  | 4.5.1                                                      | Size of parameter space                                                    | 50 |  |  |

|   |                                                  | 4.5.2                                                      | Averaging of glitch metrics for word-level signals                         | 51 |  |  |

|   |                                                  | 4.5.3                                                      | Correlation between glitch metrics                                         | 51 |  |  |

|   | 4.6                                              | Reduc                                                      | tion of modeling complexity                                                | 52 |  |  |

|   |                                                  | 4.6.1                                                      | Alternative glitch metrics                                                 | 53 |  |  |

|    |                 | 4.6.2   | Simplification of occurrence metrics                                      | 55 |  |

|----|-----------------|---------|---------------------------------------------------------------------------|----|--|

|    |                 | 4.6.3   | Simplification of time metrics                                            | 59 |  |

|    |                 | 4.6.4   | Demonstration of simplified macromodels                                   | 61 |  |

|    | 4.7             | Handl   | ing of variability                                                        | 64 |  |

|    | 4.8             | Comp    | arison of probability macromodel approaches                               | 65 |  |

| 5  | Eve             | nt-base | ed lookup of power waveforms                                              | 67 |  |

|    | 5.1             | Looku   | p-based estimation of output waveforms and gate power                     | 69 |  |

|    |                 | 5.1.1   | Signal characteristics of event-based power waveform lookup $\ . \ . \ .$ | 70 |  |

|    |                 | 5.1.2   | Grouping into event combinations                                          | 71 |  |

|    |                 | 5.1.3   | Library lookup of event combination effects                               | 73 |  |

|    |                 | 5.1.4   | Superposition of looked up waveforms                                      | 74 |  |

|    | 5.2             | Chara   | cterization complexity                                                    | 74 |  |

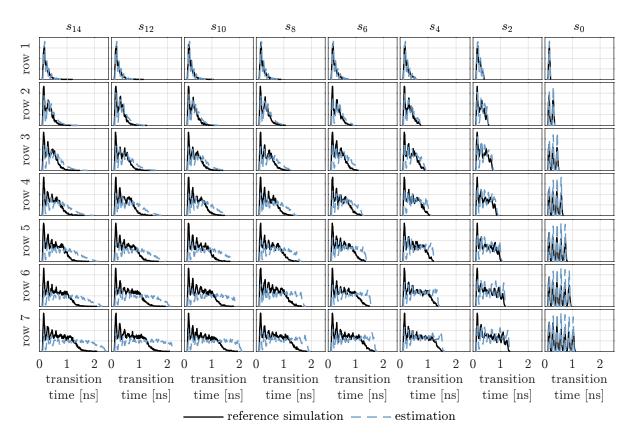

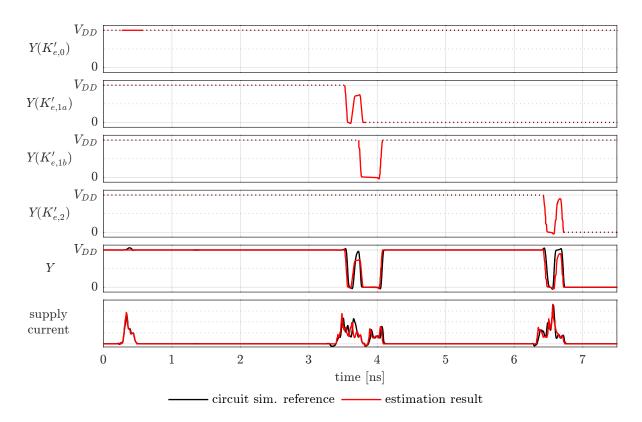

|    | 5.3             | Demo    | nstration of estimation flow                                              | 77 |  |

|    | 5.4             | Evalua  | ation of estimation accuracy                                              | 80 |  |

|    | 5.5             | Estim   | ation of sequential circuits                                              | 81 |  |

|    | 5.6             | Analy   | sis of runtime complexity                                                 | 85 |  |

| 6  | Con             | clusion |                                                                           | 87 |  |

| Bi | Bibliography 89 |         |                                                                           |    |  |

### 1 Motivation

In the early days of integrated circuits, silicon area and circuit performance were the restricting cost metrics of VLSI design. Continuing advances in CMOS technology have since lead to ever increasing transistor densities allowing for unprecedented levels of integration. The resulting challenges of power delivery and heat dissipation on the one hand as well as the rising demand for mobile computing performance on the other hand have caused the focus to shift towards power efficiency during VLSI design.

The power consumption is affected by a large number of design decisions on all levels of abstraction. Starting from architectural optimizations and operation scheduling, examples for power optimization continue down to clock or even power gating on the gate-level and device sizing on the physical level. Depending on the design method and the level of abstraction that is targeted, there are various approaches towards power estimation that allow evaluation of possible design alternatives leading to well-grounded decisions. Naturally, the more physical information of the circuit is known, the higher the confidence in the power estimation can be. At the same time, while the estimation methods allow for higher accuracy at lower levels of abstraction, the process of power estimation typically becomes more complex and therefore slower.

Due to this trade-off between estimation accuracy and complexity there is no single optimal estimation approach but rather a selection of possible methodologies suitable for a specific design stage and accuracy requirement. These might include coarse spreadsheet based power budgeting on system level during design specification on one end of the spectrum and physical level SPICE-compatible circuit simulation on the other end. Physical circuit simulation is typically the most reliable source for power estimation prior to actual measurement of fabricated silicon. It can be applied to any type of circuit without the need for pre-characterization or knowledge from previous designs since it is based on solving of differential equations governing the currents and voltages on all circuit nodes. Not surprisingly, this physical analysis results in huge sets of equations even for medium sized subcircuits. Full-chip physical simulations for current levels of integration are therefore

4 1 Motivation

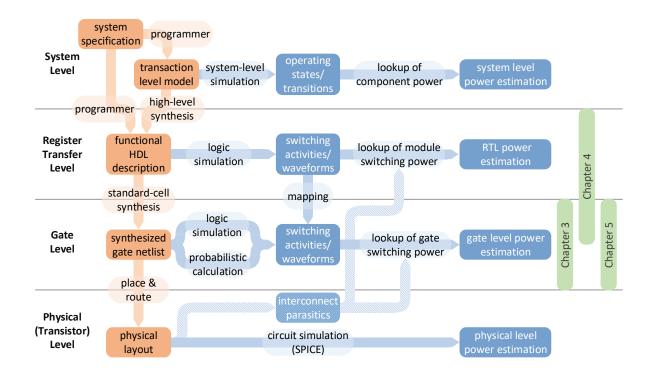

Figure 1.1: Schematic overview of power estimation methodologies on different levels of abstraction

#### unfeasible.

Due to the huge complexity of today's fabricated circuits, sign-off level power estimations are commonly performed on higher levels of abstraction particularly on the gate level where multiple established estimation flows exist. These analyses on the gate level are suitable in particular to top-down design flows employing logic synthesis tools because the precharacterized gate data is required for synthesis optimizations anyway and is distributed by standard cell developers. The power analysis on gate level abstracts from actual currents and voltages by simply considering switching events and boolean logic states. The related power consumption is derived from characterized lookup tables.

With increasing levels of integration even the derivation of meaningful switching activities for gate-level power estimation is becoming costly in terms of runtime. Consequently, a large number of power estimation methodologies on even higher levels of abstraction have been proposed. The general approach is based on encapsulation of larger logic blocks into macro-models that are characterized for suitable input parameters. On register transfer level possible model boundaries are function slices like adders or memories and parameters during power lookup might be statistical metrics of the input vectors. Even higher levels of abstraction might use models that estimate the power of a System-on-Chip by only considering the time each processing element spends in each operating state. An overview

of different approaches towards power estimation is shown in Fig. 1.

Apart from possible runtime benefits, power estimation approaches on higher level of abstraction also feature the advantage that power consumption can be estimated at early stages of design implementation even before detailed information is known about lower levels. This is possible because the pre-characterization that is commonly required for these methodologies allows for the transfer of knowledge about the power consumption from earlier designs to new circuits. While considering advantages of high level power estimation it is imperative to keep in mind that they are traded for a general loss in accuracy. The desired abstraction from numerous physical effects that allows for generalization and speedup leads to considerable discrepancies with actual power measurements.

This work aims at improving power estimation accuracy on selected levels of abstraction. The main focus is on including effects due to signal delays that were previously disregarded during power estimation but often contribute significantly to total power consumption. Despite the rising influence of leakage power, for most applications the main contribution to power consumption is still caused by the switching of circuit nodes. An accurate prediction of switching activities on all nodes therefore holds promise for high accuracy of power estimation. Unfortunately, due to different delay paths that lead to unaligned transitions on different inputs of gates, the gate outputs might feature multiple transitions in the same clock cycle. Depending on circuit topology, these spurious transitions, known as glitches, can form a significant contribution to the power consumption not least because once a glitch is created it might propagate through downstream gates. At the same time, accurately predicting the number and properties of these glitches on higher levels of abstraction is challenging, as they are strongly dependent on physical circuit properties.

Two novel methodologies for glitch-aware power estimation will be evaluated in this work. The first approach extends the classic macro-modeling approach on register transfer level or gate level by suitable glitch metrics that allow for the estimation of the effect on power consumption as well as the prediction of propagated glitch metrics on the macro outputs. The accurate propagation of glitch metrics is important in order to evaluate the power model iteratively across the circuit hierarchy. The second approach focuses on the gate level and demonstrates that more physical information needs to be included in the precharacterized lookup library in order to allow accurate power estimation considering real delay effects like glitches. Both approaches are aimed at exploiting the faster estimation runtimes of higher abstraction levels while improving accuracy compared to previous approaches by utilizing selected information from lower abstraction levels.

1 MOTIVATION

Before these proposed approaches are introduced, the terminology used throughout this work as well as previous work will be discussed in Chapter 2. Due to its prevalent usage as signoff-level reference, the accuracy that can be expected from commercial gate-level power estimation tools as well as shortcomings inherent to these estimation approaches are determined Chapter 3. Chapter 4 proposes novel glitch metrics to accurately capture glitch properties and to allow for power estimation as well as propagation of these glitch metrics by lookup of precharacterized models. An alternative approach is presented in Chapter 5 which solves inaccuracies of traditional gate level power estimation flows by substituting logic simulation with concatenation of looked-up analog waveforms and handling transition events that were previously neglected. Finally, the benefits and suitability of both propositions are evaluated in Chapter 6.

When power consumption of digital circuits is to be determined, in the majority of cases the goal is the estimation of average power consumption. One of the few exceptions is the design of the power supply network which requires consideration for the tolerable supply voltage drop and electromigration both of which are determined by the maximum instantaneous power consumption. For important power related challenges like thermal package design or battery-constrained low power operation the maximum power consumption is of little concern because it only applies to a negligible amount of operating time. For these applications the average power consumption for a typical work load or selected input stimuli needs to be determined. Because of this focus on the mean power, many approaches in the field of power estimation are of probabilistic nature in order to capture typical behavior as will become apparent in the following chapter.

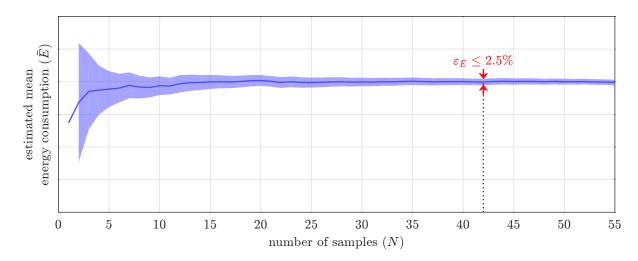

This fact is related to the problem of defining how "mean power consumption" is to be determined. Because of the strong dependence on switching activity, the characterization of a circuit macro requires the definition of typical workloads which is challenging for many applications. Changes in the operating environment often result in drastic changes in workload. On top of that, the trend of growing process variations in deep-submicron CMOS technologies also affects power consumption which will be discussed in more detail at the end of this chapter. All of these uncertainties add up to the result that a single figure for mean power consumption is only marginally valuable if no knowledge about the spread of the power consumption under expected operating conditions is available. Due to the strong dependency on workload- and variation-specific switching activity, classical corner-based characterization is not sufficient to determine this spread. Instead, detailed characterization of power consumption calls for statistical approaches like Monte-Carlo simulation and mean estimation. The requirement of analysis for differing input parameters in order to determine power variations increases the need for accelerated evaluation of power consumption. At the same time, this challenge lends itself to probabilistic approaches that are inherently capable of handling some form of variation.

Before discussing previous work related to power estimation and specifically the handling of glitch based contributions, a brief introduction to sources of power estimation of static CMOS circuits and the related terminology will be given.

#### 2.1 Contributions to CMOS power consumption

The power consumption of a CMOS circuit can be separated into a *dynamic* and a *static* component. While the dynamic power,  $P_{dyn}$ , is caused by the loading and unloading of circuit nodes during logic evaluation of the circuit, static power,  $P_{stat}$ , is mostly independent from switching as it is caused by undesired leakage currents from supply to ground nodes that are quasi constant during one logic state:

$$P = P_{dyn} + P_{stat}. (2.1)$$

The main contribution to these leakage currents in technologies below 45 nm is *sub-threshold leakage*, which results from the fact that the drain current cannot be fully turned off in real transistors. *Gate leakage* which had gained importance due to shrinking gate oxide thickness resulting in direct tunneling has been reduced again by the adoption of high-k dielectric materials in recent CMOS technologies [1]. The gradual replacement of planar transistors by multigate devices at advanced technology nodes offers the promise of decreased leakage current by regaining control over the channel [2]. While the contribution of static power can be significant, its estimation complexity is relatively low because of the sole dependency on logic states.

Dynamic power consumption on the other hand depends on the switching of logic states over time which leads to both *switching power*,  $P_{dyn,sw}$ , when charging capacitive loads and *short circuit power*,  $P_{dyn,sc}$ , during the short period when both pull-up and pull-down networks of a CMOS gate are partially conducting:

$$P_{dyn} = P_{dyn,sw} + P_{dyn,sc}, (2.2)$$

$$P_{dyn,sw} = \alpha \cdot f \cdot C_{load} \cdot V_{DD}^2, \tag{2.3}$$

$$P_{dyn,sc} = 2 \cdot \alpha \cdot f \cdot \overline{Q_{sc}} \cdot V_{DD}. \tag{2.4}$$

In this equation f specifies the clock frequency,  $\overline{Q}_{sc}$  is the average charge that is dissipated during each switching window due to short circuit paths and  $\alpha$  is the *activity* factor which can also be regarded as the probability that the capacitive load,  $C_{load}$ , is

charged in a clock cycle. This simplified view on dynamic power consumption abstracts from the effect of internal node capacitances inside the pull-up and pull-down networks that could be approximated by an average effective increment on the capacitive output load. Because both components of  $P_{dyn}$  are directly proportional to clock frequency it is often advantageous to consider the average energy dissipation per clock period  $E_{dyn}$  which eliminates this dependency:

$$E_{dyn} = \frac{P_{dyn}}{f} = \alpha \cdot C_{load} \cdot V_{DD}^2 + 2 \cdot \alpha \cdot \overline{Q_{sc}} \cdot V_{DD}. \tag{2.5}$$

The dynamic energy dissipation stays constant for varying operating frequencies as long as the same operations are performed and the maximum operating frequency that still results in full-swing transitions on all nodes is not exceeded. Because the static power consumption, in contrast, is only marginally influenced by the frequency of switching events, this also introduces an elegant way of separating both components. Assuming that the operating frequency can be manipulated during measurement or simulation, the power consumption of a circuit macro performing the same work load at two distinct frequencies  $f_1$  and  $f_2$  can be determined as

$$P_1 = E_{dum} \cdot f_1 + P_{stat}, \tag{2.6}$$

$$P_2 = E_{dyn} \cdot f_2 + P_{stat}. \tag{2.7}$$

Solving these equations for static power and dynamic energy therefore results in

$$P_{stat} = \frac{f_1 \cdot P_2 - f_2 \cdot P_1}{f_1 - f_2} \quad \text{and} \tag{2.8}$$

$$E_{dyn} = \frac{P_1 - P_2}{f_1 - f_2}. (2.9)$$

Dynamic energy dissipation strongly depends on the probability of switching at individual circuit nodes which is defined by the switching activity  $\alpha$ . This factor is generally subject to large variation because it strongly depends on the workload which is carried out by the circuit under test. A clock has an activity factor of  $\alpha = 1$  caused by deterministic rising edges in each cycle while a random signal would feature  $\alpha = 0.25$  resulting in charging of the load in every fourth clock cycle on average, which is equivalent to a toggling of the logic state in every second cycle. This consideration indicates that no logic signal carrying information could feature an activity  $\alpha > 0.5$  because even toggling of the logic state in every clock cycle would only result in  $\alpha = 0.5$ . Unfortunately, for real signals

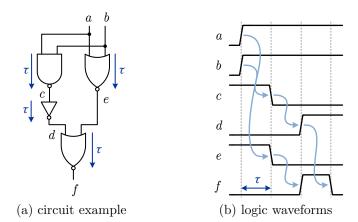

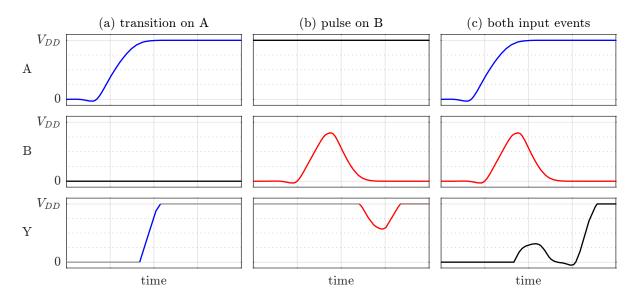

Figure 2.1: Generation of a glitch pulse due to unbalanced paths at gate inputs.

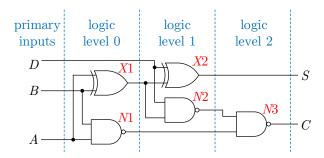

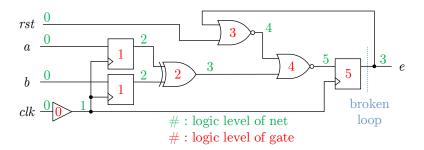

featuring transport delays this does not need to be true, because spurious transitions due to unbalanced path delays can lead to additional switching before a signal settles to its stable state. The creation of one of these spurious pulses commonly known as glitches is demonstrated in Fig. 2.1 for a simple circuit example implementing the exclusive OR function of two inputs, a and b. For simplification, all gates are assumed to feature the unit delay of  $\tau$ . When both inputs change at the same time, output f is not supposed to switch at all according to the logic function. However, due to the circuit structure in the assumed implementation, the transitions on the inputs d and e of the bottom NOR-gate are not aligned which results in a rising logic state for f before it settles to the low state again. Because of such glitches, the switching activity of a circuit node may exceed the limit of zero-delay evaluation of  $\alpha = 0.5$ .

Depending on the circuit topology, glitching can be responsible for a significant amount of the power consumption ranging from 20 - 30% for a large number of circuits but even reaching contributions of approximately 70% of the total power for selected circuits like combinatorial adders or multipliers [3, 4]. These types of circuits typically feature topologies with a large number of gates that are connected in series, which is measured as the logic depth of a circuit. Therefore, when a glitch is created in an early state of these circuit structures it can potentially influence the switching activity of a large number of gates by propagating through the circuit hierarchy. The contribution of glitching to total power consumption is therefore becoming even more significant in designs that employ a high logic depth between register stages in order to mitigate increased variability or in applications using subthreshold operation for ultra-low power consumption due to growing delay variations [5, 6].

#### 2.2 Power estimation methodologies

The development of both fast and accurate power estimation methodologies has been in the focus of research for more than 20 years to this date. While in the early days little to no CAD tool support was available for power estimation [7], suitable estimation tools on different levels of design abstraction have long since been published by all leading electronic design automation companies. As already stated in the motivation, there is no single optimal power estimation approach. Instead, the suitable method needs to be selected regarding the design style and required accuracy.

The most accurate way to evaluate power consumption of digital circuits prior to fabrication remains physical SPICE-compatible circuit simulation at transistor level. The need for accelerated power estimation arises due to the complexity linked to solving the systems of differential equations that are a fundamental part of physical simulation. Over the years, computing power has increased exponentially and numerous fast-SPICE simulators have been developed. They rely on techniques like parasitic reduction, partitioning, isomorphic matching, piecewise linearization or parallelization to deliver results that are hardly distinguishable from full SPICE accuracy for many applications despite dramatically reduced runtimes [8]. However, at the same time circuit sizes have likewise grown, following the trend for higher levels of integration, so the challenges of power estimation remain similar.

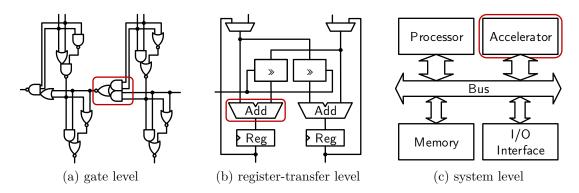

The basic principle behind virtually all accelerated power estimation approaches is to employ knowledge about the power consumption of existing circuit components to estimate the power of a yet to be realized implementation that is build from the same or similar components. A potentially costly precharacterization step is required to extract this knowledge and generate the component macromodels. However, once this power consumption data has been collected, all subsequent power estimations can profit from accelerated runtimes since evaluation of these macromodels is often as simple as a series of table lookups. In order to obtain the required accuracy, power models are usually parameterized which results in an estimation flow that is typically separated into two steps. During the first step the parameter values that apply in the analyzed implementation are determined. These values are employed in the second step to look up the power consumption for all macromodels. The granularity of the models and the relevant evaluation parameters vary in a wide range depending on the targeted abstraction level. Possible boundaries for these models on different levels of abstraction are exemplified in Fig. 2.2.

Figure 2.2: Examples for boundaries of macromodels on different levels of abstraction.

#### 2.2.1 Macromodels on gate level

Gate-level power models were the earliest approaches to accelerate power estimation. Traditionally, dynamic switching power,  $P_{dyn,sw}$ , according to (2.3) was considered the dominating contribution so the power model was essentially reduced to a switched capacitance and the goal of power estimation was an accurate estimation of the switching activity on all nodes of a gate level circuit. This could be achieved by performing logic simulation while monitoring signal states [7]. Modified simulators improved the handling of finite signal slopes [9, 10, 11, 12] as well as considering additional power contributions like short circuit power and internal gate capacitances [13]. These effects are particularly relevant for gates of higher complexity where internal power consumption can be the dominating contribution compared to charging of the output node. All of these effects can be easily captured by characterizing the power consumption related to all combinations of transitions from one set of input states to another [14]. For an N-input gate, this requires characterization of  $2^{2N}$  transitions to be stored in a lookup table. This complexity is further increased when the effect of varying output loads and transition slopes is considered [15]. Established commercial gate-level power estimation flows used during sign-off level power estimation are still based on this characterization of transitions but are limited to events featuring the toggling of only one input in order to balance accuracy and complexity [16].

Irrespective of the specific modeling approach, the input parameters for gate-level models always include switching activity on all circuit nodes of the gate-level netlist. When logic simulations are used to determine these switching events and average power consumption is to be estimated, sequences of input vectors featuring the desired statistics need to be applied until convergence can be observed [17]. This potentially time-consuming step can be replaced by probabilistic propagation of signal statistics. Starting from signal

statistics on the circuit inputs like probabilities for signals to be in high state and probabilities for signals to switch during a specified time interval, the resulting probabilities at the remaining circuit nodes can be analytically determined in one sweep over the circuit hierarchy [18, 19]. Improvements to this propagation of signal statistics added support for handling of temporal [20, 21] and spatial correlation [22, 23] between signals.

#### 2.2.2 Macromodels on register-transfer level

By encapsulating larger circuit blocks in macromodels, low level effects like capacitive coupling or internal timing hazards can be abstracted. Functional blocks like adders, shifters or register slices are natural boundaries for power macromodels on this abstraction level. The choice of model parameters that promise the highest accuracy are the individual states of all macro inputs before and after a switching event. Unfortunately, for typical macroblocks on register-transfer level the exponential dependency of characterization complexity on the number of input signals renders this approach infeasible. Efforts have been made to reduce the size of this characterization table by clustering of selected states assuming relatedness of neighboring inputs [24] or analyzing similarities in switching of selected internal nodes [25]. Another approach that is based on switching of individual inputs (and potentially outputs) without full characterization builds the regression model in the form of

Power

$$(k) = c_0 + c_1 \cdot (i_1(k-1) \oplus i_1(k)) + c_2 \cdot (i_2(k-1) \oplus i_2(k)) + \dots,$$

(2.10)

where  $i_j(k)$  is the logic state of input j at time k and " $\oplus$ " is the exclusive-or operation indicating a change of the logic state per input [26, 27]. The coefficients  $c_j$  can be obtained by linear regression analysis from the characterized power consumption of a representative number of switching cycles applying random input vectors. A number of refinements to this approach were proposed to automatically determine special inputs [28] or conditions [29] which select between fundamentally different operating states in order to build separate regression models for each state. Correlations between switching of multiple inputs can be captured by expanding of the regression model to include terms indicating pair- or group-wise simultaneous switching [30]. This promises a significant gain in accuracy but causes the number of regression coefficients to increase exponentially. A reduction in the number of parameters can be achieved by employing signal statistics that are averaged over selected inputs. Typical statistical parameters are the

average probability of all inputs to be in high logic state and the averaged probability for switching on inputs or outputs in a specified time interval [31, 32, 33]. Due to the reduced number of parameters, a full characterization of selected input vector streams featuring all desired statistics can be performed, which allows for direct table lookup possibly involving interpolation during estimation. Additional dimensions can be added to the lookup table to consider supplementary statistics like correlation between bits [34]. Due to the averaging of switching statistics over all input bits, information on differing behavior of individual bits is discarded, which might degrade estimation accuracy. The observation that input vectors in arithmetic circuits often show strongly correlated behavior for the most-significant bits and quasirandom switching for the lowest bits motivated an approach that builds separate models for lower and upper bit weights of word-level models [35]. The boundary between both bit types can be calculated from word-level statistics like mean, variance and autocorrelation of the input vectors [36]. Alternatively, these characteristics can directly be used as model parameters for components featuring inputs that have associated word-level values [37].

Evaluation of these models can be accelerated by employing simulations on the functional level instead of relying on gate-level simulators or probabilistic propagation. Selected high-level metrics can even be propagated throughout the circuit hierarchy by building of additional lookup tables [38, 37].

#### 2.2.3 Macromodels on system level

On system level a model boundary might enclose whole submodules that are simulated using transaction level modeling. Due to the limited visibility of internal functionality, especially when components are implemented as black-boxes, possible input parameters during estimation are the time spent in coarse functional states (e.g. idle/active) [39, 40, 41] or the number of accesses on the outside ports [42, 43, 44]. Without knowledge of the implementation, power consumption in different power states can be characterized by measurement or from datasheets. During estimation, a transaction-level simulation that determines the state of the system component by monitoring its inputs and outputs can be performed which allows for accumulation of power consumption. When more detailed information on a module is available, the state of selected internal registers or signals indicating a specific event can be included in the parameter space [45, 46]. Particularly for processor cores, a multitude of specialized power models were proposed. They rely on additional parameters like instruction traces [47, 48, 49], cache hits/misses [50, 51] or

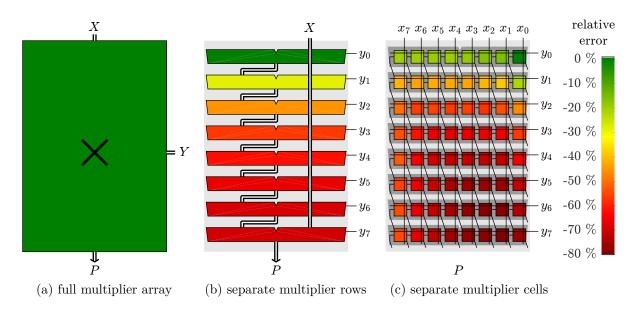

Figure 2.3: Error of zero-delay characterization of dynamic energy dissipation due to glitches inside an 8x8 array multiplier for different choices of component boundaries.

pipeline hazards [52].

# 2.3 Power estimation considering real delay effects and glitches

The correct handling of glitches during power estimation is challenging because glitching is highly dependent on accurate gate delays [53] which are in turn defined by physical parameters like parasitic capacitances or cross-coupling. The power consumption caused by glitches that are generated inside of a macromodel is automatically captured during characterization. Power consumption due to propagation of glitches which appear on the inputs of the circuit macro on the other hand needs to be estimated accordingly. Following this reasoning, it would be advantageous with respect to errors due to glitching to choose the boundaries of macromodels as large as possible, preferable as large as full pipeline states to guarantee glitch-free inputs. However, macros of this size might not be generic enough to be reusable in a large number of power estimations. On top of that, model parameters that still result in feasible characterization effort become increasingly inaccurate with growing macro size as discussed in the previous section.

Consequently, if glitch-free operation cannot be guaranteed, macromodels need to consider occurrence of glitches on the macro inputs. This need to address glitching on model

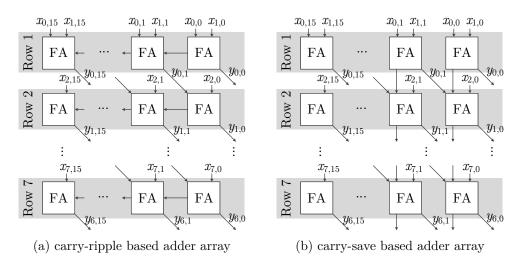

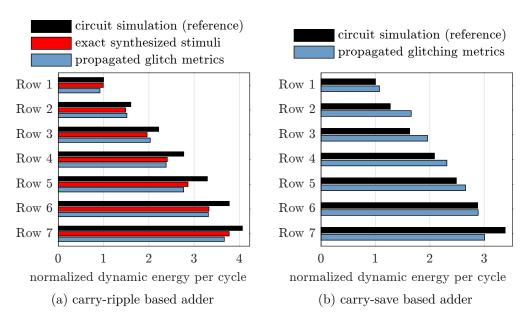

inputs is demonstrated in Fig. 2.3 for different choices of model boundaries when regarding an 8x8 array multiplier macro based on carry-ripple adders where the inputs, X and Y, are assumed to be glitch-free. This example was specifically chosen due to the high degree of glitching inside the regular array structure. Nevertheless, characterization of the whole multiplier array using glitch-free stimuli for both inputs results in perfect power estimation because the glitches that appear inside the macro are inherently captured during the low-level characterization simulation. In contrast, when all constituting adder rows inside the multiplier macro are stimulated separately using the same zero-delay stimuli that would result from the original input vectors, a growing error of the dynamic energy dissipation can be observed starting at the second adder row. When glitches that appear at the output of the first adder row are neglected while determining the switching activity at the inputs of the second row, the dynamic energy dissipation of the second row is underestimated by 28 %. The error in following adder rows is even larger because a certain number of glitches at the input of each row propagates to the output resulting in an additional increase in switching. Because of the dominating contribution of glitching to the overall power consumption for the analyzed multiplier macro, the total dynamic energy is underestimated by 57% compared to the simulation of the full macro. While this error seems excessive, at least the effect of glitches that are generated inside the carry paths of the adder rows is captured when characterizing functional slices like adders. When the model granularity is increased further down to the gate-level not even these glitches are observed when employing zero-delay switching activity. This results in an overall error of 64% for the estimation of dynamic energy.

Early gate-level estimation approaches that recognized the importance of glitching for power estimation focused on the use of accurate gate delays during simulative evaluation of switching activities in order to capture the increase in state toggling [7]. Limited output slew of circuit components in combination with nonuniform gate delays lead to attenuation of glitch pulses that are shorter in time than a gate-dependent threshold during propagation through the circuit hierarchy. To consider this glitch filtering characteristic of circuit gates, postprocessing of logic simulator results [12, 10] or custom event based simulators considering the finite signal transition times [9, 11, 15] were proposed. The thresholds for propagated pulse widths or load dependent transition times as well as power consumption due to partial-swing glitch pulses need to be determined by characterization or estimated from technology features. If probabilistic analysis is employed to analyze switching activities instead of logic simulation, similar considerations lead to concepts like

probability waveforms that consider gate delays during propagation of switching probabilities and consequently allow for filtering of non propagating glitch pulses [22, 6, 54, 23]. Alternatively, empirical correction factors that are calculated from topology properties or input vector characteristics have been proposed which are used as weighting factors during calculation of power consumption for individual gates [55, 56]. All of the above approaches solely focus on the correct analysis of switching activities which only form the input parameters to the required model lookup translating the switching events into power consumption. Due to the prevailing digital viewpoint, filtering of pulses is limited to a binary decision of propagating or blocking. When they are considered at all, partial-swing transitions are only determined in a postprocessing step to derive scaling factors to the power consumption of the related full-swing transitions.

By increasing the abstraction of macromodels to register-transfer level, the inherent consideration of glitches internal to the model boundary might appear to lessen the need for accurate handling of glitches. However, pure functional simulation which is commonly employed at this level of abstraction to accelerate model evaluation offers no possibility for propagation of glitches because only cycle-accurate timing can be observed. Instead, handling and propagation of metrics determining the glitching activity on input signals to the macromodel must be performed by means of additional lookup tables. The metric chosen by Raghunathan et al. [37], denoted glitching activity, defines the rate of glitch pulses appearing on the inputs of circuit components without specifying their shape or the time of their appearance. Liu and Papaefthymiou introduce an additional parameter which specifies both the pulse width of each glitch as well as the spacing between glitch pulses in case of multiple glitches [57]. However, partial swing glitches are not considered in their model and all glitches are assumed to occur synchronously at the beginning of each clock cycle.

Accurate estimation of power consumption due to glitching is clearly more challenging than estimation of functional switching power. On top of zero-delay functional simulations, interrelated delay effects which are defined by the physical level of the design need to be taken into account. To determine the state of the art concerning power estimation intended to capture glitching power, chapter 3 will evaluate established gate-level power estimation approaches. The insights gained regarding potential shortcomings related to these methodologies will serve as a motivation for novel estimation techniques proposed in subsequent chapters.

#### 2.4 Power consumption and variability

Because of the direct dependency of the threshold voltage on leakage currents, static power consumption is strongly affected by process and temperature variations. Dynamic power consumption due to functional circuit evaluation is less susceptible to process variations or changes in temperature when the dominating contribution can be assumed to be the charging of capacitances. However, when glitches are considered, the influence of variability on dynamic power consumption becomes less predictable. This is due to the fact that the generation and propagation of glitches is determined by the delays of individual circuit components which in term might vary considerably due to local or global variation.

With the notable exception of the introduction of multigate structures, the continuing technology scaling is accompanied by increasing variability. Therefore, this influence of process variations on dynamic power consumption forms a considerable challenge for suitable estimation methodologies.

An early method for calculating coarse bounds of the dynamic energy dissipation when variation cannot be neglected calculates ambiguity intervals at the outputs of gates based on minimum and maximum delays of all gates during which the logic state might vary depending on delay variations [58]. The lower bound of the dynamic energy dissipation is derived from a gate level estimator supplied with switching activities under the assumption that there is at most one transition during each ambiguity interval. In contrast, for the estimation of the upper energy bound the maximum number of full-swing transitions which fits inside the ambiguity interval when spaced by at least the gate delay is assumed. This simplistic method assumes uniformly distributed gate delays and allows no conclusions regarding the expected distribution of dynamic energy inside the derived bounds. Higher accuracy for the estimation of switching activity variations can be achieved by extending the concept of probabilistic transition waveforms that list possible events on circuit nodes with a given probability. Each event is not only annotated by its (mean) occurrence time but also by the standard deviation assuming normally distributed gate delays [54]. The delay and energy dissipation of gates including variation is derived from a precharacterization employing Monte-Carlo simulations. The effect of spatial correlation of parameters related to dynamic power consumption can be considered in order to improve estimation accuracy [23]. In order to limit the estimation complexity, no information about switching direction or intersignal correlation is considered for this approach. A fundamentally different approach proposes to employ Monte-Carlo Analyses based on fast

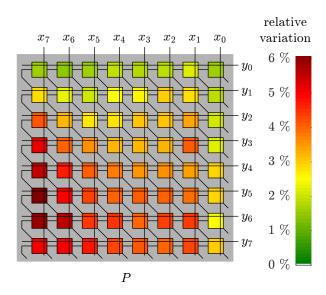

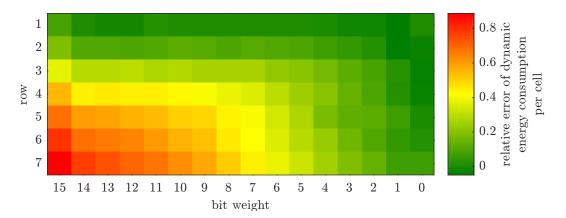

Figure 2.4: Variation of energy dissipation per cell measured as  $1\sigma$  quantile bounds relative to mean energy dissipation per cell for an  $8 \times 8$  unsigned array multiplier.

gate-level simulation by annotating precharacterized lookup tables for delays, slopes and switching energies as well as their sensitivities regarding selected variation parameters to the descriptions of basic cells [15]. During elaboration phase all instances of each basic cell are assigned an updated set of lookup tables according to the random variation parameters. Partial-swing glitch pulses are considered in a postprocessing step by deriving pulse heights from the assumed linear signal slopes.

The effect of delay variation on energy dissipation is demonstrated by a Monte-Carlo analysis of an array multiplier which exhibits both a high logic depth and a large number of reconverging delay paths. For 1000 circuit simulations both global and local variation parameters are varied for the same stream of input operands. The variation per multiplier cell is illustrated in Fig. 2.4 by comparing the relative deviation of the lower or upper  $1\sigma$  quantile bounds from the mean dynamic energy dissipation per cell. This variation metric specifies the minimum deviation interval around the mean which contains 68.3% of energy dissipation results. The dependency of the observed variation on delay variations becomes apparent in the increasing relative variation of the energy dissipation towards the lower left corner of the array. This effect can be explained by the growing number of possible delay paths terminating at these multiplier cells. In contrast, static effects like varying load capacitances or short circuit currents during switching affect all multiplier cells in the same way. Due to averaging across the multiplier array the  $1\sigma$  bound of the total dynamic energy dissipation deviates from the nominal dynamic energy by only 3%. The maximum total dynamic energy dissipation for the full array recorded during

Monte-Carlo analysis is 7.3% higher than the analysis result employing nominal models.

This result which was obtained without consideration for varying operating voltage and temperature demonstrates the impact of variations of the propagation delays on dynamic energy dissipation. The effect is exacerbated by applications which adopt subthreshold operation in order to increase energy efficiency because of increased delay variations at these operating points. As a consequence, in addition to the discussion of the accuracy at the nominal operating point the following discussion of power estimation methodologies needs to evaluate the ability of each approach to consider and report variation effects.

However, the largest variations in dynamic energy dissipation are caused by the choice of input stimuli that are applied to the circuit under test. The input stimuli for the demonstration of variation effects were sampled from uncorrelated uniform distributions spanning the full wordlength of eight bit. This results in independent toggling of each input bit in every second cycle on average. This assumption might be far from the workload that could actually be observed during functional operation of a certain multiplier macro. Moderate modifications of the input statistics can result in significant deviations in energy dissipation. For example, the reduction of the switching activity for input Y by a factor of two decreases dynamic energy dissipation of the multiplier macro by 10%. In many applications it is hardly possible to specify a single stream of input stimuli that captures typical circuit behaviour. In that case, the stimuli-dependend variation of energy dissipation should be considered in order to derive well-grounded design decisions.

# 3 Limits of Commercial Gate Level Power Estimation

Due to ever increasing levels of integration physical circuit simulation has long since ceased to be able to support full-chip power estimations. As an alternative, gate level estimation flows that fit well into top-down design methodologies employing standard cell synthesis have been developed. A number of commercial tools from established vendors in the field of electronic design automation on this level of abstraction have reached a reputation for accuracy that allows their usage as sign-off level estimators. In fact, many proposals for power estimation methodologies on higher levels employ these gate-level estimations as a reference to compare against [49, 59, 60]. Because of their importance in digital circuit design in combination with the lack of comparative studies targeting the accuracy to expect, the following discussion will focus on the work flow of commercial gate-level power estimation tools and possible sources of errors related to them. This in turn will help to identify the requirements for improved power estimation approaches that will be proposed in subsequent chapters.

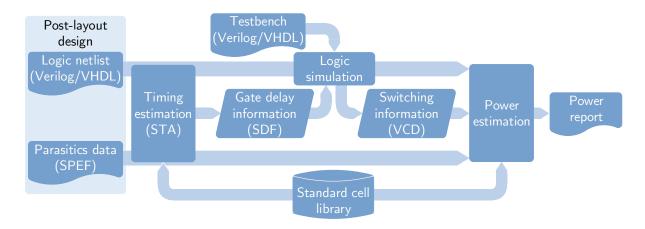

Gate-level power estimation as performed by commercial state-of-the-art tools typically operates by accumulating precharacterized energy values associated with single-signal switching on individual gate inputs. As discussed previously, the information on signal switching on all gate inputs that is required for this approach can either be determined by probabilistic propagation of switching activities throughout the circuit or by logic simulation using the gate-level netlist and a testbench supplying suitable input stimuli. In order to be able to consider delay effects like glitches on the input of gates, the evaluation of switching activity needs to take realistic gate delays into account. These gate delays, that are strongly dependent on the output loads of the individual gates, can for example be estimated by static timing analysis (STA) and annotated to the gate-level netlist during logic simulation or analytical propagation of switching probabilities. This standard work flow for gate-level power estimation is shown in Fig. 3.1.

Figure 3.1: Standard gate-level power estimation flow.

The depicted situation is that of postlayout power estimation where information from the physical level can be annotated to the gate-level view in the form of parasitic capacitances of interconnects. While gate-level estimation can also be performed at prelayout design stages, the accuracy of power consumption estimations will deteriorate accordingly.

While the standard use model of commercial gate-level power estimators is focused on classic corner-based design, the effect of process variation could be incorporated by a large number of repeated evaluations of the power consumption for varying gate delays. The required information on delay variation could for example be determined by statistical static timing analysis (SSTA). However, since the focus of the chapter is the evaluation of the overall accuracy of state-of-the-art power estimators for specific operating conditions and workloads, the effect of variation is not considered in the following discussion. The potential sources of error which will be discussed remain the same for repeated evaluation of the work flow.

Deviations of the estimated power consumption compared to physical-level power simulations might be introduced by any of the steps involved in gate-level power estimation as depicted in Fig. 3.1 [4]. The following sections will discuss selected steps in the work flow in order to highlight shortcomings and evaluate their impact on accuracy of gate-level power estimation.

#### 3.1 Errors due to logic simulation

Power estimation on gate-level requires accurate knowledge of the switching activity on all circuit nodes. The most common method of determining this switching activity on all circuit nodes is to perform a logic simulation of the design under test using either the

Figure 3.2: Example of glitch propagation and related switching power

gate-level netlists themselves or the RTL sources followed by a mapping step. Simulation on register-transfer level features the advantage of significant speedup compared to the gate-level but introduces additional errors because accurate timing properties of the gate-level implementation cannot be considered. In order to reduce the possible error sources, the following discussion will therefore focus on the gate-level instead. As an alternative to logic simulation, probabilistic methods for the calculation of switching activity like tagged probability waveforms [6] or transition waveforms [54, 23] could be used. These probabilistic propagation approaches suffer from similar problems as logic simulation when handling glitches but introduce additional sources of error due to the challenge of handling signal correlation due to reconvergent fanout during propagation of signal statistics.

The main contribution to errors during logic simulation is the handling of gate delays which lead to glitches on the circuit nodes. In order to be able to observe glitches, it is necessary to annotate accurate gate delays to the gate-level netlist during simulation. The gate delays, that are themselves dependent on the transition slopes on the gate inputs and the capacitive load at the gate outputs, can be estimated using the static timing analysis functionality that is typically provided by complementary tools to the gate-level power estimators.

A limitation that is inherent to logic simulation is the restriction to two signal levels (true and false) and the abstraction from finite signal transition slopes. In contrast, glitches occurring during actual operation of the circuit do not necessarily feature full-swing transitions due to limited signal slopes that cause the output to be discharged

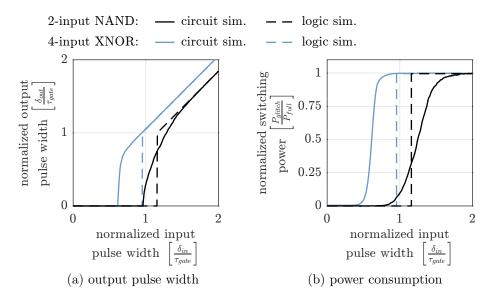

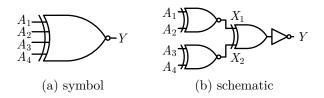

Figure 3.3: Multistage 4-input XNOR gate from a commercial standard-cell library

before it has been fully charged. The second physical effect that is hard to model in logic simulation is the impact of a glitch on the input of a gate on the output of that gate. In logic simulators this effect that is known as *glitch filtering* is commonly implemented by using inertial gate delays. The effect of this filtering is to prevent pulses that are shorter than the gate delay from propagating to the gate output. This is a simplification since the physical effect of a short pulse at the input is often visible as a partial swing pulse at the output. Fig. 3.2a shows the relationship between the input and output pulse widths for a simple NAND gate and a more complex multi-stage XNOR gate. As opposed to logic simulation with glitch filtering, circuit simulation does not feature and abrupt cut-off of the propagation for short input pulses but shows a smooth transition instead. Fig. 3.2b demonstrates that pulses that do not feature full swing transitions nevertheless cause significant power consumption. Inertial glitch filtering as employed in logic simulators would overestimate power consumption resulting from small glitches applied to the NAND gate while it would potentially lead to underestimation of the XNOR gate by rejecting a large number of valid glitches. This is a typical result which demonstrates that the gate delay is not a good measure for glitch filtering.

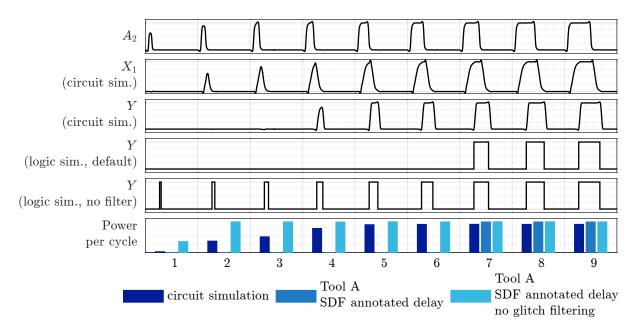

The inertial glitch filtering fails completely for complex multistage gates like full-adders or gates like the 4-input XNOR gate shown in Fig. 3.3. The delay of these gates that is looked up from the design libraries depends on the sum of stage delays. In contrast, for correct application of the pulse filtering using the inertial gate delay model the delay of the slowest stage would be significant. Since no information about the internal structure of the basic cells is known to the gate-level power estimation flow, the default glitch filtering tends to be too aggressive for complex multistage gates. This effect is demonstrated in Fig. 3.4 showing waveforms from physical circuit simulation and logic simulation alongside cycle accurate power estimations for a compound 4-input XNOR gate that features pulses of increasing width on a single input. In circuit simulation, the pulse in the second cycle can already be observed on the internal node  $X_1$  and the pulse of the fourth cycle propagates to the output demonstrating the multistage nature of this gate. In contrast,

Figure 3.4: Glitch filtering and estimated glitch energy for pulses on a single input of a 4-input XNOR gate  $(A_1 = 1, A_3 = A_4 = 0)$

logic simulation erroneously rejects all pulses until the seventh cycle when the default pulse filtering depending on the inertial gate delay model is employed.

Logic simulation without glitch filtering on the other hand results in gross overestimation of switching power as demonstrated in Fig. 3.4 despite efforts of power estimation tools to recognize glitches in the logic waveforms and apply a scaling factor to the power consumption of related events. The threshold for glitch detection is typically derived from the transition times,  $t_{rise}$  and  $t_{fall}$ , at the gate output as a pulse width

$$t_{pulse} < \frac{t_{rise} + t_{fall}}{2}. (3.1)$$

Once a glitch has been detected the power associated with the pair of constituting transitions,  $P_{trans}$ , is reduced by a factor to approximate the power consumption of a partial-swing pulse as

$$P_{glitch} = \left(\frac{2 \cdot t_{pulse}}{t_{rise} + t_{fall}}\right)^2 \cdot P_{trans}.$$

(3.2)

This approximation clearly fails for the considered XNOR gate where the short transition times of the output stage are only marginally related to the minimum propagating pulse width. Consequently, the scaling factor is only applied to the power related to the erroneously predicted glitch in the first cycle of Fig. 3.4 during the logic simulation without glitch filtering. All subsequent pulses are not recognized as glitches and are therefore estimated as separate transitions.

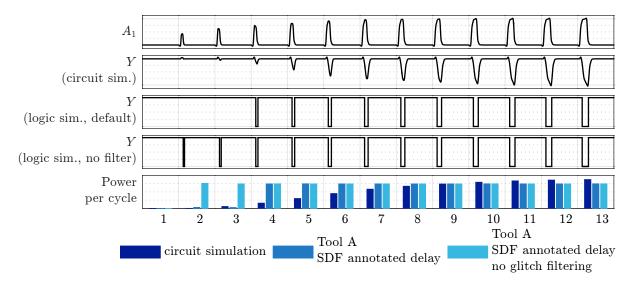

Figure 3.5: Glitch filtering and estimated glitch energy for pulses on a single input of a 2-input NAND gate  $(A_2 = 1)$

While for complex gates the default glitch filtering routinely rejects valid pulses which leads to an underestimation of switching power, the opposite can be true for simple gates with gate delays that may well be shorter than the transition time of the output. This is demonstrated in Fig. 3.5 for a 2-input NAND gate featuring pulses of increasing width on one input. Inertial gate delay filtering predicts the third pulse to propagate to the output while in physical circuit simulation the first output pulse to show 90% output swing is in cycle nine. Due to the steep transition slopes of the output, no pulses are recognized as glitches during power estimation preventing any possibility of correction of this overestimation.

#### 3.2 Errors due to energy lookup

Apart from the errors caused by inaccurate switching activities that serve as inputs to the gate-level power estimation tools, there are shortcomings which are directly dependent on the estimation methodology itself. While in general it is hard to separate the contributions to the total error observed during power estimation, during an analysis of benchmark circuits from the ISCAS85 suite the power estimation tools were supplied with switching activities that were extracted from outputs of low-level circuit simulations [4]. The power estimation using these "perfect" switching activities still showed deviations of up to 16% from circuit simulation references.

These errors are mainly caused by simplifications in the format of the characterized cell libraries that were introduced to reduce the characterization complexity and the size of the

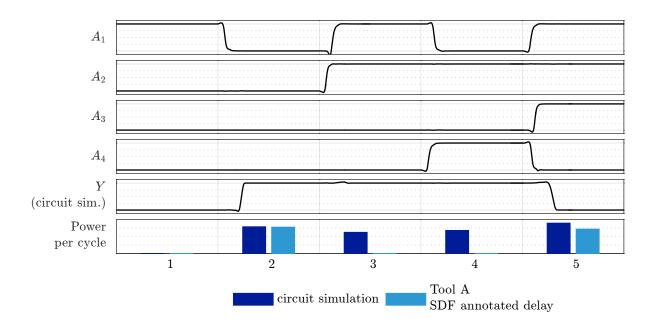

Figure 3.6: Estimated power for switching of multiple inputs of a 4-input XNOR gate

library itself. Apart from the restriction to full-swing transitions, the most fundamental simplification is the omission of multiple-input events from the library [61]. Because of this, the cell library used during lookup only contains power values related to the toggling of a single input. Power consumption related to the simultaneous or quasisimultaneous switching of multiple inputs can only be approximated. The situation is even more severe for gates where switching of the individual inputs always results in switching of the output while quasisimultaneous switching of multiple inputs does not cause the output state to change. The 4-input XNOR gate which has already been regarded in the last section can again be used as an example to demonstrate this shortcoming. In Fig. 3.6 the cycle accurate power estimation for selected events on single or multiple inputs is compared to the circuit simulation reference. The power consumption of the single-input event in the second cycle is estimated perfectly but for switching of three inputs in the fifth cycle the power is underestimated by 20 %. The lookup based power estimation fails completely in the third and fourth cycle that both show two input events which cancel out the output effect that would have been related to each single-input event. As the lookup tables in the cell library that are dependent on both the transitions on the input and output do not contain events for switching of inputs without activity on the output, no matching power values can be found for either of the input switching events and power cannot be estimated at all. Consequently, this effect is most pronounced for gates like XOR gates or full adders where all single input events result in output switching while quasisimultaneous switching of multiple inputs might not cause the output state to change.

| 20.200.0 | circuit function     | number of gates |         |         |  |

|----------|----------------------|-----------------|---------|---------|--|

| name     |                      | CMOS40          | CMOS28a | CMOS28b |  |

| C432     | Interrupt Controller | 87              | 75      | 75      |  |

| C499     | $\operatorname{SEC}$ | 154             | 185     | 157     |  |

| C880     | ALU                  | 150             | 158     | 153     |  |

| C1355    | $\operatorname{SEC}$ | 131             | 194     | 149     |  |

| C1908    | SEC/DED              | 180             | 190     | 184     |  |

| C2670    | ALU/Controller       | 342             | 352     | 358     |  |

| C3540    | ALU                  | 454             | 477     | 444     |  |

| C5315    | ALU                  | 586             | 635     | 639     |  |

| C6288    | 16-bit Multiplier    | 599             | 623     | 609     |  |

| C7552    | Adder/Comparator     | 729             | 766     | 693     |  |

Table 3.1: Characteristics of the ISCAS85 circuits

#### 3.3 Benchmarking of estimation accuracy

In order to evaluate the accuracy of gate-level power estimation, a range of typical circuits was analyzed using two commercial gate-level power estimation flows. The reference power consumption data against which the estimations are compared was generated using physical-level circuit simulation running the same testbench as during estimation. In order to be independent of discrepancies caused by specific technologies or library files, this analysis was carried out using three different advanced commercial CMOS technologies: CMOS40 is a 40-nm CMOS technology while CMOS28a and CMOS28b are both 28-nm CMOS technologies from two different foundries. All benchmark circuits were implemented using the foundry-supplied general purpose standard cell libraries.

#### 3.3.1 ISCAS85 circuits

One of the most widely used benchmark suites which is commonly known as ISCAS85 stems from the International Symposium of Circuits and Systems in 1985 [62]. This package consists of 10 purely combinatorial industrial designs that were originally published as flattened gate netlists without description of the implemented function. Over the years these circuits have been used in a variety of fields from logic synthesis to test pattern generation. Because of their wide acceptance, individual circuits from this benchmark set have also quite commonly been used to demonstrate power estimation methodologies. For the purpose of this comparison, the original netlists where implemented using standard cell synthesis. The characteristics of the results after place and route for all three technologies are summarized in Table 3.1.

The ISCAS85 circuits were analyzed using both physical circuit simulation and gatelevel power estimation using two different commercial tool suites. The power consumption observed during circuit simulation is regarded as the reference in the following comparison. As no realistic testbenches are published for the ISCAS85 circuits, the circuit simulation as well as the gate-level power estimations assume the same stream of uniformly distributed random vectors on the circuit inputs for a duration of 1000 cycles. The main focus of this analysis is the handling of effects due to real gate delays which have little to no impact on the static power consumption. Therefore, the total power consumption was separated into dynamic and static power. Gate-level power estimation reports separate figures for dynamic and static power by default. In circuit simulation this separation was performed according to (2.8) and (2.9) by varying the operating frequency while executing the same testbench.

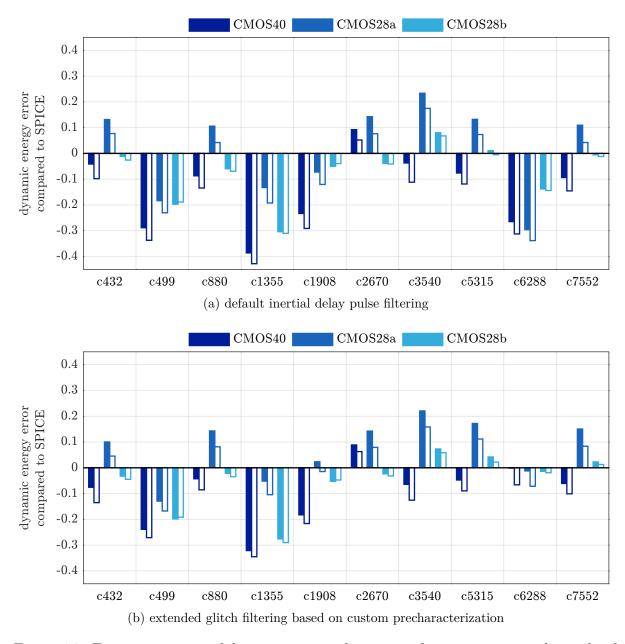

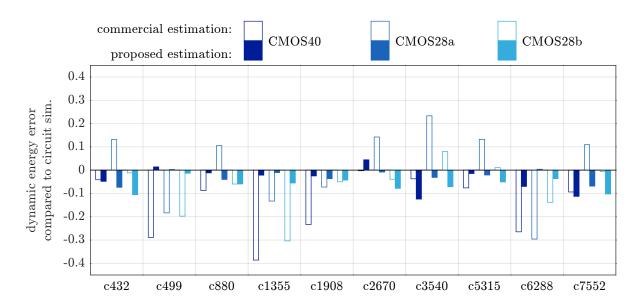

The estimates for dynamic energy dissipation of both commercial tool suites, denoted as  $Tool\ A$  and  $Tool\ B$ , are compared to the reference from SPICE-level circuit simulation in Fig. 3.7a. The mean deviation from the circuit simulation result is as high as 14.6% or 15.2% for Tool A and Tool B respectively. Even more interestingly the dynamic energy is overestimated by up to 23% for some circuits while it is underestimated by up to 43% for others. The highest errors can be observed for circuits c499, c1355 and c6288. Upon closer analysis it is found that this error is mainly caused by the use of large XNOR gates with three or four inputs for c499 and c1355, which implement error detection functions, and full-adders in c6288, which represents a 16-bit multiplier. These types of gates are examples for compound gates that suffer both from excessive pulse filtering when using the default inertial gate delay model as described in section 3.1 as well as from missing library table entries for multi-input events as elaborated in section 3.2.

While the errors due to simplifications of the provided library are inherent to the state-of-the-art power estimators, the misestimation of switching activities can be reduced by more complex glitch filtering. Since no information on the minimum pulse width on gate inputs that leads to propagation is included in the default characterization library, a custom precharacterization of all cells used in the netlist is required in order to determine the propagation properties. This additional information can be used to pre- and postprocess the data related to the logic simulator, resulting in more realistic glitch filtering [4]. As shown in Fig. 3.7b, the estimation error can be reduced for most circuits by inclusion of extended glitch filtering. In particular, the errors during the original estimation of circuit c6288 appear to be almost exclusively caused by over-aggressive pulse filtering

Figure 3.7: Estimation error of dynamic energy dissipation for two commercial gate-level power estimators (filled bars: Tool A, empty bars: Tool B) compared to SPICE-level circuit simulation for three CMOS technologies.

in the inertial delay model. In contrast, the estimation for the problematic circuits containing large XNOR gates still shows underestimation of up to 34.5% despite significant improvements. An explanation of this discrepancy is found when the maximum logic depth, which measures the number of gates that are connected in series, is compared for both circuit types. For the multiplier circuit c6288 the logic depth is found to be 36 or 37 for all technologies while a maximum of only 14 gates are connected in series for the error detection circuits. Resulting from the three times higher logic depth, the accurate propagation of glitches becomes critical for c6288, because a large number of gates are

| nama   | number of gates (number of registers) |              |             |  |  |

|--------|---------------------------------------|--------------|-------------|--|--|

| name   | CMOS40                                | CMOS28a      | CMOS28b     |  |  |

| s27    | 14 (3)                                | 20 (3)       | 13 (3)      |  |  |

| s208   | 45 (8)                                | 52 (8)       | 56 (8)      |  |  |

| s298   | 76 (14)                               | 88 (14)      | 86 (14)     |  |  |

| s344   | 87 (15)                               | 126 (15)     | 100 (15)    |  |  |

| s349   | 89 (11)                               | 117 (15)     | 105 (15)    |  |  |

| s382   | 126(21)                               | 148(21)      | 128 (21)    |  |  |

| s386   | 78 (6)                                | 80 (6)       | 74(6)       |  |  |

| s400   | 127(21)                               | 136(21)      | 124(21)     |  |  |

| s420   | 101 (16)                              | 105 (16)     | 110 (16)    |  |  |

| s444   | 128(21)                               | 143 (21)     | 128 (21)    |  |  |

| s510   | 123(6)                                | 126 (6)      | 130 (6)     |  |  |

| s526   | 119(21)                               | 129(21)      | 134(21)     |  |  |

| s641   | 111 (14)                              | 127 (14)     | 110 (14)    |  |  |

| s713   | 110 (14)                              | 130 (14)     | 108 (14)    |  |  |

| s820   | 136 (5)                               | 137 (5)      | 127 (5)     |  |  |

| s832   | 129(5)                                | 132 (5)      | 131 (5)     |  |  |

| s838   | 183 (32)                              | 208(32)      | 215 (32)    |  |  |

| s1196  | 271 (18)                              | 270 (18)     | 271 (18)    |  |  |

| s1238  | 288 (18)                              | 274 (18)     | 272 (18)    |  |  |

| s1423  | 458 (74)                              | 592 (74)     | 475 (74)    |  |  |

| s1488  | 284(6)                                | 301 (6)      | 294(6)      |  |  |

| s1494  | 296 (6)                               | 297(6)       | 297(6)      |  |  |

| s5378  | 776 (162)                             | 966 (162)    | 911 (162)   |  |  |

| s9234  | 655 (132)                             | 898 (132)    | 705 (132)   |  |  |

| s13207 | 1009(213)                             | 1365 (213)   | 1111 (213)  |  |  |

| s15850 | 585 (128)                             | 675 (128)    | 655 (128)   |  |  |

| s35932 | 8096 (1728)                           | 12427 (1728) | 9488 (1728) |  |  |

| s38417 | 6589 (1462)                           | 8912 (1462)  | 8200 (1462) |  |  |

| s38584 | 7166 (1159)                           | 9428 (1159)  | 7498 (1159) |  |  |

Table 3.2: Characteristics of the ISCAS89 circuits

potentially affected by glitch pulses propagating along logic paths. Quasisimultaneous switching resulting in errors during energy lookup on the other hand is more likely for shorter and more balanced signal paths as found in the error detecting circuits.

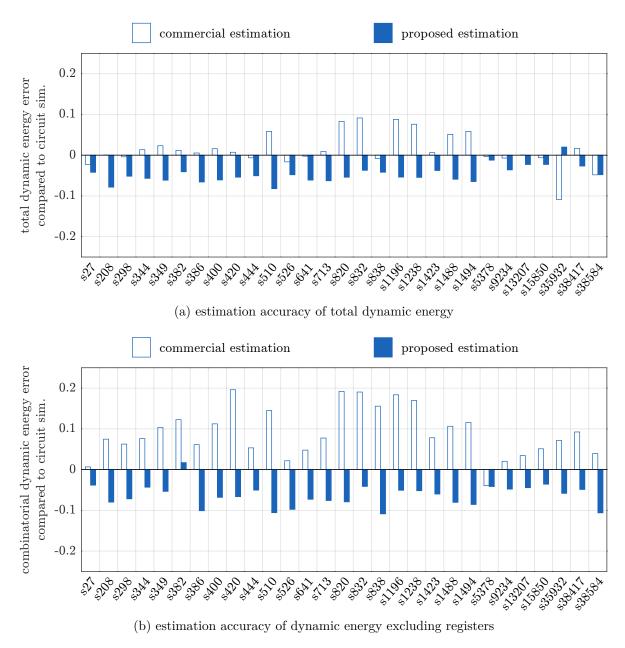

#### 3.3.2 ISCAS89 circuits

In order to extend the complexity of the ISCAS85 benchmarks as well as to provide the opportunity to benchmark scan-based test generation algorithms, during the *International Symposium of Circuits and Systems* in 1989 a set of sequential circuits was distributed [63] that was compiled from industrial and university sources and is commonly known as

(b) estimation accuracy of dynamic energy excluding registers

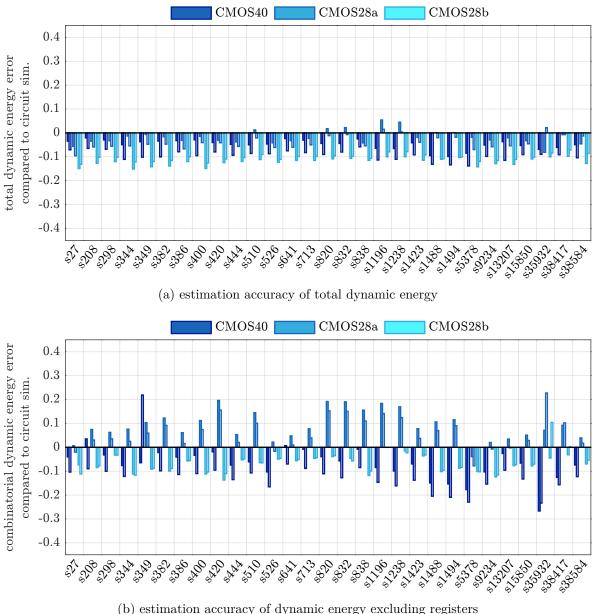

Figure 3.8: Estimation error of dynamic energy dissipation for two commercial gate-level power estimators (filled bars: Tool A, empty bars: Tool B) compared to SPICE-level circuit simulation for two CMOS technologies.

ISCAS89. As with the ISCAS85 circuits, the benchmark circuits were published as gatelevel netlists without logical hierarchy and mostly without functional description. The gate counts resulting from implementation of the ISCAS89 benchmark circuits in the analyzed technologies as well as number of internal states are summarized in Table 3.2. In addition to the inclusion of sequential cells, this benchmark set contains significantly more complex circuits than could be found in the ISCAS85 set.

Analogous to the analysis of the purely combinatorial circuits the placed and routed netlists including parasitic components were employed in an evaluation of the dynamic energy estimated using two leading gate-level estimators. The resulting deviations from the reference obtained by physical-level circuit simulation, which are plotted in Fig. 3.8a, show considerably smaller maximum errors than could be observed for the ISCAS85 circuits. In particular, the implementations in technology *CMOS28a* seem to exhibit a high estimation accuracy, while circuits implemented in technology *CMOS28b* are seemingly prone to underestimation of about 10%. Upon closer analysis of the estimation results these observations can be attributed to the fact, that the energy dissipation of the registers contained in the ISCAS89 circuits is generally underestimated for all technologies. This cancels out part of the overestimation of combinatorial gates for implementations in technology *CMOS28a* which is common for this technology as shown in Fig. 3.8b. In addition, the maximum overestimation of up to 23% of combinatorial gates which is observed for the implementation of circuit *s35932* only marginally contributes to the overall estimation error because the power of sequential cells dominates the overall energy dissipation for this circuits. This effect can also be observed for the maximum underestimation of combinatorial gates of 27% for the same circuit in technology *CMOS40*.

The compensation of overestimation of the energy dissipation for some components or modules of a circuit with underestimation of other parts is a typical feature which can be observed for the power estimation of larger digital circuits. However, this averaging effect which results in apparently good estimation accuracy for a majority of circuits cannot be guaranteed. As a worst case assumption the possibility of mutual reinforcement of individual errors needs to be considered.

This consideration motivates the search for modifications or full replacements of the prevalent gate-level power estimation methodologies. A major goal will be an improved handling of delay effects which enable glitch creation and propagation in order to mitigate one of the biggest deficiencies that was identified in this chapter.

# 4 Probabilistic macromodels considering glitch parameters

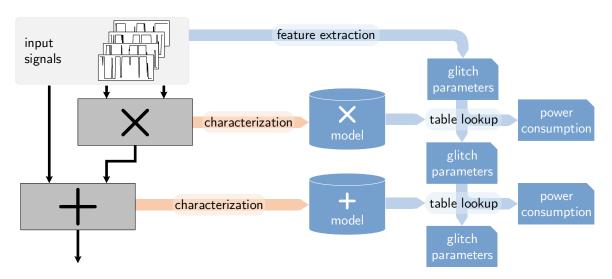

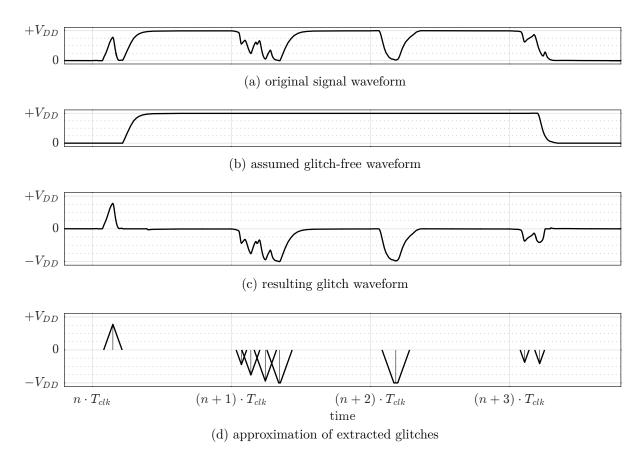

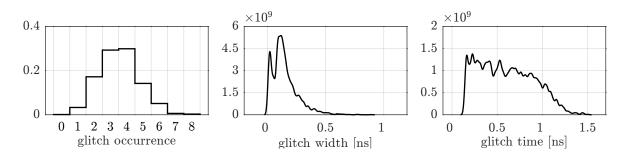

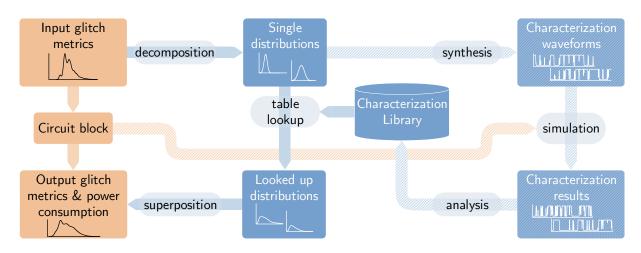

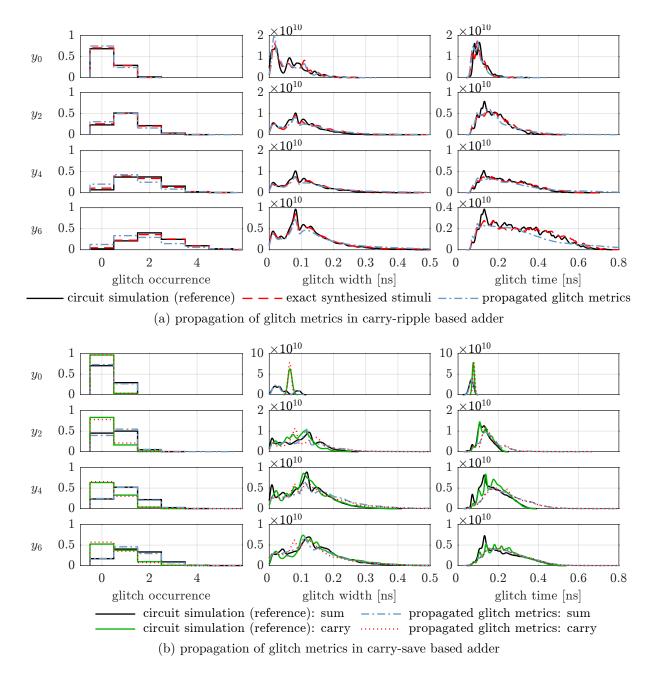

Motivated by the challenge of accounting for glitches using logic simulation, this chapter explores alternative ways of representing the underlying increase in switching activity. In the scope of macromodels as defined in section 2.2 this requires the definition of suitable parameters that can be used as inputs to a precharacterized lookup table to determine the effect of glitches at the input of the circuit macro of interest. Switching induced by the desired evaluation of the logic function is thereby separated from glitches caused by unbalanced delays. As depicted in Fig. 4.1 a general power estimation flow following the macromodeling approach starts by extracting these glitch parameters from the primary inputs of the circuit to be analyzed. Using the precharacterized models of circuit components, the power consumption induced by the evaluated values for glitch parameters can be looked up. At the same time, the model can be used to look up the values for the selected glitch parameters that could be observed at the output of the circuit component if the inputs would be stimulated according to the extracted input parameters. This

Figure 4.1: Schematic view of macromodel evaluation with integrated propagation of parameter values.

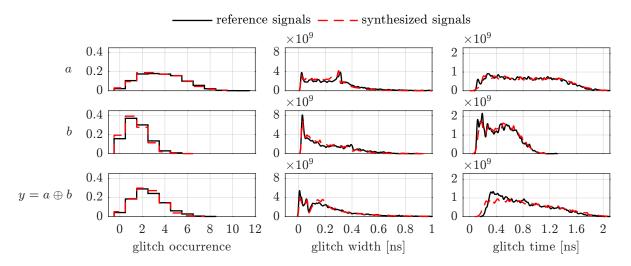

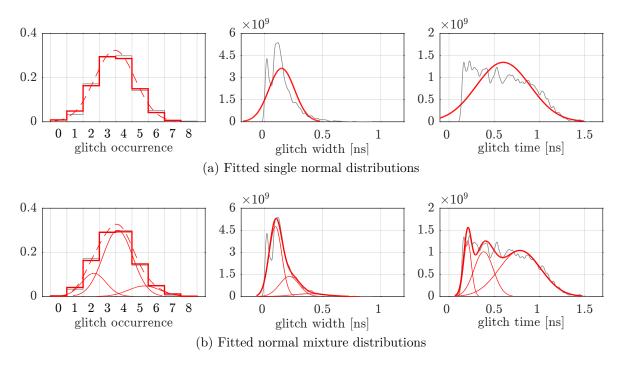

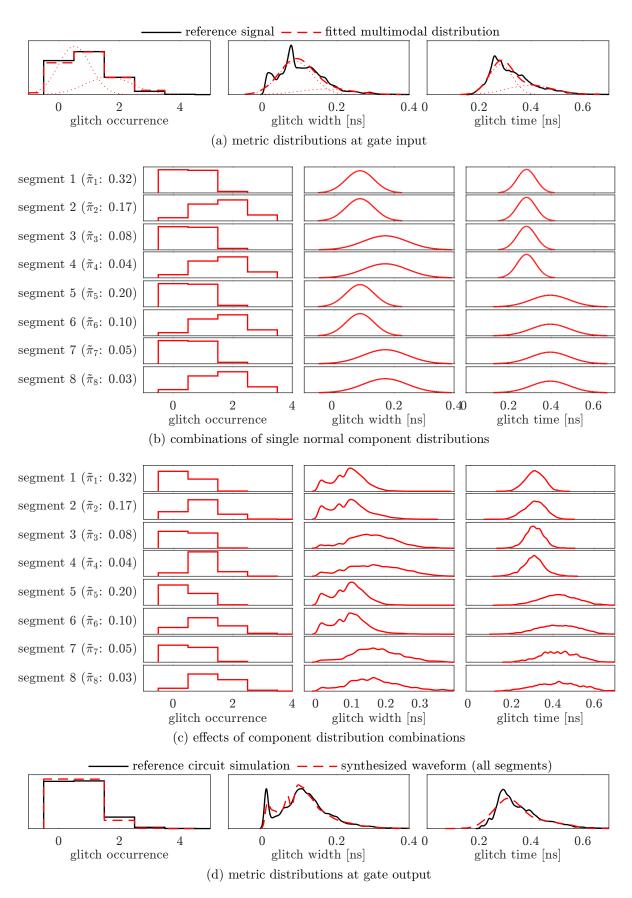

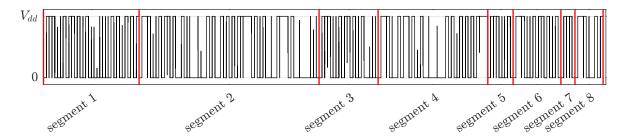

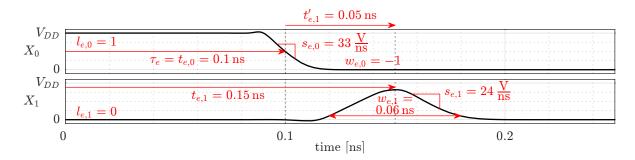

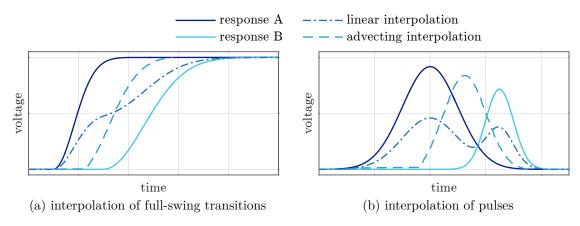

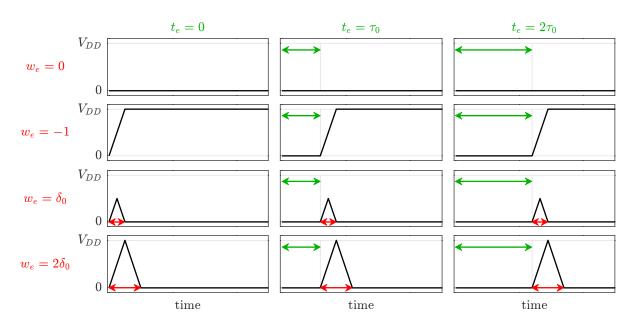

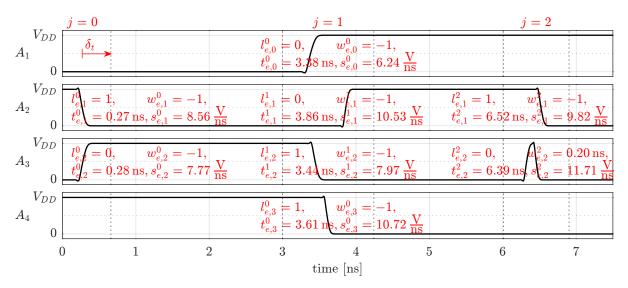

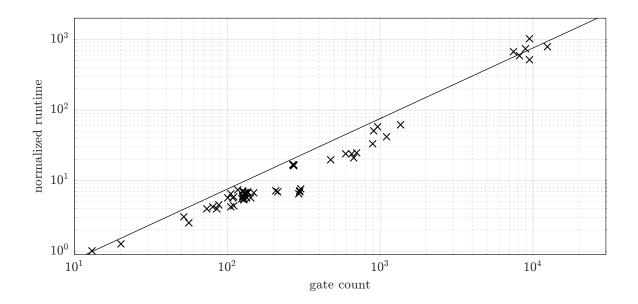

method of parameter propagation replaces time-consuming delay annotated logic simulation and holds promise for high accuracy because the parameter responses stored in the characterization library are based on accurate circuit simulation. The propagated glitch parameters subsequently form inputs to the power models of downstream components in the circuit hierarchy allowing for iterative analysis of all circuit components.