# GROWTH AND CHARACTERIZATION OF INAS NANOWIRE-BASED JOSEPHSON JUNCTIONS

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

Sree Koti Subha Pujitha Perla, M.Sc. aus Visakhapatnam, India

Berichter: apl. Prof. Dr. rer. nat. Thomas Schäpers Univ.-Prof. Dr. sc. ETH Christoph Stampfer

Tag der mündlichen Prüfung: 02.06.2022

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

# **Contents**

| De               | eclaration                                                                                                                              | 1                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Acknowledgements |                                                                                                                                         |                      |  |

| Αŀ               | ostract                                                                                                                                 | 4                    |  |

| Ζu               | sammenfassung                                                                                                                           | 5                    |  |

| 1                | Introduction 1.1 Scope Of This Work                                                                                                     | <b>6</b><br>7        |  |

| 2                | Theory  2.1 Growth Of Thin Films                                                                                                        | 13<br>15             |  |

| 3                | Experimental And Characterization Techniques  3.1 Growth Techniques                                                                     |                      |  |

| 4                | Sample Fabrication  4.1 Silicon (111) Substrate Preparation                                                                             | 29<br>34<br>35<br>35 |  |

| 5                | Substrate Analysis5.1 Si (111) Substrate Preparation5.2 Effect Of Reactive Ion Etching5.3 AFM Analysis5.4 Si(100) Substrate Preparation | 40<br>43             |  |

| 6                | InAs And InAs-Te Doped Nanowires  6.1 InAs Nanowires                                                                                    |                      |  |

| 7                | InAs/Al Nanowires 7.1 Aluminium Half-shell Growth                                                                                       | 74<br>75             |  |

| 8                | In-situ Josephson junctions via shadow evaporation |                                             |     |  |

|------------------|----------------------------------------------------|---------------------------------------------|-----|--|

|                  | 8.1                                                | Introduction                                | 79  |  |

|                  | 8.2                                                | Nanowire Growth On Tilted Si (111) Surfaces | 80  |  |

|                  | 8.3                                                | InAs/Al Nanowires                           | 81  |  |

|                  | 8.4                                                | InAs/Nb Nanowires                           |     |  |

| 9                | Sun                                                | nmary And Outlook                           | 98  |  |

| Appendix         |                                                    |                                             |     |  |

|                  | 9.1                                                | Substrate Preparation                       | 102 |  |

|                  | 9.2                                                | GaAs Nanowire Selective Area Epitaxy        | 105 |  |

|                  |                                                    | In-situ Josephson Junctions                 |     |  |

| Lis              | st of                                              | Publications                                | 124 |  |

| Li               | List of Presentations                              |                                             |     |  |

| Curriculum Vitae |                                                    |                                             |     |  |

# Declaration of authorship

- I, Sree Koti Subha Pujitha Perla declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research. I do solemnely swear that:

- 1. This work was done wholly or mainly while in candidature for the doctoral degree at this faculty and university;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this university or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others or myself, this is always clearly attributed;

- 4. Where I have quoted from the work of others or myself, the source is always given. This thesis is entirely my own work, with the exception of such quotations;

- 5. I have acknowledged all major sources of assistance;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published before as:

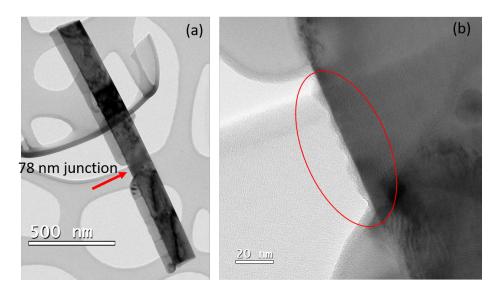

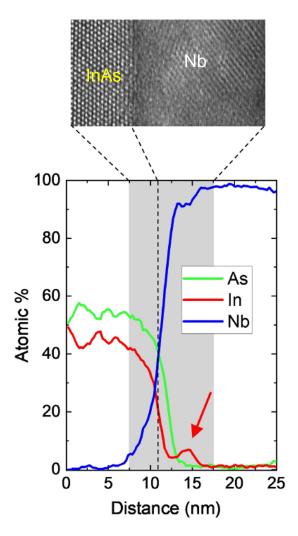

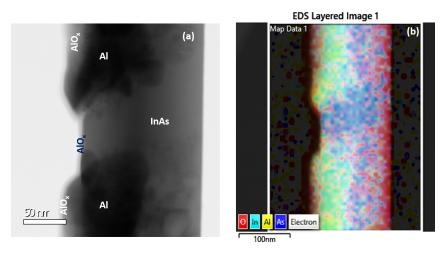

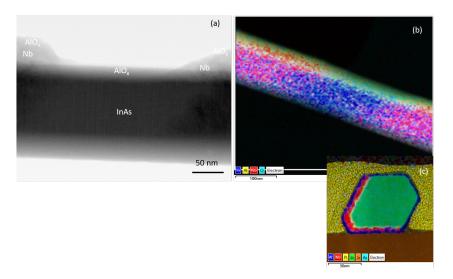

- Pujitha Perla, H. Aruni Fonseka, Patrick Zellekens, Russell Deacon, Yisong Han, Jonas Kölzer, Timm Mörstedt, Benjamin Bennemann, Abbas Espiari, Koji Ishibashi, Detlev Grützmacher, Ana M. Sanchez, Mihail Ion Lepsa, and Thomas Schäpers. Fully in situ Nb/InAs-nanowire josephson junctions by selective-area growth and shadow evaporation. Nanoscale Adv., 3:1413–1421, 2021.

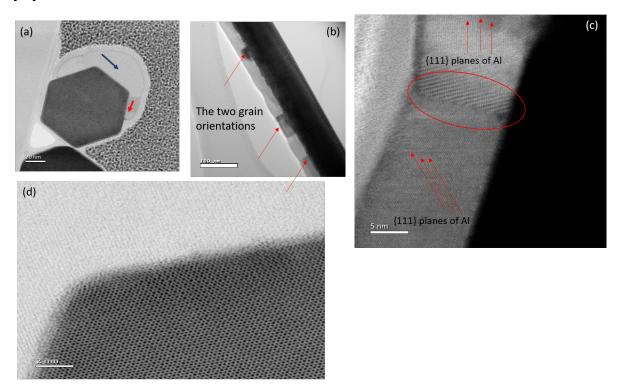

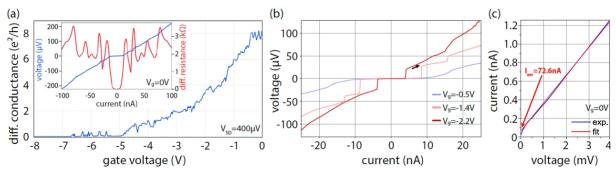

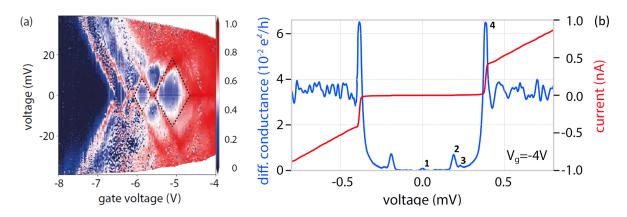

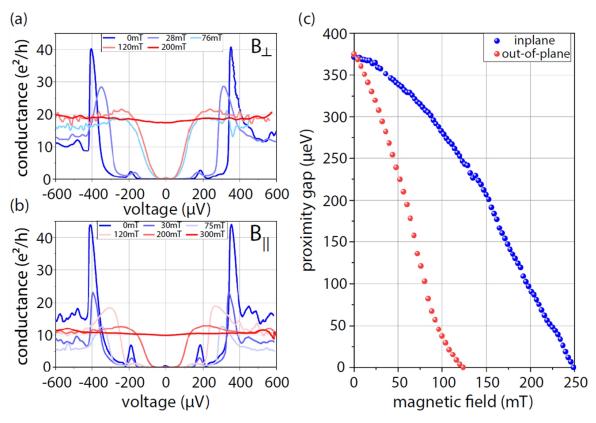

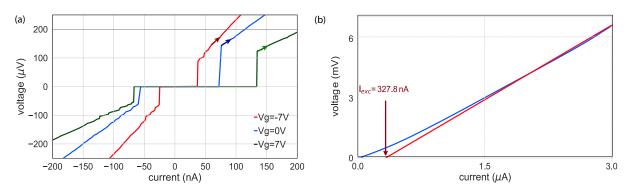

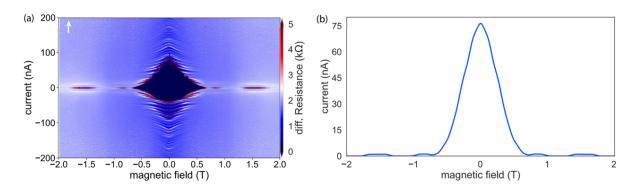

- Patrick Zellekens, Russell Deacon, Pujitha Perla, H. Aruni Fonseka, Timm Mörstedt, Steven A. Hindmarsh, Benjamin Bennemann, Florian Lentz, Mihail I. Lepsa, Ana M. Sanchez, Detlev Grützmacher, Koji Ishibashi, and Thomas Schäpers. Hard-Gap Spectroscopy in a Self-Defined Mesoscopic InAs/Al Nanowire Josephson Junction. Phys. Rev. Applied 14, 054019, 2020.

- Perla, Pujitha and Faustmann, Anton and Koelling, Sebastian and Zellekens, Patrick and Deacon, Russell and Fonseka, H. Aruni and Kölzer, Jonas and Sato, Yuki and Sanchez, Ana M. and Moutanabbir, Oussama and Ishibashi, Koji and Grützmacher, Detlev and Lepsa, Mihail Ion and Schäpers, Thomas *Te-doped selective-area grown InAs nanowires for superconducting hybrid devices*. PhysRevMaterials., 6.024602, 2022.

Signed: Perla Sree Koti Subha Pujitha

Place & Date:

# Acknowledgements

I would like to thank Prof. Detlev Grützmacher for the opportunity to work at PGI-9.

Prof. Dr. Thomas Schäpers, has been a mentor, supervisor, and a friend. He is the kind of leader that takes care of you and pushes you gently towards the goal. He never inhibits new ideas or approaches. He always gave me this kind of freedom which helped me find solutions to different scientific challenges. I offer my sincere appreciation for the innumerable tutorial sessions on different scientific topics, and learning opportunities, that was a great deal of help. I would like to thank him heart fully for giving me an opportunity to work in the group and improve my capabilities within nanotechnology and learn a whole lot more about nanomaterials and devices than, I ever did before embarking on this journey. You have taught me to be more kind, patient, humble, and also how to diffuse tense situations (life hacks!). Thank you for your continued support and encouragement throughout my Ph.D. time, and for being a big pillar of support during my visa extension.

Thank you Prof. Dr. Christoph Stampfer, for agreeing to be a second supervisor for the thesis and giving a careful reading of it.

I would like to thank Dr. Mike Lepsa, for several helpful discussions, as well as a careful reading of the thesis.

I would like to thank Christoph Krause for his daily work in keeping the MBE running, introducing me to the MBE technique, helping me with transferring my samples, every other time with a lot of patience. Also for all the funny and insightful conversations.

Dr. Christian Weyrich, a gentle giant as he is known, has been an inspiration to me. Thank you for helping me with assimilating into the environment in our group. All the funny conversations we had, were memorable times. I have learned a lot from your work and your down-to-earth attitude. Thanks for the wonderful two years in the office. I really enjoyed it. Jonas Kölzer, thanks for your immense patience with me. Thanks for all the time you spent training me in the MAGLAB. You have been an amazing friend through thick and thin. I truly enjoyed all our conversations, the numerous bus rides, and our cooking sessions. You taught me to be patient and curious, and lighthearted. Thanks for sitting through most of my visa sessions, translating my agonies to a grumpy old man at the immigration office.

Valerie, thank you for being there and for your immense patience to help me with my visa/job center applications. It was a lot of fun writing the thesis together and all the dining!

Anton, thanks for your help with the manipulator, careful reading of my thesis, and your patience, and support.

I would like to thank all our collaborators: TEM (Transmission electron microscopy) support has been extended by Dr. H. Aruni Fonseka and Prof. Ana M Sanchez from the department of Physics, University of Warwick, UK.

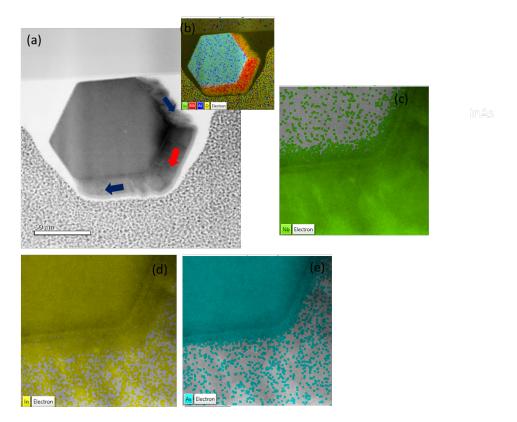

APT (Atom Probe Tomography) support has been extended by Dr. Sebastian Kölling and Dr. Oussama Moutanabbir from the department of Engineering Physics, Polytechnique Montreal, Canada.

Low temperature electrical measurements supported by Dr. Russell Deacon, Patrick Zellekens, and Prof. Koji Ishibashi from RIKEN Center for Emergent Matter Science and Advanced Device Laboratory, Japan.

I am grateful for an amazing support I received during my thesis from numerous kind people namely, Tobias Ziegler, Gerrit Behner, Tobias Schmitt, Michael Schleelvoigt, Miriam Rathas, Timm Moerstedt, Patrick Bernardy, Benjamin Bennemann, Mingshan Liu, Johanna Jansen, Marvin Janssen, Silke Piper, Christine Servo, and Herbert Kertz. I would like to thank all cleanroom staff from HNF, more importantly, Dr. Elmar Neumann, Stephy Bunte, Dr. Florian Lentz, Dr. Stefan Trellenkamp, Matthias Geitner, Dr. Jhih Sian Tu, Dr. Thomas Grap, for all their valuable support and guidance.

Finally, my deep and sincere gratitude to my family and my guru Sathya sai for their continuous and unparalleled love, help, and support. I am grateful to my brothers Perla Ananth Maruthi and Perla Gowra Hari for always being there for me. I am forever indebted to my parents P.V. Anjaneyulu and K. Satyavathi for giving me the opportunities and experiences that have made me who I am.

## **Abstract**

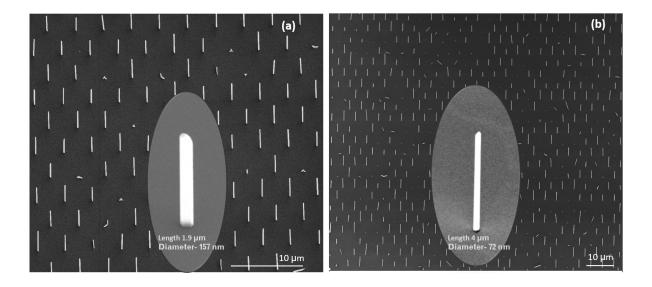

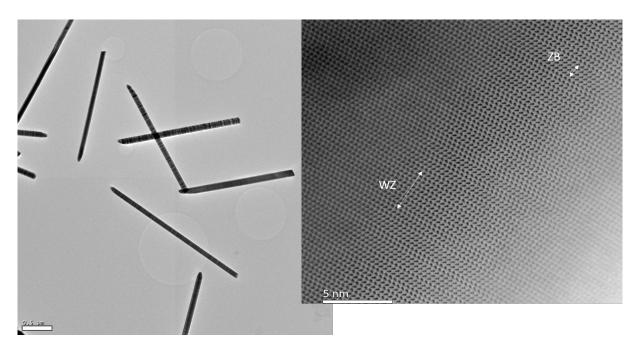

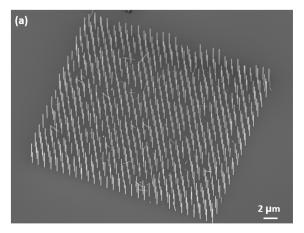

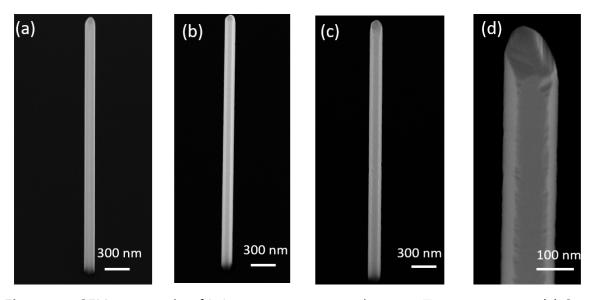

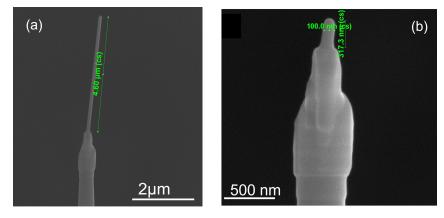

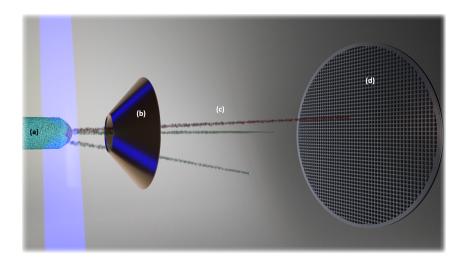

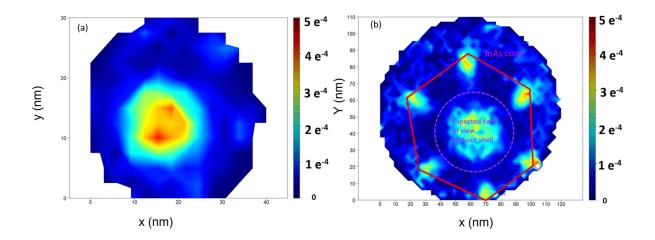

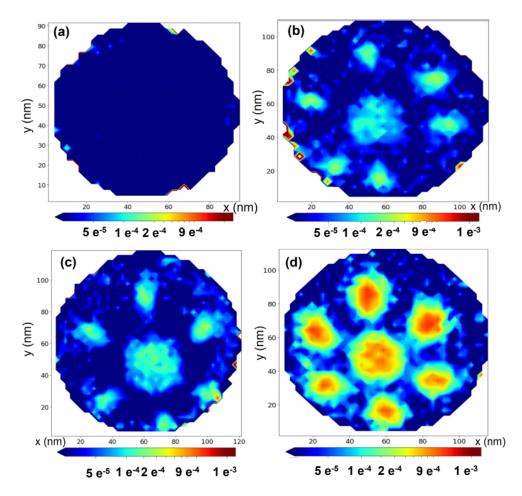

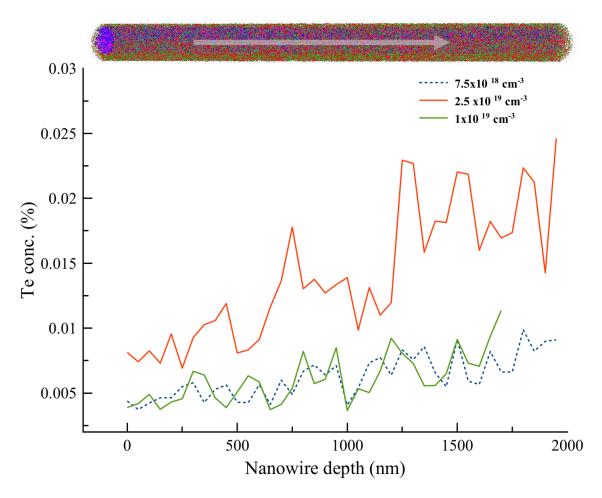

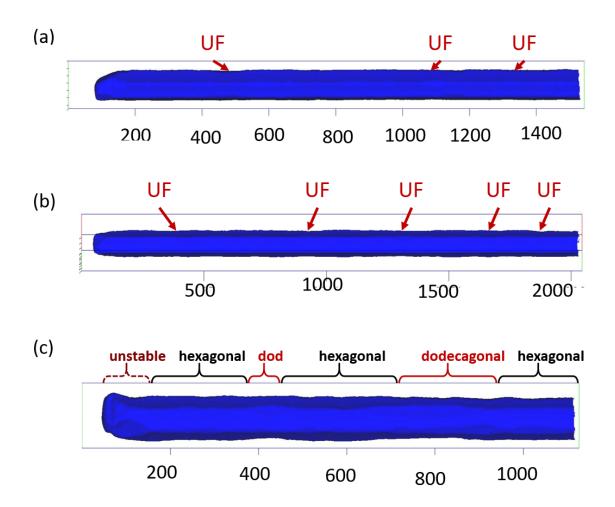

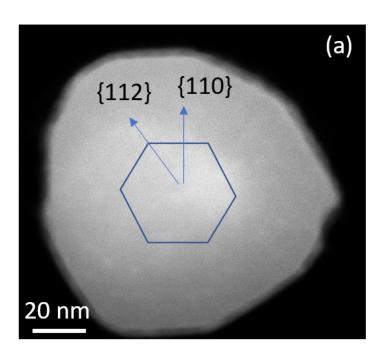

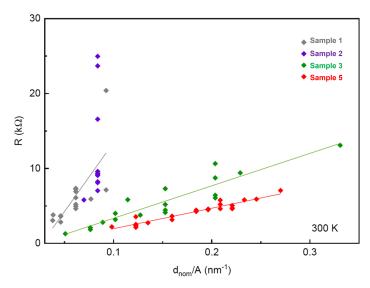

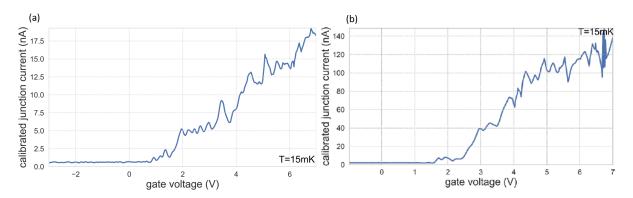

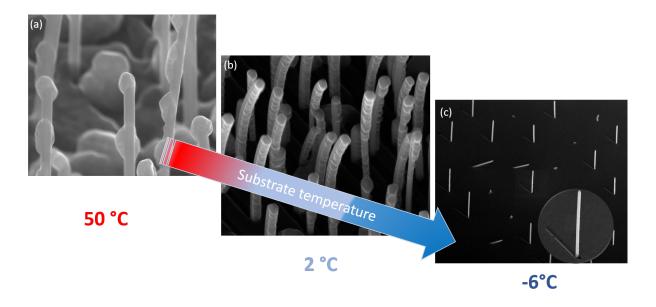

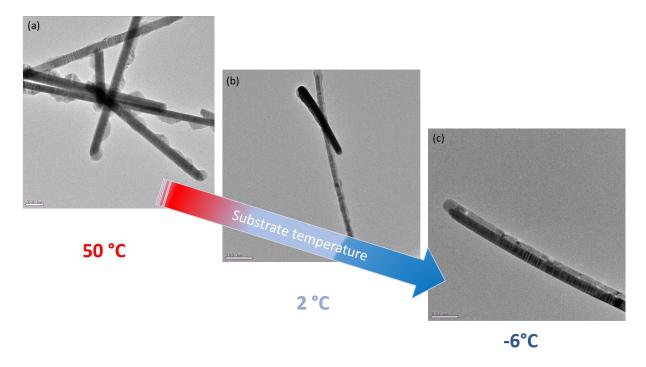

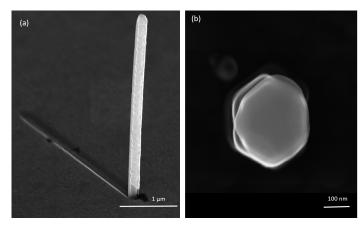

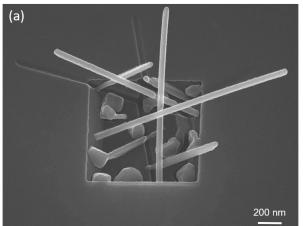

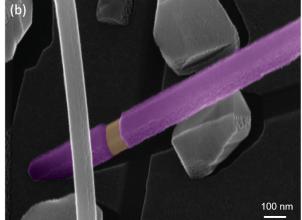

This work delves into the growth mechanism as well as structural and electrical characterization of InAs nanowires (NWs) for Josephson junctions. The superconductors used in this case are aluminum and niobium. Josephson junctions are an essential component of a superconducting qubit. This work describes the evolution of the Josephson junctions within the state-of-the-art and achieving higher transparency of the semiconductor/superconductor interfaces. The first part of the work deals with the optimization of the selective area growth. This method offers greater control of the growth of nanowires and provides higher uniformity. Parameters such as temperature, indium growth rate, and arsenic beam equivalent pressure (BEP) have been optimized to achieve a growth yield of 95%, using a 20 nm thick silicon dioxide mask on a Si(111) substrate. Eventually, the InAs nanowires are grown and optimized for diameters of 70-80 nm and lengths of 4-5  $\mu$ m. Additional experiments have been performed to dope the InAs nanowires with tellurium. In the case of Josephson junctions, they offer a huge asset, with a doping range of  $1 \times 10^{18} \, \mathrm{cm}^{-3}$  to  $1 \times 10^{19} \, \mathrm{cm}^{-3}$ . An increase in the conductance of these nanowires is observed with increased doping and thereby an enhanced critical current of the Josephson junctions. Moreover, Te doping has shown an impact on the diameter and the length of the nanowires, since it is a surfactant. Atom probe tomography investigations performed on these nanowires show additional (211) lateral facets, that shift the hexagonal structure of the InAs nanowire to a partly dodecagon structure at Te doping concentrations greater than  $1\times10^{19}\,\mathrm{cm}^{-3}$ . Furthermore, the transparency of the lnAs/superconductor interface has been tuned. A defect-free interface and a smooth film of a superconductor is a pre-requisite for a high-quality Josephson junction, since this ensures a good coupling between the materials. A complete in-situ method has been adopted, to grow Al and Nb, onto the nanowires, thereby eliminating, any possible exposure of the semiconductor surface to the ambient. To achieve defect-free semiconductor/superconductor interfaces, a brief degassing step is introduced to the nanowires before the growth of the superconducting metals such as aluminum or niobium. This process, ensured enhanced transparency between the materials, thereby strengthening the coupling, by that improving the proximity effect. To be brief, the proximity effect induces Cooper pairs into the semiconductor, i.e. it turns the NW partly into a superconductor. Furthermore, the growth parameters of the metals evaporated are optimized to produce a smooth and defect-free interface and are investigated systematically. Lastly, the in-situ approach is expanded to encompass the fabrication of Josephson junctions at ultra-high vacuum conditions and to include other superconducting and capping materials in the process. The substrates made for this purpose have been prepared in such a way that two nanowires grow in a square trench at  $90^{\circ}$  to the planes of the trench. The growth windows for the NW growth are meticulously and selectively placed in such a way that one NW shadows the other during the metal evaporation, thus, causing a junction on the latter wire. The superconductors used in this process are optimized to create smooth and defect-free layers. In the case of aluminum, the growth of the metals is found to depend more on the temperature than on the angle of deposition. In contrast, for Nb, the angle of evaporation has a huge effect on the smoothness of the film. The investigations presented in these sections include transmission electron microscopy and corresponding low-temperature electrical measurements. This shadow approach, increased the metal evaporation angles onto the nanowires, from 30° to 87°, thus causing smooth and defect-free layers. This has also been shown to increase the interface transparency, between the NW and the superconductors. Lastly, this platform has also been used to demonstrate the growth of complex NW networks and multiple Josephson junctions.

# Zusammenfassung

Josephson-Ubergänge sind ein wesentlicher Bestandteil von supraleitenden Qubits. Diese Arbeit beschreibt deren Weiterentwicklung auf Basis von selektivem Wachstum von Halbleiternanodrähten und in-situ Prozessierung. Die hierfür hergestellten InAs-Nanodrähte wurden zunächst strukturell und elektrisch charakterisiert. In den entsprechenden Josephson-Übergängen mit Aluminium und Niob Elektroden konnte nachfolgend eine höhere Transparenz der Halbleiter-Supraleiter-Grenzfläche festgestellt werden. Im ersten Teil beschäftigt sich diese Arbeit mit der Optimierung des selektiven Wachstums. Diese Methode bietet eine größere Kontrolle und ermöglicht somit eine höhere Gleichmäßigkeit des Wachstums der Nanodrähte. Parameter wie Temperatur, Indium-Depositionsrate und Arsendruck wurden optimiert, so dass am Ende eine Ausbeute von 95% erreicht wurde, wobei eine 20 nm dicke Siliziumdioxidmaske auf einem Si(111)-Substrat verwendet wurde. Das optimale Ergebnis wird bei InAs-Nanodrähte mit Durchmesser von 70-80 nm und Längen von 4-5  $\mu$ m erreicht. Zusätzlich wurden die InAs-Nanodrähte mit Tellur dotiert. Im Falle von Josephson-Übergängen bietet eine Dotierung im Bereich von  $1 \times 10^{18}\,\mathrm{cm^{-3}}$  bis  $1 \times 10^{19}\,\mathrm{cm^{-3}}$  den großen Vorteil, dass eine Erhöhung der Leitfähigkeit der Nanodrähte und damit des kritischen Stroms der Josephson-Übergänge beobachtet wird. Gleichzeitig hat die Te-Dotierung einen Einfluss auf den Durchmesser und die Länge der Nanodrähte handelt, da es sich um einen oberflächenaktiven Stoff. Atomsondentomographieuntersuchungen zeigen zusätzliche laterale Facetten (211), welche die hexagonale Struktur des InAs-Nanodrahtes bei Dotierungskonzentrationen größer als  $1 \times 10^{19}\,\mathrm{cm}^{-3}$ zu einer teilweise dodekagonalen Struktur verändern. Weiterhin konnte die Transparenz der InAs/Supraleiter-Grenzfläche erhöht werden. Eine defektfreie Grenzfläche und eine glatte Schicht des Supraleiters ist eine Voraussetzung für einen hochwertigen Josephson-Ubergang, da dies eine gute Kopplung zwischen den Materialien gewährleistet. Hierzu wurde eine vollständige in-situ-Methode angewandt, um Al und Nb auf die Nanodrähte zu deponieren, wodurch eine Kontamination der Halbleiteroberfläche durch Luft vermieden wird. Die gezüchteten Nanodrähte werden hierzu vor der Deposition der supraleitenden Metalle Aluminium oder Niob kurz entgast. Eine Optimierung durch systematische Untersuchungen der Depositionsparameter für die Metalle führt zu einer glatten und defektfreien InAs/Supraleiter-Grenzfläche mit erhöhter Transparenz. Dies ermöglicht die Beobachtung des Proximity-Effekts, bei dem Cooper-Paare in den Halbleiter induziert werden, d.h. der Nanodraht wird teilweise zu einem Supraleiter. Final wird der in-situ-Ansatz für die Herstellung von Josephson-Übergängen bei Ultrahochvakuum-Bedingungen durch die Deposition einer Schutzschicht gegen Oxidation ergänzt. Die zu diesem Zweck hergestellten Substrate werden so präpariert, dass zwei Nanodrähte in einem quadratischen Graben im Winkel von 90° zur Oberfläche des Grabens orientiert sind. Die Nanodrähte werden selektiv so platziert, dass ein Nanodraht den anderen während der Metallverdampfung beschattet und so ein Josephson-Ubergang auf dem letzteren Draht entsteht. Im Falle von Aluminium wird festgestellt, dass das Wachstum der Metalle mehr von der Temperatur als vom Abscheidungswinkel abhängt. Im Gegensatz dazu hat bei Nb der Verdampfungswinkel einen großen Einfluss auf die Glattheit der Schicht. Die an diesen Übergängen durchgeführten Untersuchungen umfassen Transmissionselektronenmikroskopie- und entsprechende Quantentransportmessungen. Eine Erhöhung des Depositionswinkels des Metalls auf die Nanodrähte von 30° auf 87°, resultiert in einer glatten und defektfreien Schicht, deren Transparenz zwischen dem Nanodraht und den, Supraleiter erhöht ist. Am Ende wurde diese Technologie verwendet, um das Wachstum von komplexen Nanodraht-Netzwerken und mehrfachen Josephson-Kontakten zu demonstrieren.

# 1 Introduction

If there's anything radical that could revolutionize the world, that nonetheless is a quantum computer. It could transform various fields, the quantum impact possibilities are limitless [1].Quantum computation is one of the trending topics in the research community and many top companies [2–5]. These companies are using semiconductors, superconducting qubits, etc to make qubits. Quantum computers, use quantum physics to interpret and compute. They can exceedingly outperform supercomputers at certain tasks [6]. Widely known classical computers encode information in the form of 'bits' that are 0s or 1s. Whereas, a quantum computer uses qubits also known as quantum bits. A quantum computer uses two states likewise its classical counterpart. These two states are rather called as energy states and not as in a 'on' and 'off' configuration. In contrast to classical computers, additionally a quantum computer can also be in the superposition of states i.e. energy levels.

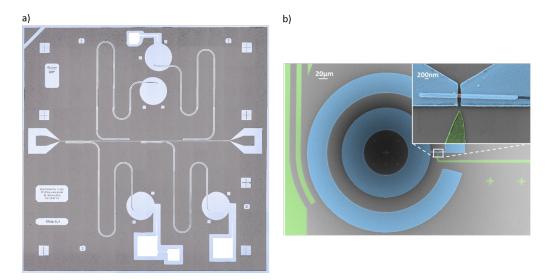

The current major drawbacks of a quantum computer are noise and decoherence [7], also scalability w.r.t to qubits. Decoherence can be caused by light, vibrations, or by the inevitable act of measuring a qubit. Decoherence causes the instability in a qubit's position, thus disturbing a qubit's state of superposition or entanglement. There is a high need for a robust system. An example of such a robust qubit is a superconducting qubit, which is a collective excitation in a superconducting circuit. These superconducting qubits are popular approaches for large-scale quantum computation, since they are highly controllable and sensitive to charge noises [8]. One such qubit is a transmon qubit i.e. superconducting charge qubit, which is specifically designed to have a reduced sensitivity to charge noise [9–11]. A transmon qubit, that can be controlled by a gate is called a gatemon, where in the Josephson junction is controlled by a gate, as seen in Fig. 1. III-V semiconductor nanowires (NW) combined with superconducting

Figure 1: a) A transmon qubit circuit with resonators, gates and feed lines. b) closeup of the resonator (from the transmon qubit circuit) with a Josephson junction on semiconductor nanowire in the inset (designed at RIKEN).

electrodes have proven to serve as versatile building blocks of Josephson junctions [12]. These Josephson junctions are formed by two separated superconducting electrodes that are connected by a NW segment. This NW segment, is the semiconductor part that can be tuned via

a gate electrode to control the critical current of the junction. Furthermore, due to the large Fermi wavelength of the electrons (that are present in the semiconductor part), and limited diameter of the NW, a finite number of discreet Andreev bound states are formed in this Josephson junction. The Josephson current is mainly carried by these bound states. There are coherent transitions present in these states that can be used for qubit operations [13–15]. These SNS (superconductor-semiconductor-superconductor) junctions have also found their place in the topological qubit regime that are based on Majorana fermions [16–20].

InAs and InSb nanowires are well suited candidates to form a Josephson junctions, because of their high transparency towards the deposited superconducting electrodes, which is one of the prerequisites to obtain a sufficiently large supercurrent [21, 22]. A commonly used material is aluminium, since it possesses a small superconductive gap and critical magnetic field, but has a large superconducting coherence length [18, 22, 23]. In particular, when a larger operation temperature is required or the junctions have to be operated at a higher magnetic field, other superconductors such as Nb and its alloys [24-26], Pb [27, 28], or V [29, 30], are the materials of choice. It was already established that a semiconductor NW can be covered in-situ by a superconducting layer [26, 30–32]. SC/SM (superconductor/semiconductor) hybrids in this regard, have always been fascinating and the research has greatly paced to realize these Josephson junctions in-situ at ultra-high vacuum (UHV), without any exposure to chemicals or ambient surroundings. Normally to form a Josephson junction with a small gap between the insitu deposited superconducting electrodes, wet-chemical etching is employed. However, there have been several reports to achieve short Josephson junctions, by adopting different shadow evaporation techniques, i.e. either by using a NW to cross another as shadow masks [33, 34] or by using a patterned, suspended  $SiO_2$  layer as a stencil mask [26, 30]. In this thesis, different approaches to realize a Josephson junctions using molecular beam epitaxy (MBE) technique are presented, which have proven to be highly promising elements for superconducting qubits.

# 1.1 Scope Of This Work

This thesis involves in optimization of bottom-up growth of NWs using an MBE technique, and implementation of the MBE technique to produce highly transparent superconducting contacts onto semiconductors. The entire work benefited from the state-of-the-art Nanocluster at Helmholtz Nano Facility (HNF), combining several deposition chambers maintained at UHV conditions. The outline of this thesis is as follows:

- Chapter 1 This chapter gives brief insights into the essential theory of growth, metal shell growth and physics behind fusing a semiconductor and a superconductor.

- Chapter 2 This chapter explains about the characterization tools that have been used throughout the thesis.

- Chapter 3 This chapter describes the different fabrication steps of the samples, that have been used in this thesis.

- Chapter 4 The optimized results of the substrate fabrication methods are presented in this chapter.

- Chapter 5 This chapter illustrates the results of the growth and characterization of undoped InAs and Te doped InAs nanowires.

- Chapter 6 The results of the growth and characterization of InAs/Al half-shell nanowires with ex-situ etched junction is presented in this chapter.

- Chapter 7 This chapter presents the most novel approach to achieve a Josephson junction device in-situ, with the supporting transmission electron microscopy and low temperature electrical measurements.

- Chapter 8 The summary and the outlook has been presented in this section.

# 2 Theory

In this chapter, general theory related to the growth of layers is explained in the thin films section. Gathering the basic understanding from this, the nanowire growth is explained. Furthermore, the growth of superconducting metal shells on the nanowires using MBE at UHV conditions is discussed. Finally, to understand the importance of the semiconductor/superconductor interfaces, the basic transport mechanisms are presented via superconductivity, Josephson effect, and superconductor-normal conductor-superconductor (SNS) junctions.

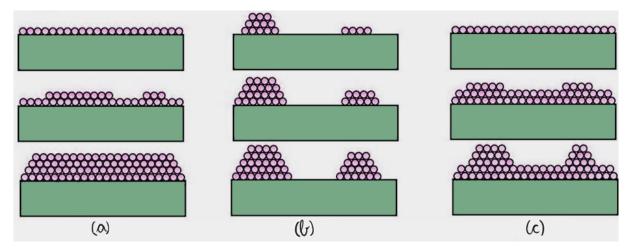

## 2.1 Growth Of Thin Films

Josephson junctions with the semiconductor nanowires form a crucial part of a superconducting qubit circuit. These nanowires have to be crystalline. This increases the transparency of the semiconductors and the superconductors, by allowing sufficient current through the semiconductor. Although the growth of nanowires is different than a layer growth, the experimental realization of the different growth modes, helps one understand the mechanism of layer growth which is quite comparable to that of the metal growth of superconductors. The growth of crystalline materials involves a variety of parameters, such as substrate temperature, fluxes of the materials, III-V ratio, etc., that need to be optimized. Some of them include growth direction, composition, disorders, etc. To obtain a high crystalline quality of the materials, MBE growth technique is adopted. Furthermore, to understand the basic mechanism of crystalline growth, a basic understanding of the growth modes is necessary. When a layer is grown onto a desired substrate, it can adopt three different growth modes i.e. Frank-van der Merwe (FM), Volmer-Weber (VW), and Stranski-Krastanov (SK) modes. These modes are schematically shown in Fig. 2. The distinguishing factor amidst the modes, depends on parameters namely, lattice mismatch between the materials, the adatom diffusion length, the adhesion energy, the flux J and the substrate temperature. In Volmer–Weber (VW) growth, the adatom-adatom interaction dominates, this leads to the formation of the islands. As more adatoms reach the substrate, they coagulate on the previous islands and coarsen. This causes rough multi-layers on the substrate. This usually occurs when the lattice mismatch is moderate, and the critical thickness,  $h_c$ , value is lower than a monolayer, thus favours island growth. In the Frank-van der Merwe (FM) growth regime, the interaction between the adatoms and the surface dominates, thus leads to a layer-by-layer growth [35]. The film formed here is smooth and complete. This indicates that a new layer forms after a complete layer is formed below it. Hence, occurs when the lattice mismatch between the grown layer and the substrate is small. Here, the layer thickness is below  $h_c$ , thus the strain could be relaxed elastically [36]. Stranski-Krastanov growth regime is an intermediate process that consists of both islands and layers. This occurs in the case of highly mismatched systems. The transition of the layer growth to the island growth depends on the key parameter called critical layer thickness  $h_c$ . This is the thickness of a wetting layer, where it starts to form an island. This critical thickness parameter depends on the surface energies and the lattice misfit parameters of the substrate and the film. Additionally, strain energy increases as the wetting layer thickens, and this could lead to misfit dislocations [37]. The misfit between the layers, can be expressed in terms of the lattice constant of the substrate  $a_s$  and the lattice constant of the desired material to be grown  $a_f$ , as shown in the equation below:

$$\frac{\delta a}{a} = \frac{a_f - a_s}{a_s}. (2.1)$$

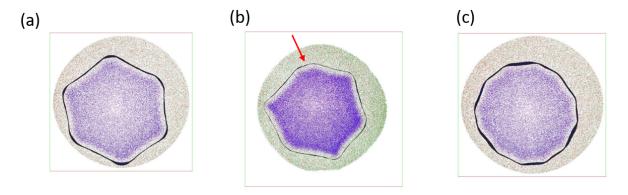

Figure 2: Growth modes of thin films (a) Frank-van der Merwe (b) Volmer-Weber, and (c) Stranski-Krastanov. Image adapted from [38].

This gives a good understanding of different growth regimes and the mechanism behind layer growth. It is also comparable to metal film growth which will be further discussed in the superconductors section. Besides this, nanowire growth is quite different to layer growth, since nanowires have a large surface to diameter ratio.

#### 2.1.1 Nanowires

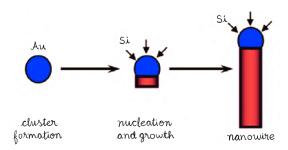

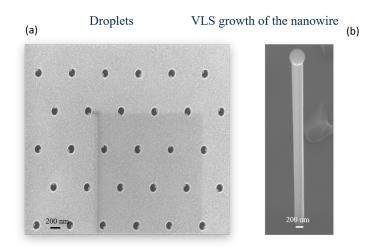

Nanowires in general have a very high aspect ratio. When they are manipulated via field effect from a gate electrode, the conduction channels can be controlled. This is a desirable quality for fast switching applications. Nanowires are considered to host one-dimensional states due to quantum confinement, which reflects in the efficient charge transport and interesting quantum effects. They can be grown via top-down or bottom-up methods. The first growth of 1D structures by self-assembly in 1964 has been reported by Wagner and Ellis [39], where they used liquid gold droplets on Si substrate to grow Si nanowires. Here, the gold droplets are employed as a catalyst, and the nanowires eventually grew when the droplets are supersaturated and supplied with gaseous Si. Thus, the supersaturation led to the growth of the nanowires between the substrate and the gold droplet. This process was known as vapor-liquid-solid (VLS) growth mechanism. This process has been expanded and restored in early 90's by Hiruma et al. [40, 41] for the growth of III-V nanowires such as GaAs and InAs. These works highlighted the metalorganic vapor phase epitaxy (MOVPE) methods of growth. Henceforth, several other growth methods have come into light, namely, chemical beam epitaxy (CBE), and MBE. Different materials from the groups (IV, III-V, II-VI) have been adopted to grow nanowires using these growth techniques. Apart from gold, also Ag [42], Cu [43], Mo/Au [44] have been utilized as catalysts to grow nanowires.

A typical VLS growth process is schematically illustrated in Fig. 3. Metal nanoparticles are used as a catalyst to grow nanowires. During the growth process, the catalyst is heated above

its eutectic temperature. This creates a liquid metal—semiconductor alloy [45]. When a desired vapour source (NW material) is provided, the eutectic alloy continues to incorporate the semiconductor material via supersaturation, through the vapor/liquid interface. This causes nucleation as more and more of the vapour arrives. Thus, the semiconductor material precipitates and creates a solid/liquid interface (growth interface). Eventually, nanowire growth is achieved. This is followed by solid addition (formation of NW) at the growth interface, thus VLS mechanism. In this process, the metal catalyst, precipitates and a nanowire, thus is formed between the droplet and the substrate. Hence, the metal droplet stays on the tip of the nanowire as the nanowire elongates [45].

**Figure 3:** Schematic of VLS growth of silicon nanowires. Gold is used as a metal catalyst, a liquid alloy droplet of AuSi (orange) is initially formed when heated above 363°C. Continuous supply of vapour materials results in nucleation. Thus, the nanowire (green) grows uniaxially. Image adapted from [45].

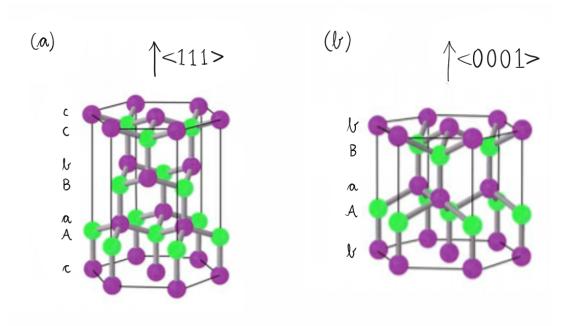

Contradictingly, using an external catalyst such as gold, often influences the opto-electronic properties of the nanowires. Gold is widely known to diffuse into materials and can be quite detrimental for CMOS fabrication platforms. It causes deep level traps and causes diffusion, and in turn degrades and effects the efficiency of the electronic devices [46, 47]. Hence, alternative methods have been investigated. One such method is a self-catalyst method to grow III-V nanowires using group III element as a catalyst. Here, the axial growth of the nanowire proceeds with saturation of the droplet of group III element with group V. This method is popularly used to grow GaAs nanowires [48]. Here, the nanowires are grown selectively, and the group III droplets are made to form on the holes patterned on Si substrates covered with SiO<sub>2</sub>, as a mask. The nanowires grown on these substrates are distributed uniformly on the substrate. The nanowires tend to have different growth rates for the top and the side facets in this case. For the investigations performed in this thesis we have grown InAs nanowires using vapour solid (VS) growth mode. InAs is chosen since it is a widely known, III-V semiconductor and has a very high electron mobility  $\approx 3.4 \times 10^4 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  at room temperature [49]. A VS growth mechanism is adopted since, in contrast to the VLS mechanism, a droplet is not involved during the nanowire growth. This makes it easy to incorporate dopants and growth of ternary structures. There have been only few reports that have demonstrated VS grown methods [50, 51]. Solid conclusions regarding the exact VS growth mechanism have not been made. Hence it is not clearly known if the initial phase of VS growth mode, is dominated by VLS mechanism and further by VS mechanism or by simultaneously saturation of both elements. In-situ growth studies of VS growth mechanism would shed light on this topic, which is lacking currently. Independent of different growth methods, a high occurrence of stacking faults in these nanowires is observed that degrades the electronic transport and optical efficiency [52, 53].

**Figure 4**: Atomic arrangement of Zinc Blende (ZB) (a) and Wurtzite (WZ) (b) structures along the [111] and [0001] nanowire growth directions. Image adapted from [54].

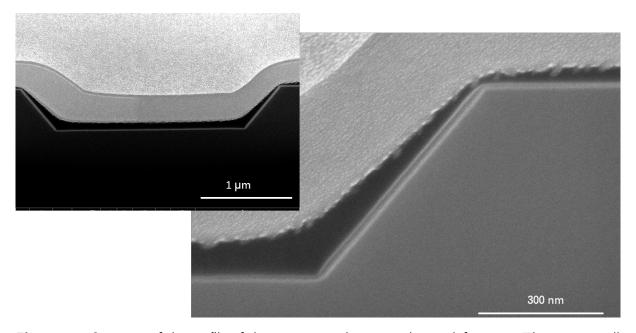

## 2.2 Growth Of Superconductive Thin Films

The Josephson junctions prepared for this thesis are based on InAs nanowires/superconductor. The nanowires for this purpose, are initially degassed and a thin superconducting metal shell is evaporated onto these preferably at UHV conditions. In the previous section, the nanowire growth mechanism is already elucidated. This section entirely is based on the growth kinetics of the superconductor metal shell. The superconductor metal film should cover the nanowire conformally. Keeping this concept in mind, evaporation of Al and Nb metals have been performed onto the InAs nanowires that are grown on Si (111) substrates, at UHV conditions. The Al and the Nb shells evaporated here, are half shells that are formed, when the substrate is not rotated during the process. In 2015 a growth model was developed by Peter Krogstrup, that explains the kinetics and the growth of the thin Al films, Suppl. [31]. One of the essential components of a superconducting metal shell is the adatom diffusion length  $\lambda_a$ . This is the mean distance of the adatom, when it lands on the surface and moves along and gets incorporated into the growth of the film. When this movement is assumed as a random walk and the adatom incorporation barrier is considered neglected, from Krogstrup *et al.* [31] the average diffusion length can be defined as:

$$\lambda_a(\rho_a, T_s) \propto \frac{1}{\sqrt{\rho_a}} \cdot \exp^{-\left(\frac{\delta h_{aa} - \delta \mu_M}{2k_B T_s}\right)},$$

(2.2)

where,  $\rho_a$  is the adatom concentration,  $\delta\mu_M$  is the chemical potential of the incorporation site,  $\delta h_{aa}$  is the transition state enthalphy barrier between two nearest adatom sites,  $k_B$  is the Boltzmann constant and finally the substrate temperature is  $T_s$ . It is also know that, when the flux J increases, the adatom concentration  $\rho_a$  on the substrate also increases, that gives rise to

$$J \propto \rho_a$$

. (2.3)

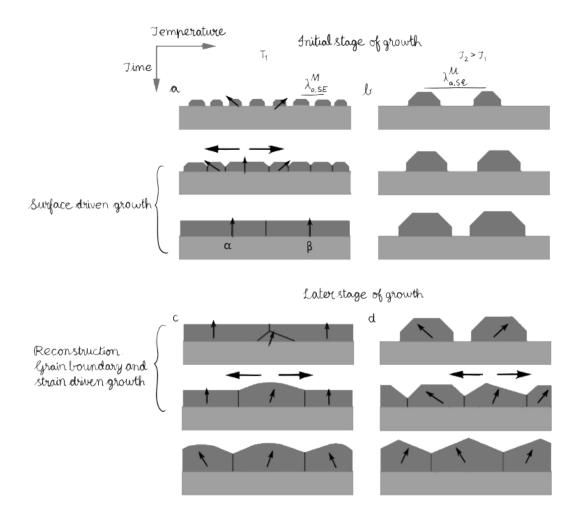

Considering Eq.(2.2) and Eq.(2.3), it can be deduced that the adatom length decreases, as the flux J increases and the substrate temperature  $T_s$  decreases. When the diffusion length  $\lambda_a$  is small, it results in a small and grainy metal films. Since Al has a FCC i.e. face-centered cubic structure, the adatoms merge into grains and crystallize in [111] crystal direction, which is out-of-plane [57]. The [111] crystal direction, is a quite preferential orientation for grains with lowest surface energy, since it reduces the total energy. This growth regime, where the total surface energy is minimized is called surface driven growth. Considering an in-plane orientation, this occurs to minimize the interface energy as seen, in Fig. 5 (a). This appears until a certain critical thickness and can also vary with different metals.

When the substrate temperature  $T_S$  increases the diffusion length of the adatom increases, the grains become spacey and clump together to form bigger clusters, as seen in Fig. 5 (b). When the critical thickness of the grains increase, the growth is dominated by by strain fields and grain boundaries, rather than surface energy minimization, as shown in Figs. 5 (c) and (d). This causes grains with different crystal orientations and the metal film formed here is grainy rather than smooth. It is a prerequisite, to consider the lattice mismatch for the metal that are to be evaporated, so as to reduce the disorders at the interface. In case of a large mismatch of the semiconductor and the superconductor metal, interfacial domains form to decrease the stress caused due to lattice mismatch [58]. For thinner layers, it is known that,

**Figure 5**: Initial stages of metal shell (blue) growth on InAs surface at high  $(T_2)$  and low temperature  $(T_1)$  is illustrated. (a) Shows a case of  $T_1$ , where small grains form due to low adatom diffusion, then they later merge into a thin film. If the thin film is below a critical thickness, the grains with the lowest surface energy dominate (arrows). (b) Shows a scenario of higher temperature where in the adatom diffusion is higher, that results in larger grains, that are spaced further apart than in scenario (a) (c) and, (d) Represent the cases in which the critical thickness is exceeded. In both temperature regimes, they result in new crystal orientations, w.r.t to the grain boundaries and strain disorder, since these contribute more, when the layers are sufficiently thick, image adapted from (Suppl. [31]).

surface energy minimization dominates. Since the surface-to-volume ratio for thinner layers is high. Aluminium forms a complete and conformal layer and the grains are oriented out-of-plane along the [111] direction as depicted in Fig. 5 (a). For thicker layers, [11 $\bar{2}$ ] is the preferred orientation, since it is driven by strain reduction [31]. This is attained by reconstruction or relaxation into less mismatched grains, i.e. from [111] to [11 $\bar{2}$ ], as illustrated in Figs. 5 (c) - (d).

# 2.3 Superconductivity

This section deals with the evaporated metals such as Al/Nb and their behaviour at ultra low temperatures, where they exhibit superconductivity. Furthermore, this concept is extended to understand Josephson junctions that are designed using semiconductors (InAs nanowires) and superconductors (Al/Nb). In such Josephson junctions, the semiconductor induce superconductivity from the metals at low temperatures. To explain this whole phenomenon of Josephson junctions, it is essential to initially understand, the basics of superconductivity. Superconductivity was first discovered by Kammerlingh Onnes [59] in 1908 in Leiden, when they dipped Mercury into liquefied helium at 4.2 K. The electrical resistance of mercury drastically dropped and vanished at this temperature, the corresponding phenomenon was named superconductivity. This has gathered a huge attraction and since then various fields in physics and technology have been revolutionized. This further has lead to discovery of many superconducting materials [60]. Another crucial effect that also has been observed in conjunction to the electrical resistance drop in a superconductor is that, when a magnetic field is passed through this superconductor at lower temperatures, it generates its own screening field, that expels the magnetic field, this was coined as diamagnetism. Superconductors are perfect diamagnets at lower temperatures. Although the experiments have been laid down, the theory behind the superconductivity has been formulated much later than the discovery of the superconductivity itself. It has fascinated a pool of scientists and it took several years until BCS theory explained it using many-body physics. It was John Bardeen, Leon Cooper, and John Robert Schrieffer, who modelled it, hence the name [61]. The theory demonstrates that superconductivity is a quantum mechanical state of matter that exhibits zero resistance and perfect diamagnetism. This state is caused due to the electron-electron attraction at very low temperatures. This attraction is mediated via a phonon exchange, thus causing electron-phonon interaction. Hence, Cooper pairs propagate through the material, causing no dissipation, thus electrical resistance drops towards zero. A Cooper pair is a state of two electrons that are weakly bound and can be defined using a wave function. These bound states occupy the same energy state and condensate to form a Bose-Einstein condensate. The two electrons in such a condensate have opposite momenta and form a spin singlet, hence their centre of mass is stable. This superconducting state can be disturbed via several thermodynamic parameters, such as temperature, field, and current. These thermodynamic properties can influence the macroscopic behaviour of the superconductor. Thus, the superconducting state is vanished when there is an increase in temperature, magnetic field, or current [62–64] above a critical value. As mentioned above, since the electrons form a condensate, this many-body interaction can be defined by a macroscopic phase coherent state, that is stated in the equation below:

$$\Psi = \sqrt{n_s} e^{i\phi}. (2.4)$$

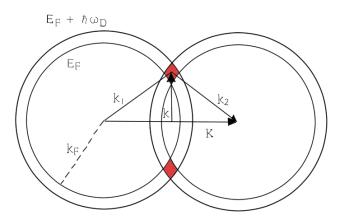

Since all Cooper pairs are in the same quantum mechanical state, this equation describes the state of an entire macroscopic superconductor. Here,  $\phi$  is a single phase and  $\sqrt{n_s}$  is the single amplitude. Considering the BCS theory, it explains that an electron moving through the crystal lattice, in a state  $k_1$  interacts with the other lattice ions in its proximity through Coulomb interaction and acquires a new energy state, lower than its previous state i.e.  $k_1$  -  $\delta k$ , releasing a phonon. The Cooper pair has the momentum  $\hbar k$ . Consequently, the released phonon is potentially absorbed by a different electron in the lattice, that is at state  $k_2$ , which excites its energy state to  $k_2 + \delta k$ . While lapped region of the two Fermi spheres, can be seen in Fig. 6, it results in a formation of a Cooper pair. The first electron in the state  $k_1$ , attract the near by lattice ions, causes a positive fluctuation in the charge density causing it to

attract the second electron. This interaction via the phonon is the implied electron-electron interaction, which is also depicted in the above Fig. 6. Electrons could pair up using the phonon interaction over larger distances to form Cooper pairs. They do not necessarily, pair up with a nearby electron. Rather, the electron-electron interaction could extend over almost several hundred nanometers, in the range of the coherence lengths [61, 65–67].

**Figure 6**: Overlapping Fermi spheres for two interacting electrons in the formation of a Cooper pair.  $\vec{k}$  points in the overlapped (shaded area). Image adapted from [68].

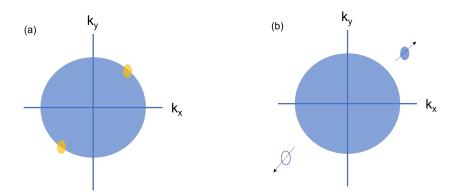

The superconductor consists of a BCS ground state where Cooper pairs are occupied, and below this is the Bogoliubov quasi-particle state. This gap  $\Delta_0$  is created to protect the BCS ground state. Even though the electron electron interaction is considered to be weak, the energy needed to break up a Cooper pair is twice the energy difference between quasi-particle state energy E and BCS ground state  $\Delta_0$ . This excited state is known as Bogoliubov quasi-particle state, that is a result of an elementary excitation above a superconducting state, and can be seen in Fig. 7. The Bogoliubov quasi particle is a superposition of an electron and a hole, with opposite spin and momenta.

**Figure 7**: (a) Electrons (yellow) in a Fermi sphere, have opposite momenta and spin describe a Cooper pair in a superconducting state. (b) An elementary excitation above the Fermi sphere, results in quasi-particle that is a superposition of a hole and an electron. They have opposite spin and momenta and are called Bogoliubov quasi-particles (blue and white).

The quasiparticle energy E is determined using the Bogoliubov-de Gennes eigenvalue equation:

$$\begin{bmatrix} H(r) & \Delta_r \\ \Delta^*(r) & -H(r) \end{bmatrix} \begin{bmatrix} u_k(r) \\ v_k(r) \end{bmatrix} = E \begin{bmatrix} u_k(r) \\ v_k(r) \end{bmatrix}.$$

(2.5)

Here,  $\Delta(r)$  is the coupling energy, while  $u_k$  and  $v_k$  are electron- or hole-like quasiparticles, H(r) is the Hamilton operator for a single particle. This can also be expressed as

$$H(r) = \frac{-\hbar^2}{2} \frac{1}{m^*} \nabla^2 + V(r) - \mu, \tag{2.6}$$

where  $\mu$  is the chemical potential and V(r) is a scalar potential [69]. In case of metals,  $m^*$  can be equated to  $m_e$ . Thus the eigenvalue E of the Bogoliubov-de Gennes equation is

$$E = \pm \sqrt{\left(\frac{\hbar^2 k^2}{2m_e} - \mu\right)^2 + \triangle_0^* \triangle_0}.$$

(2.7)

This equation represents that there exists a gap between excited state and the ground state and this gap of a superconductor does not host any single-particles. As for the energy required to break the Cooper pair, once has to surpass the superconducting gap.

## 2.4 Josephson Effect

The devices fabricated for this thesis are made of of Al/Nb superconductors separated by few tens of nm of InAs nanowire. This constitutes a Josephson junction, i.e. superconductor-normal conductor-superconductor (SNS) junction. To understand the Josephson effect the concepts are briefly summarized below.

The phenomenon of flow of Josephson current between two distinct and disconnected pieces of superconductors is called the Josephson effect, was discovered by Brian D. Josephson in 1962 [70]. This is a phase-coherent process, that has been formulated for the SIS (superconductor-insulator-superconductor) junction, wherein the weak-link is a thin insulating barrier. The Cooper pairs tunnel through the barrier from one superconducting segment to the other. However, the weak-link chosen in our case is the semiconductor nanowire and thus the Josephson junction in our case, could be approximated to a superconductor-normal conductor-superconductor device, also known as the SNS Josephson junction device.

When a DC current is applied to this SNS device, Cooper pairs travel through the weak-link from one side to another through proximity effect. The superconductor wave function, on either sides decays into the weak-link.

Considering the Cooper pair wave functions

$$\Psi_1 = \sqrt{\rho_1} e^{i\phi_1} \text{ and } \Psi_2 = \sqrt{\rho_2} e^{i\phi_2},$$

(2.8)

where,  $\rho_1$  and  $\rho_2$  are the Cooper pair densities on either side of the junction and the  $\phi_1$  and  $\phi_2$  are the corresponding phases. The electrons in a Cooper pair have to have the similar center of mass. This can be satisfied by making the Cooper pairs phase-coherent all along the superconductor. Hence,  $\phi_1$  and  $\phi_2$  represent the Cooper pairs in the superconductor section and simultaneously  $\Psi_1$  and  $\Psi_2$  can be substituted in the Schrödinger equation, that results in two Josephson equations. The Josephson current is related to the difference in the phase between the left and the right parts of the weak-link

$$\phi = \phi_1 - \phi_2,\tag{2.9}$$

and the first Josephson equation for the current is

$$I(\phi) = I_c \sin(\phi), \tag{2.10}$$

$I(\phi)$  maxes out at critical current  $I_c$ , and additionally the phase difference  $\phi$  can be varied according to the current I flowing through the junction. This means that an increase in I results in the increase of the phase  $\phi$  and a corresponding decrease of the coupling energy  $E_c$

$$E_c(\phi) = -\frac{\hbar}{2e} I_c \cos(\phi). \tag{2.11}$$

The systems behaves as a single superconductor in the presence of an infinitely thin barrier, which phases out  $\phi_1$  and  $\phi_1$  [67]. The coupled Schrödinger equations with ansatz from 2.8, gives

$$V(t) = \frac{\hbar}{2e} \frac{\partial \phi}{\partial t}.$$

(2.12)

It is deduced that the Josephson voltage depends on the time-derivative of the phase difference  $(\phi)$ . These equations (2.10) and (2.12), characterize the Josephson effect.

## 2.4.1 Proximity Effect And Andreev Reflections

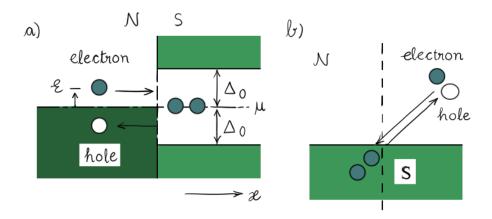

This section deals with the physics of fusing a superconductor to a normal conductor, that is a basis of an SNS Josephson junction. When a non-superconductor is bought in close proximity within a superconductor, Cooper pairs travel from the superconductor (S) into the normal conductor (N) known as proximity effect. The semiconductor then partly turns into a superconductor, this is known as induced superconductivity. This means that the wave function of a superconductor decays through the non-superconductor, and this decay depends on the coherence length of the non-superconductor. This proximity effect would be ideal if the interface between S and N has a high transparency. Thus, the interface between the InAs nanowire and superconductors (Al/Nb) has to be clean for the effective proximitization of the NS. Any impurity at the interface, decreases the coherence lengths and thus diminishes the effect. InAs nanowires in general are known readily be proximitized if there exists a transparent interface between S and N [22]. Thus there have been several attempts to improve the interface between the InAs nanowire and the superconductors (AI/Nb) in this thesis. As for the SNS Josephson junctions, the Josephson current is known to flow through the superconducting segments without any dissipation [62, 63, 69] at zero bias. It is assumed that the superconductor and the normal conductor have the same Fermi-energy and electron densities. Here, interaction between the bound Cooper pairs in the superconductors and free electrons in the normal conductors are explained. This is known as a reflection process at the boundaries of the materials (S and N) and was introduced by Alexander F. Andreev in 1962 [71]. The process was named after him and called the Andreev reflection. To make the process simpler, it is assumed that the electron gas in the normal conductor grazes with the superconductor without any additional barriers that could cause normal reflections at the interface at zero bias. The Andreev reflection process is depicted in Fig. 8.

When a conducting electron with energy  $E_F < E_e < \triangle_0$ , travels from a normal metal into a superconductor, as see in Fig. 8 (a), there happens to be no corresponding energy state within  $\triangle_0$ . Hence it needs to pair up to travel through the superconducting regime. Thus, it pairs with another electron from the Fermi sea of the normal conductor [69]. This results in a hole in the Fermi sea, that the paired-up electron created. Accordingly, to conserve the momentum this hole with the charge +e is retro-reflected, as seen in Fig. 8(b), and travels back in the opposite direction of the incident electron, and into the normal conductor. This

**Figure 8**: a) Energy diagram of the Andreev reflection process b) Scattering process in the real space. Image taken adapted from [69].

process could also occur in the reverse way, when the Cooper pair in the superconductor, drives through the normal conductor. The paired-up electrons redeem themselves in the channel of the normal conductor. One of the electron goes into the normal conductor channel and the other combines with a hole of the Fermi sea of the normal conductor.

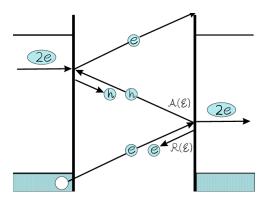

**Figure 9:** Multiple Andreev reflections, that are caused between two superconductors in a close proximity of a non-superconductor. A charge transfer of -2e per cycle, can be observed. Image adapted from [72].

In case of a superconductor-normal conductor-superconductor (SNS) junction, Andreev reflections take place at both S/N interfaces. An incident Cooper pair from the superconducting region reaches the interface to a normal conductor and dismantles itself into two electrons, wherein one of the electron is absorbed by a hole. The other electron travels through the normal conductor and sees the second interface. Here it needs to pair up again to enter the superconducting region thus, it pairs up with an another electron and retro-reflects a hole. This hole is reflected back through the normal conductor and engages in the same process near the first interface. This process is known as multiple Andreev reflections and occurs with a bias. This causes a simultaneous electron and hole transfer through the normal conductor Fermi sea, can be seen in Fig. 9. Thus creates a charge of -2e per cycle [69]. Each Andreev reflection process is a phase coherent process. Additionally, energy and momentum are also conserved in this process [69]. Hence, when an interface between S/N is quite transparent, multiple Andreev reflections are observed in the junction area and can be seen as subharmonic

peaks in a differential resistance graph, deduced from the low temperature electrical measurements. Hence, there were several approaches undertaken in this thesis to increase transparency between the InAs nanowires and AI/Nb superconductors, to observe these quantum effects.

# 3 Experimental And Characterization Techniques

In this chapter, the experimental tools for the nanowire (NW) crystal growth and the other characterization techniques are illustrated.

## 3.1 Growth Techniques

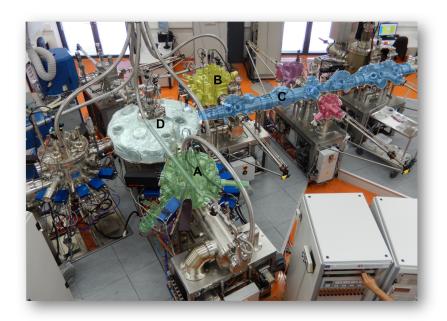

The sample growth by MBE, during the course of this thesis was performed at the Nanocluster at Helmholtz Nano Facility (HNF). This is one of the world-class, state-of-the-art clusters built by Scienta Omicron GmbH. It is a UHV tool combining 10 deposition chambers that are group III-As MBE, group III-As/Sb MBE, ALD, metal MBE, phase-change MBE, an oxide sputter chamber, a metal sputter chamber and a metal oxide MBE. This classic built grants a huge possibility to investigate a lot of material combinations within the UHV conditions. In this thesis, the MBE technique is adopted to grow NWs and then a metal layer, is evaporated by an electron beam (e-beam) maintaining ulta high vacuum (UHV) conditions.

#### 3.1.1 Molecular Beam Epitaxy

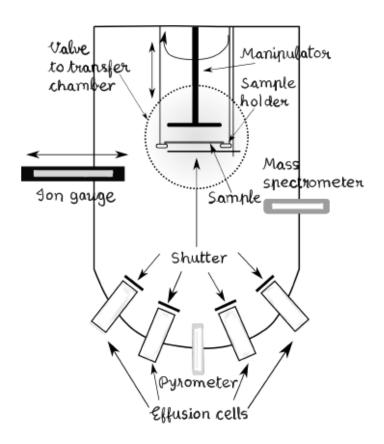

Epitaxy is a process of growing crystalline materials on a crystalline substrate. The high purity of the source materials together with the UHV conditions results in a extremely good quality of the grown layers. With this technique, growth of atomic layers is possible at relatively low growth rates i.e. less than 1  $\mu$ m/hr. This empowers a greater control on the crystal structures. To achieve a high quality of epitaxial layers, it can only be grown at pressures below  $\approx 1 \times 10^{-9}$  Torr. To achieve these low pressure, the chamber is pumped using a cryo pump, an ion getter pump and additionally a cryo shield. The cryo shield acts as a pump and also as a thermal isolation between the effusion cells. Two MBE systems have been used, during the course of this thesis. The first one, MBE A, which is equipped with one As and one Sb cracker and additionally Ga, In and Al effusion cells. Furthermore, Si, C, and GaTe are the dopant cells. MBE A is used to grow InAs nanowires, where the planar growth rates are optimized on GaAs(100) substrates. MBE B is a metal MBE where the materials Al, Nb, Pt, Ti, and AlO $_x$  are used for deposition. Both MBE A and MBE B are connected to each other via a large UHV transfer line. MBE A was used for the growth of the InAs NWs, where in the planar growth rates are tested on GaAs (100) substrates. This is then optimized to the nanowire growth rates. As and Sb fluxes are measured in beam equivalent pressures (BEP). Figure 10 shows an overview of a part of the Nanocluster. MBE Chamber (A), used for NW growth is coloured green. The round transfer chamber marked silver (D), contains a robotic arm, which distributes the samples to the different chambers. The actual transfer is depicted in blue (c). Here, a small train is used to transport the substrates to any desired chamber. Chamber MBE B (B) is coloured yellow, here the metal deposition takes place. The preparation chamber is used for degasing the samples is coloured in purple. The samples are transferred to the load-lock, and is coloured in red.

In chamber A MBE (schematic can be seen in Fig. 11), the effusion cells have a crucible containing the deposition material and is heated up via a filament until a desired pressure is reached. These crucibles contain group III elements and dopants. There are shutters, placed in front of these cells to open and close them. Cell temperature defines the amount of materials that comes onto the sample. Arsenic is supplied via a valved cracker source and the amount of

**Figure 10:** An overview of a part of the Nanocluster. Chamber MBE (A) in green, Chamber MBE B (B) in yellow, transfer line (C) in blue, round transfer chamber (D) in silver.

Figure 11: Schematic illustration of MBE chamber A. Image adapted from [73].

arsenic is controlled by the valve position and the reservoir temperature of the As cracker cell. The BEP (beam equivalent pressure) of As flux, is determined by the ion gauge. This whole

system is maintained at UHV (ultra high vacuum) conditions to obtain large mean free path of atoms. UHV is achieved by using a combination of cryo, ion getter pump and a cryopanel. The cryopanel condenses the residual gases, thus acts like a pump. For a III-V system growth, group III flux determines the growth rate, where as group V is just supplied in excess. The growth rate is further measured using RHEED (reflection high energy electron diffraction). In the MBE growth the interface abruptness is on an atomic level and the dopant inclusions can be controlled precisely, thus giving rise to high quality layers.

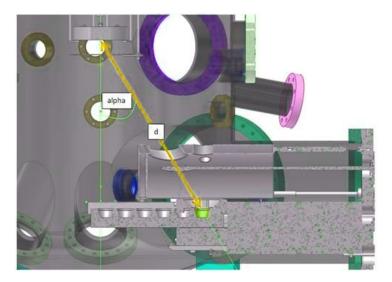

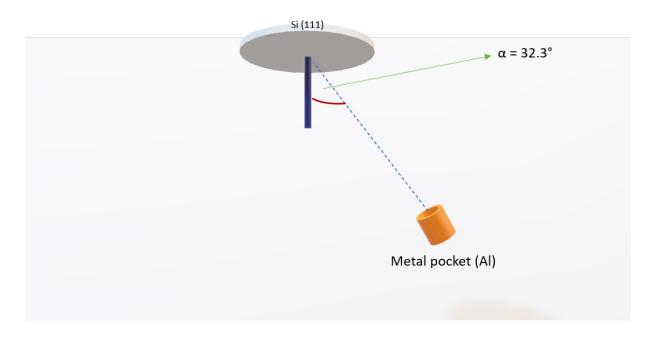

All metal depositions took place at chamber B, which is a metal MBE, as seen in Fig. 12. In the metal MBE chamber B, electron beam evaporators were used for deposition. Here, an electron beam hits a firm ingot of the evaporation substance which is placed in a crucible. This melts the ingot and leads to an evaporation of the material, can be seen in the schematic of Fig. 12. Thus, the flux J is controlled by the electron beam current and not by the temperature of the filament. The flux of the electron beam evaporators can be controlled via a residual gas analyzer feedback loop (RGA-loop). Here, a mass spectrometer detects the amount of evaporated material and uses this information to adjust the electron beam current to stabilize the targeted flux. The substrate is fastened by the substrate holder which also serves to heat and rotate the sample during growth. The desired materials are filled into the pockets and these are shifted to the gold position (see schematic Fig. 12), so the angle of deposition w.r.t substrate normal,  $\alpha$  i.e. 32.3 ° always remains constant. Only one material at once can be evaporated, hence the desired material has to be shifted to the position of the gold pocket.

Figure 12: Schematic illustration of the metal MBE deposition system with pockets, gold pocket for the desired metal usage. Image provided Benjamin Bennemann.

## 3.2 Analysis Techniques

## 3.2.1 Scanning Electron Microscopy

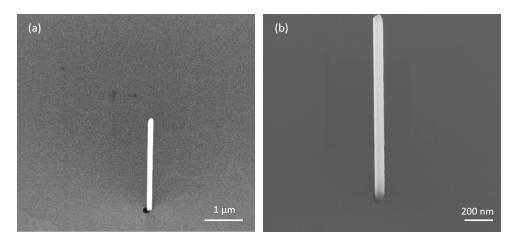

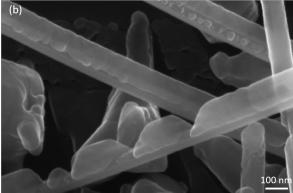

In the field of NW research, the first and the foremost feedback technique used is the scanning electron microscopy (SEM). This is used to determine the yield, the aspect ratio and the surface morphology of the NWs. This work began with the optimization of substrate preparation for selective area epitaxy (SAE) of InAs NW arrays. A detailed study with the help scanning electron microscopy (SEM) was carried out to make this process reproducible. For this purpose a Zeiss 1550 VP Scanning Electron Microscope was used as an non-invasive analysis of the grown NWs and other structures. The SEM uses a focused beam of electrons to produce a high resolution image of the sample, allowing resolutions as small as 0.8 nm. The NW growth samples were imaged at a working distances less than 2 mm when viewing from the top, and when rotated at 30° with respect to the electron beam gun the working distances was always kept less than 6 mm. The samples for viewing the NWs are imaged with the accelerating voltages of 15-20 keV. Additionally, when the nanostructures have to be imaged with PMMA resist on them, the samples are sputtered with few nm of Iridium to prevent the resist burning due to the electron bombardment.

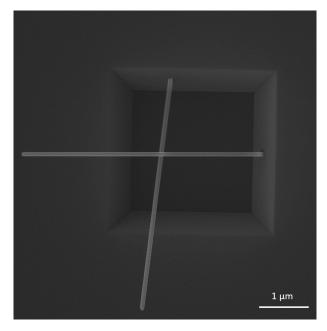

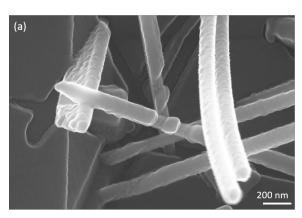

#### 3.2.2 Micromanipulator

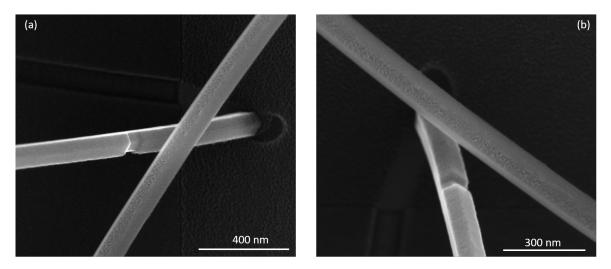

The in-situ Josephson junction samples were all transferred using a micromanipulator which is equipped in ZEISS Sigma 300 SEM. The Zeiss SEM is armed with a Kleindiek micromanipulator with 100 nm needles used for manipulation. This manipulator is a piezoelectric system that allows for XYZ motion for picking up nanowires and exactly placing them on gates etc. The manipulator tip is grounded to reduce the electrostatic effects which are caused by the charging effects of the SEM electron beam. The whole equipment is an exclusive tool which operates with a great precision and allows for the transfer of the desired NW on to any target substrate.

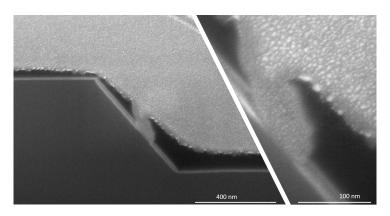

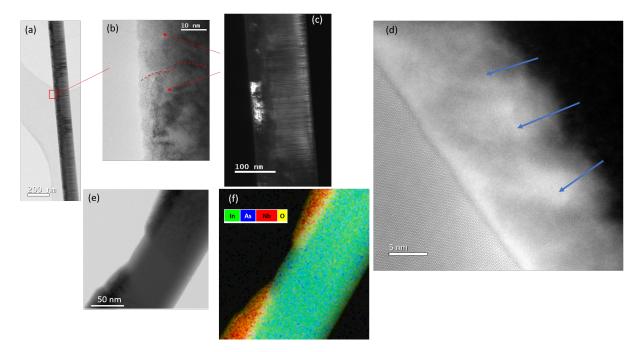

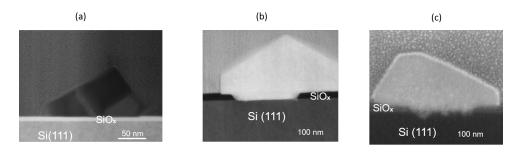

#### 3.2.3 Transmission Electron Microscopy

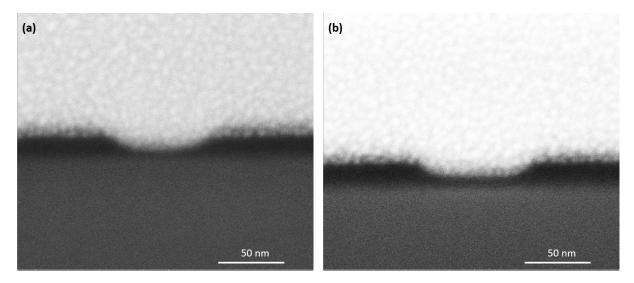

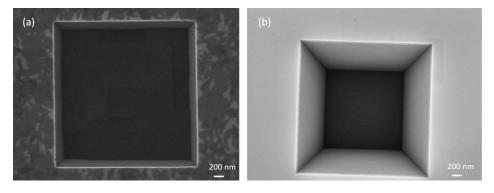

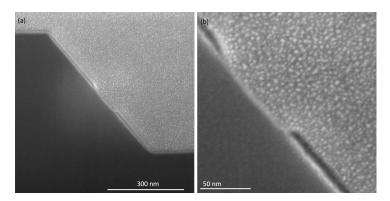

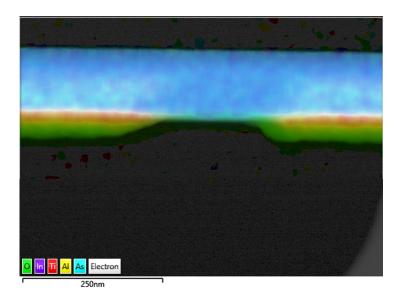

Transmission electron microscopy (TEM) analysis helps to determine the crystalline quality, presence of defects, and composition of the material system. The scanning transmission electron microscope images were collected using a Jeol ARM 200F operating at 200 kV for high resolution images and a Jeol 2100 was operated at 200 kV to obtain low resolution images in TEM mode. The samples were prepared by gently sweeping the carbon net-mesh grids across the surface of the as grown samples. The cross-sections were prepared by sputtering the samples with Pt and by milling trenches through the sample, as seen in Fig. 13.

#### 3.2.4 Atom Force Microscopy

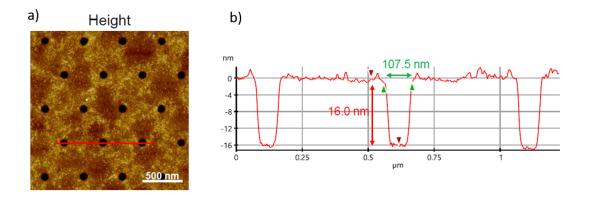

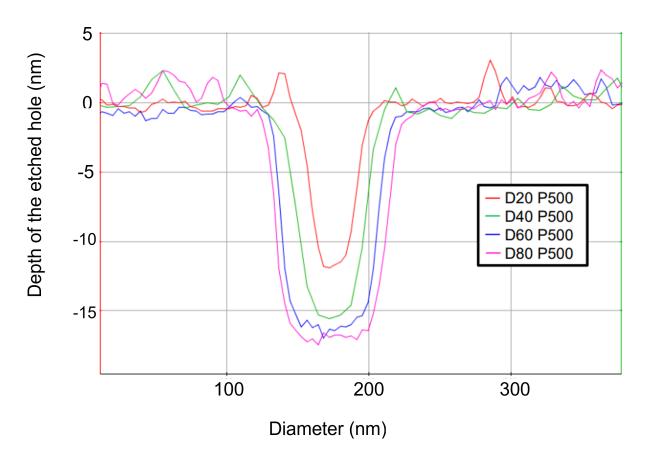

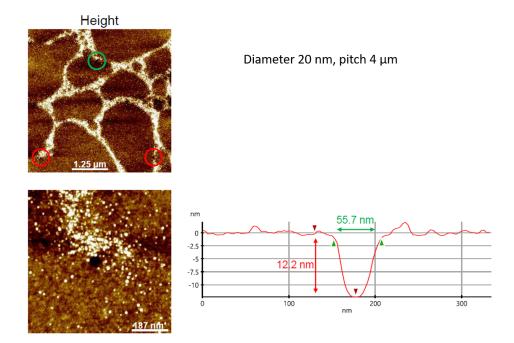

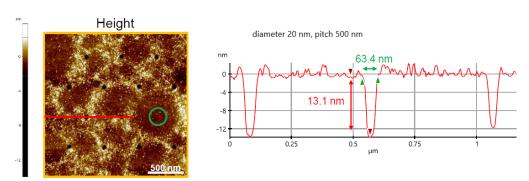

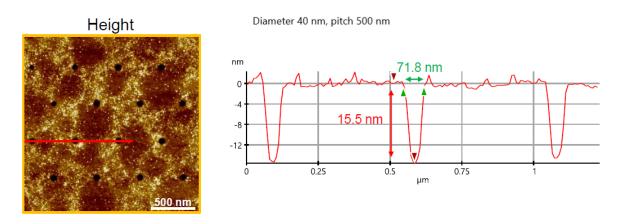

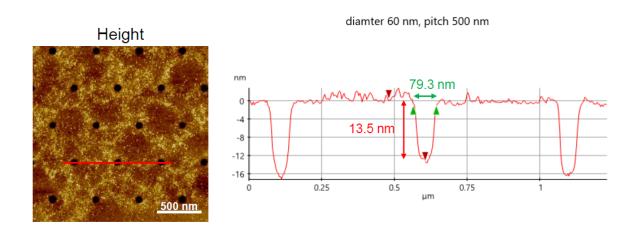

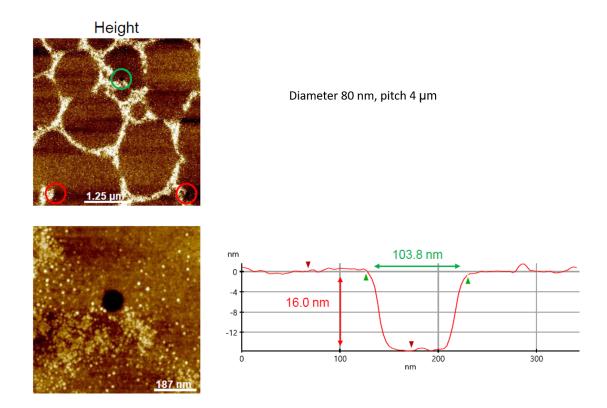

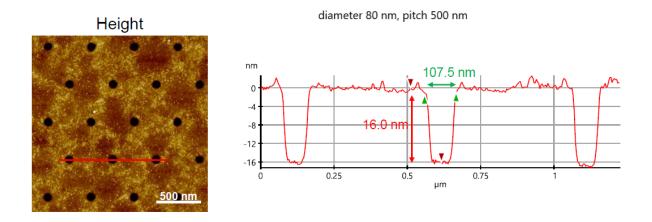

Atom force microscopy (AFM) is used for measuring the etched depth and profile of holes with varying width and pitch for nanowire growth. The surface information is collected and stored by scanning on the surface with a mechanical needle like probe. Piezoelectric elements help in having tiny but accurate movements, which helps in precise scanning. A Park AFM (NX20) was used in the non-contact mode with the cantilevers for coarse scanning, PPP NCHR (k = 42 N/m; f = 310 kHz) and for high resolution, C14/Cr Au (k = 5 N/m; k = 130 kHz). AFM analysis done on Si(111) with etched holes, can be seen in Fig. 14. Additional data from AFM analysis is presented in the appendix 9.1.

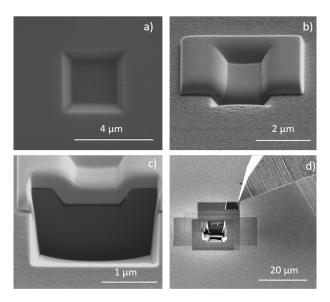

**Figure 13:** FIB (focused ion beam) based lamellae preparation. (a) Sample with square trenches. (b) A thick platinum layer is deposited on the desired area. (c) Ga ions used by the FIB to make a cross-section through the etched square. d) A thin cross-section (lamella) is cut and taken out on a grid for TEM analysis.

**Figure 14:** AFM. (a) AFM micrograph of the surface of the substrate with arrays of 80 nm holes. (b) The depth profile and the roughness of the given substrate.

## 3.2.5 Ellipsometer

Ellipsometry is based on polarization of light, used to characterize ultra thin films in the range of few nm. Ellipsometery uses a model based system to estimate the layer thickness. The layer thicknesses of the analyzed samples can be much smaller than the wavelength of the light. Hence, it is effectively used to record thickness measurements of thin films. An Accurion nanofilm RSE, fast spectroscopic ellipsometer is used measure the thickness of the resists and the oxides deposited during the course of this work.

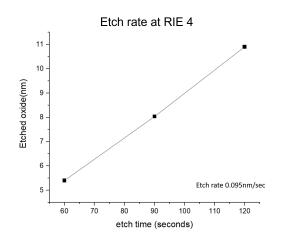

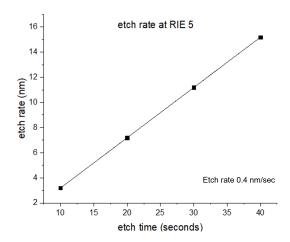

#### 3.2.6 Dry Etching

Dry etching is performed using reactive-ion etching (RIE) processes. It is an effective tool in micro-fabrication technology. It utilizes the chemically reactive plasma to remove the material

from the substrate. Electromagnetic field is used to produce the plasma under low pressure (vacuum). Thus, the high-energy ions formed due to the plasma, react with the substrate. All the RIE processes used in this thesis are performed by an Oxford PL 100/ICP RIE system with the cryo processing equipment [74].

# 4 Sample Fabrication

Through the course of this PhD project, all the sample fabrication and the process optimization was performed at the Helmholtz Nano Facility (HNF), a state-of-the-art cleanroom facility. The cleanroom has an area of  $1100 \text{ m}^2$  and belongs to class 1 [75]. HNF operates equivalent to Semiconductor Industry Association (SIA) standards [19]. The following sections of this chapter summarizes all steps of the fabrication processes used in this thesis.

# 4.1 Silicon (111) Substrate Preparation

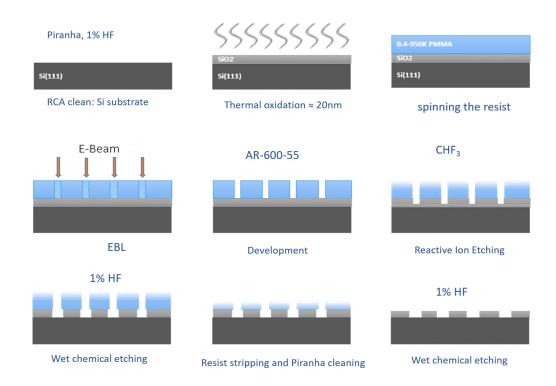

All the substrates for NW growth are based on Si wafers and are fabricated in a CMOS-compatible cleanroom to avoid cross-contamination. The substrate preparation for NW growth is an important step in selective area epitaxy (SAE) to have a good control over the vertical yield of the NWs. This process is optimized to have a moderately high yield of vertical NWs, crystallite free growth which is desired for greater homogeneity of the NWs. Figure 15 shows a schematic for the substrate preparation for SAE of the NWs. The growth substrates are n-doped As, Si(111), which are patterned with different hole diameters.

Figure 15: Schematic of the process steps: Fabrication of Si (111) substrates for NW growth

The process steps of the preparation of the pre-patterned substrates are as follows:

• A 100 mm n-doped Si(111) wafer is cleaned with strong piranha solution ( $H_2SO_4$  and  $H_2O_2$ ) to remove organic contaminants and native oxide from the substrate surface for 10 min. A 5 min HF dip is performed to passivate the Si surface, until it gets to the oxidation chamber.

- Within the next 15 minutes after cleaning, the wafer is thermally oxidised using the Massoud model [76] 990 °C for 33 min. These parameters are established for a  $SiO_2$  thickness of 20 nm, with a precision of  $\pm$  2 nm through out the entire wafer, which is confirmed by the ellipsometry. The thermal oxide is proven to be a good mask, for growth selectivity.

- After oxidation, the wafer is then coated with AZ5214E resist at 4000 rpm for 60 s using the spin coater. Later it is soft baked for 5 min at  $90^{\circ}$ C. This is done to protect the surface of the wafer from any contamination that from the next step of wafer dicing process. It is then diced into  $2.5 \times 2.5$  cm<sup>2</sup> sized square samples.

- The protective AZ5214E resist is then removed in an ultrasonic bath at high power with acetone and isopropyl alcohol (IPA) for 15 and 5 min, respectively.

- A 2 minute O<sub>2</sub> plasma bombardment, with 300 W and 200 sccm of O<sub>2</sub> flow is performed

on these samples prior to the PMMA coating to increase the hydrophillicity of SiO<sub>2</sub> and

which improves PMMA adhesion to the SiO<sub>2</sub>.

- To further improve the resist adhesion, the samples then are treated with HMDS at 120°C and then spin-coated with PMMA AR-P 679.04 950K resist at 6000 rpm for 30 s and soft baked at 180°C for 10 min. A 200 nm-thick-resist is obtained, which is confirmed with ellipsometry.

- Then EBL writing is performed to define the mask on the PMMA resist for SAE. For

development of this positive resist, the samples are dipped in AR-600 55 developer

solution for 70 s with continuous stirring movements and thereafter a slower development

is performed for better contrast of the 20-80 nm structures, by a 3 min dip in an IPA

(isopropyl alcohol) solution.

- After the development, a quick  $O_2$  plasma cleaning for 15 s with 300 W and 200 sccm of  $O_2$  is conducted to remove residual resist in the holes.

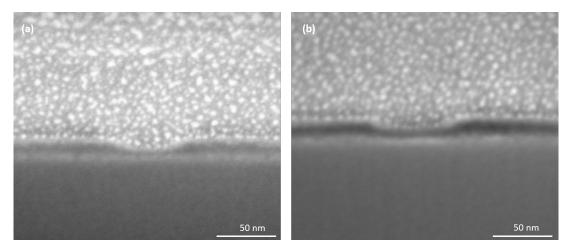

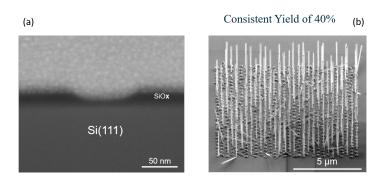

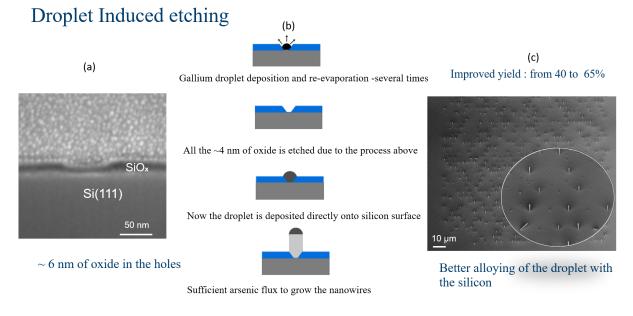

- So the hole array pattern can now be transferred onto SiO<sub>2</sub> by a combination of dry and wet chemical etching. Dry etching the hole completely, can cause a harmful damage to the silicon surface underneath [77], which affects the vertical yield of the nanowires and potentially could also result in a parasitic growth. Thus, roughly 16 nm of the SiO<sub>2</sub> is removed with RIE and the remaining 4 nm by dipping the sample in 1% HF for 60 s, which is considered to be a smoother etch.

- After the pattern is etched into the  $SiO_2$  layer, PMMA resist is removed using acetone and IPA in ultrasonic bath for 15 and 5 min, respectively. This is followed by a 10 min  $O_2$  plasma cleaning with a power of 300 W and 200 sccm gas flow.

- Eventually cleaned in a strong piranha solution ( $H_2SO_4$ : $H_2O_2 = 3:1$ ; 96%  $H_2SO_4$  and 37%  $H_2O_2$ ) for 10 min, and is finally rinsed in de-ionized (DI) water for 10 min.

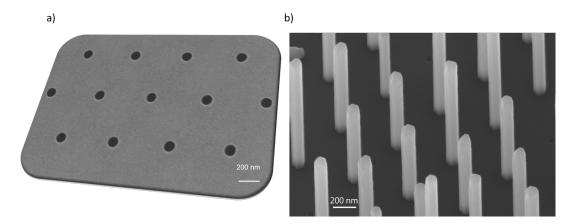

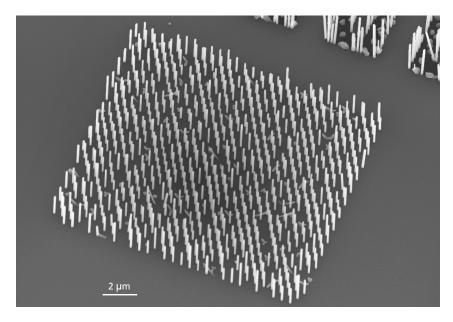

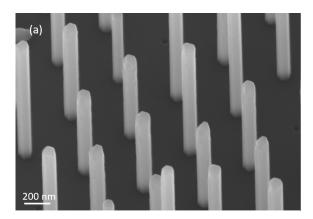

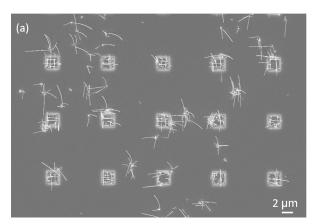

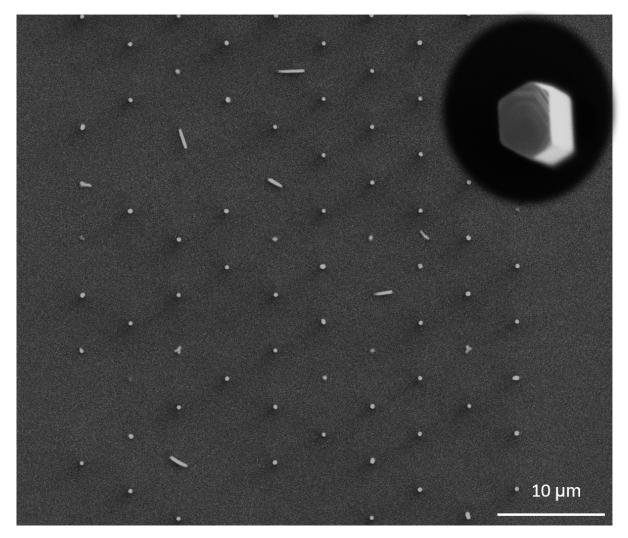

- Prior to loading the sample into MBE load-lock, it is dipped in 1% HF for  $60\,\mathrm{s}$ , to remove any native oxide on the growth substrate. The contrast between the hard mask  $\mathrm{SiO}_2$  and the  $\mathrm{Si}(111)$  is clearly seen. The finished substrate, before and after the growth of the nanowires with 500 nm pitch on  $\mathrm{Si}(111)$  substrate is shown in Figs. 16 (a) and (b), respectively.

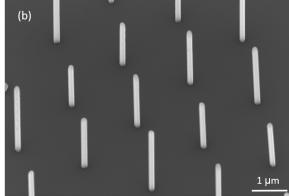

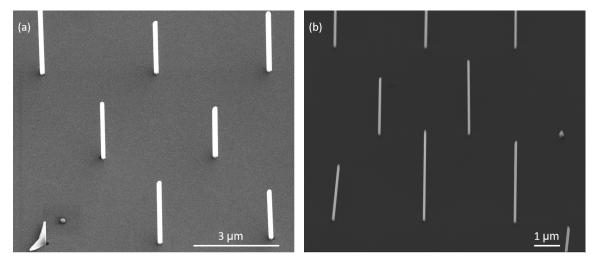

Figure 16: a) SEM micrograph of processed holes with 500 nm pitched array, clear contrast seen between the etched holes and the  $SiO_2$  mask. b) SEM micrograph of InAs nanowires grown on this substrate.

# 4.2 Silicon (100) Substrate Preparation

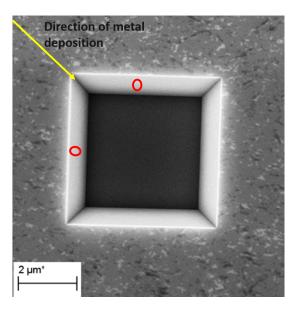

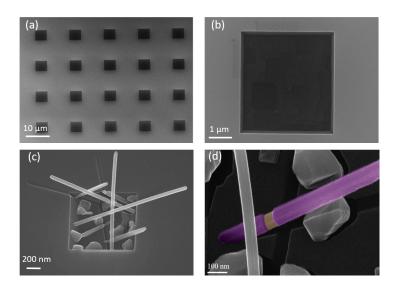

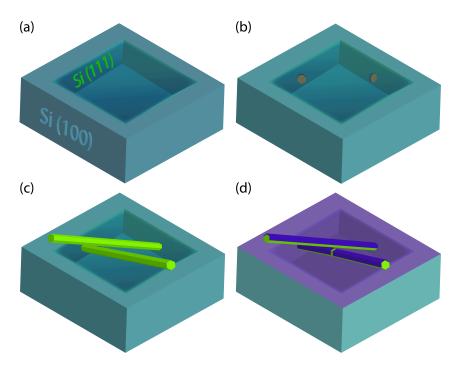

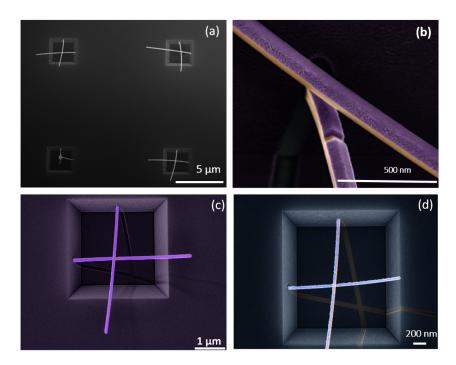

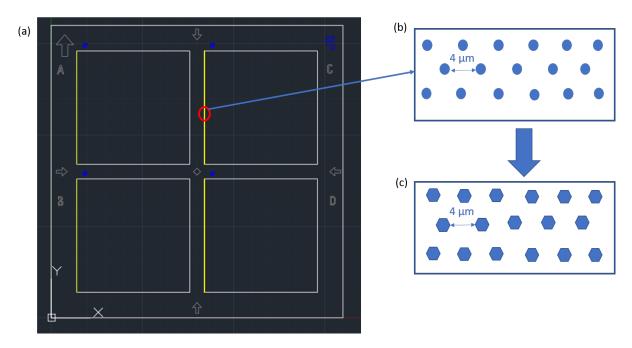

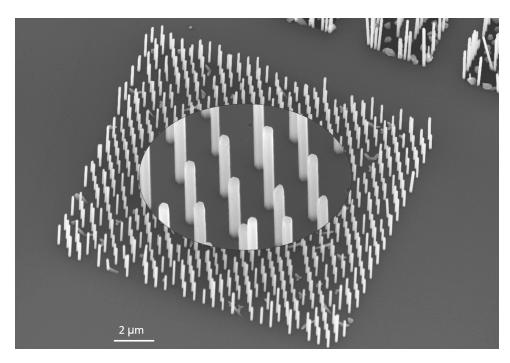

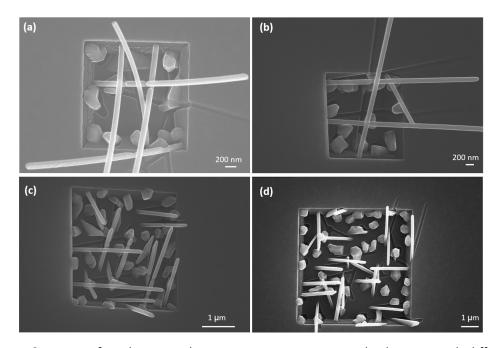

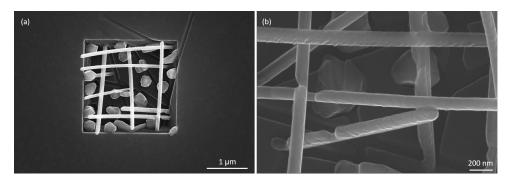

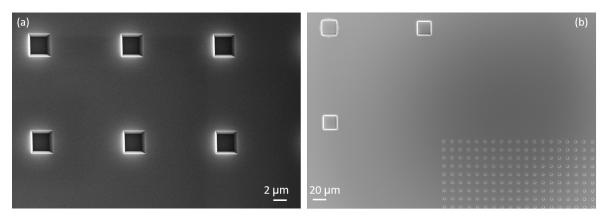

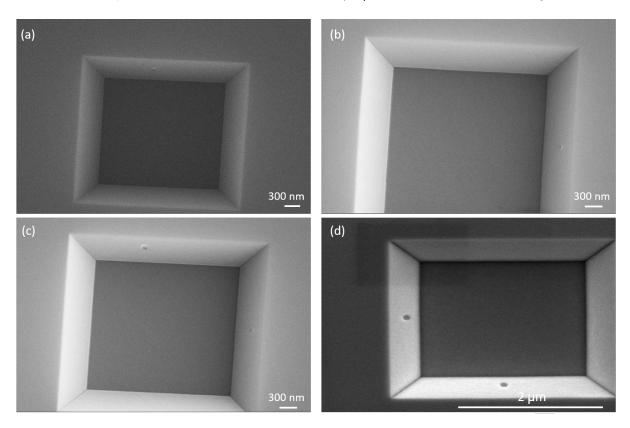

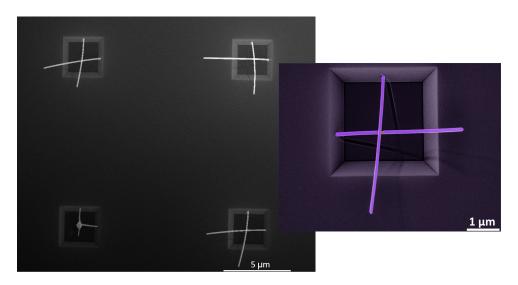

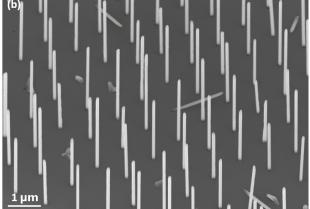

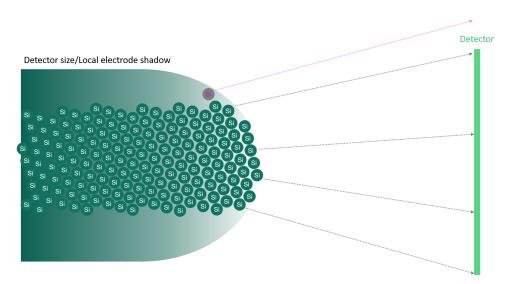

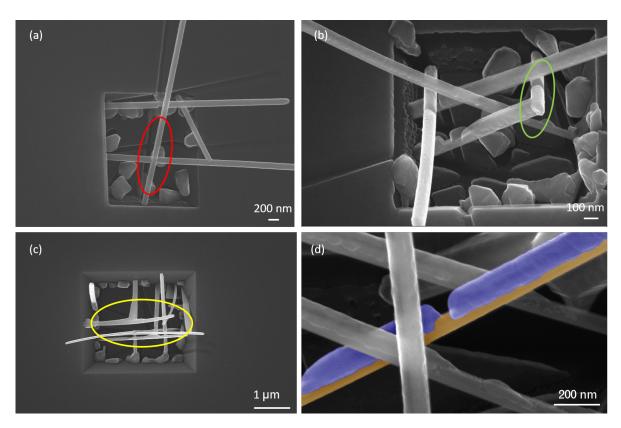

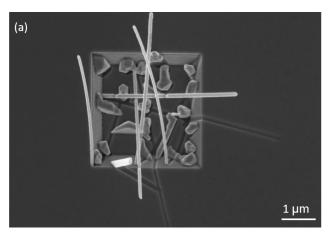

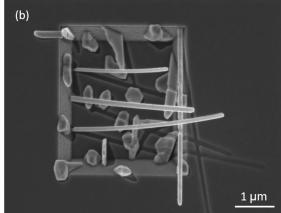

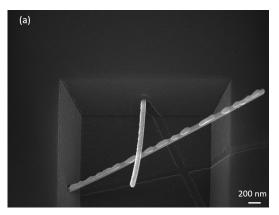

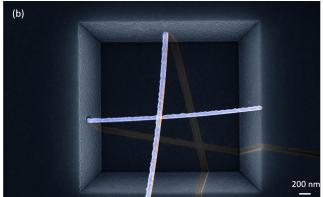

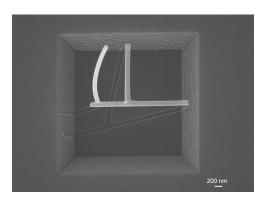

This sections demonstrates the fabrication process for combination of the in-situ evaporation of superconductor half-shells and realizing weak-links, in-situ on an InAs NWs. The InAs NWs are grown in way that a NW grown on a tilted Si(111) facet shadows another NW grown from an adjacent Si(111) facet during a metal deposition. The junction width is determined by the diameter of the NW. Two different methods are employed for the NW growth on the Si(111) facets. Firstly, a random growth procedure is performed for a study and as a quick & dirty method and secondly, as a betterment, a SAE technique using a pre-pattered SiO<sub>2</sub> growth mask is performed. This can be achieved as follows, given the geometry of the metal MBE chamber and the orientation of the metal crucible, the substrate is engineered in a way that two NWs are grown from elevated adjacent surfaces, grow out and meet each other by closing passing each other. Then, while still under UHV, the superconducting shell is deposited via e-beam evaporation with the direction of deposition is perpendicular to both nanowires, which causes smooth and crystalline metal shells on the semiconductor without any interfacial distress. The process here are optimized together with Timm Mörstedt and Abbas Espiari, master students at PGI-9.

When the substrate is not rotated during metal evaporation, it creates a half-shell on both the NWs, a shadow is cast on the lower wire by the upper wire leaving a weak link within the Josephson junction on the NWs. The idea of an engineered substrate for this arrangement is seen in Fig. 17. To obtain this kind of a substrate, two processes i.e. random growth process and SAE process have been developed.

#### 4.2.1 Substrates For Random Growth

This process steps to achieve these substrates are explained below.

- Initially a n-type Si(100) wafer is cleaned using a strong Piranha and 1% HF to remove organic matter or native oxide. The piranha solution consists of three parts sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) to one part hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>). Later a 10 minute Hf dip is performed to passivate the Si surface, until it gets to the oxidation chamber.

- The substrates are thermally oxidized withing 15 min under a high temperature of 990°

Figure 17: SEM micrograph of a substrate for template assisted growth :Si(100) substrates with exposed Si(111) facets at an elevated angle and the potential position of the nanowires depicted in the red, with  $45^{\circ}$  deposition of the metal.

in an oxidation furnace. The wafer is then thermally oxidized and the oxide thickness can be calculated using the Deal-Grove model:

$$t = \frac{d^2}{B} + \frac{dA}{B},\tag{4.1}$$

with the growth time t, thickness d and reaction-dependent parameters A and B [78].

- After oxidation, the wafers are coated with AZ resist at 4000 rpm for 60 s, soft baked for 5 min at 90 °C. This acts as a protective resistive for dicing. Then the sample is diced into 2.5 cm by 2.5 cm squares for further processing. Then the resist is removed by acetone for 15 min and IPA for 5 min in at high power in an ultrasonic bath.

- The samples are then prepared for random growth process, can be see in Fig. 18. The samples are coated with PMMA 950k in a spin coater. The sample is spun at 2000 rpm with 500 rpm/s pre-acceleration for 30 s with a closed lid. This results in a resist thicnkess of 220-240 nm.

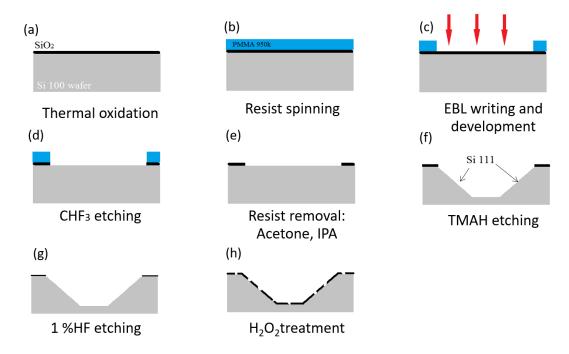

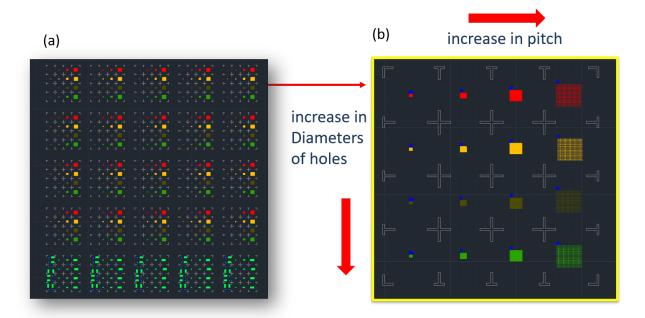

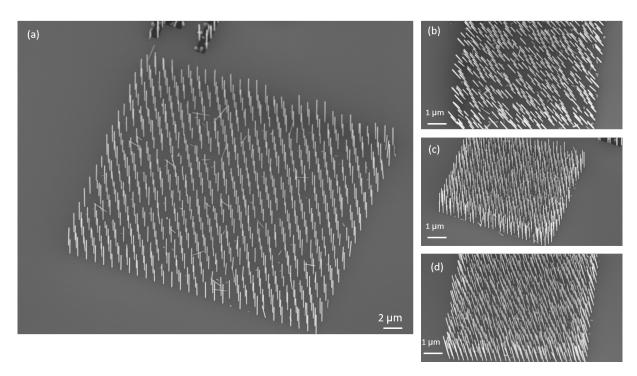

- The process of realizing these arrays of squares is presented in the schematic in Fig. 18. An array of squares with a size of 2, 3, 4, 5  $\mu$ m with a pitch (distance between squares) of  $10\,\mu$ m is written into the resist using electron beam lithography (EBL). Later, the sample is developed using an AR 600-55 developer for 70 s and into IPA for 3 min for better contrast. After that, the residual resist in the structures is removed by oxygen bombardment for 15 s at 300 W and 200 sccm.

- To etch the pattern into the resist an anisotropic dry etching process with RIE using CHF<sub>3</sub> and O<sub>2</sub> gases is used to etch silicon dioxide. The sample is etched at very low temperature of 5 °C for 4 min at 50 sccm/2 sccm. The remaining few nanometers of

Figure 18: Schematic of the Si (100) substrate fabrication processes.

oxide is smoothly etched by 1% HF for 60 s. Then the resist is removed completely by acetone for 15 min and IPA for 5 min using a high powered ultrasonic bath.

- The squares are now processed without any oxide in them. Then these squares are etched into the Si(100) underneath to expose (111) facets, thus forming square trenches. Before etching the samples with tetramethylammonium hydroxide (TMAH), a 20 s quick Hf dip is performed so that the Si(100) surface is native oxide free and TMAH is penetrable. TMAH is chosen here since, it is a selective etchant and etches Si(100) fast, but Si(111) is etched relatively slow. Additionally, TMAH also etches the SiO<sub>2</sub> mask, but rather slowly at a rate of 0.2 nm/min [79, 80]. Hence, SiO<sub>2</sub> thickness should be taken into account. The samples are etched in TMAH for 90 s that resulted in square trenches exposing Si(111) facets with depths of 300-350 nm.

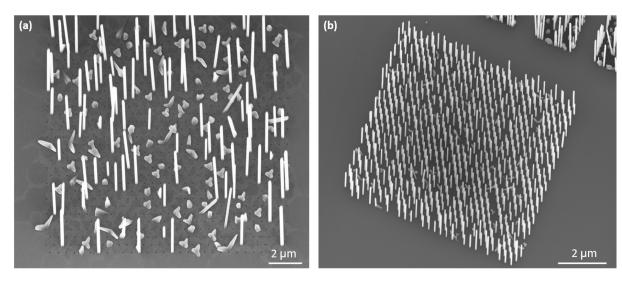

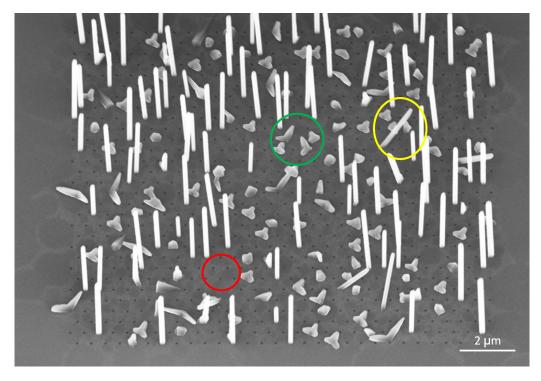

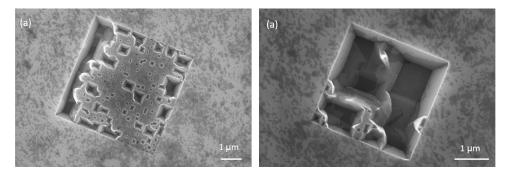

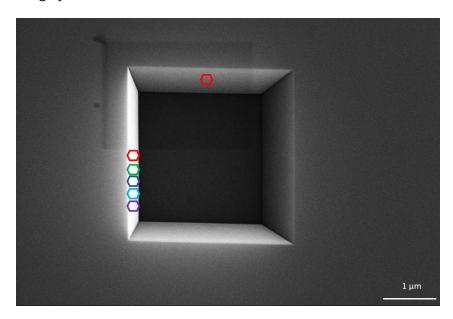

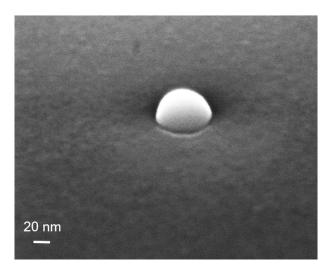

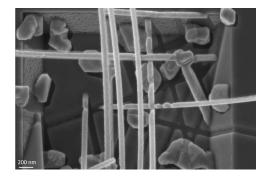

- The substrate is dipped into Hf for a quick rinse to remove native oxide. Later dipped into H<sub>2</sub>O<sub>2</sub> for 45 s to create a oxide of 2 nm. The oxide layer formed here is porous and when heated causes pinholes. These pinholes in the oxide layer can act as nucleation sites to grow InAs nanowires [81]. The finished product can be seen in Fig. 19 where the randomly grown NWs, most likely shadow each other from the adjacent Si(111) facets and form a fully in-situ Josephson junction.

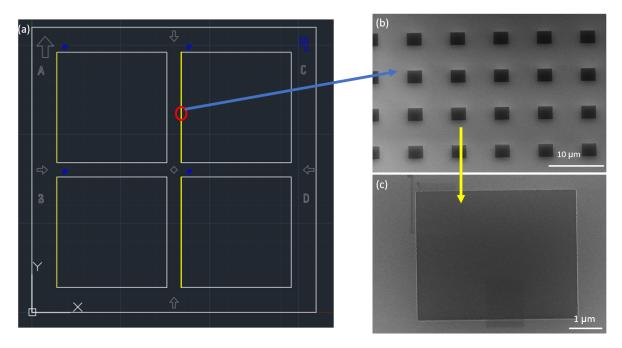

#### 4.2.2 Selective Area Epitaxy Substrates

For many reasons, the selective area epitaxy (SAE) process of fabricating the samples is a betterment of the procedure mentioned above for random growth process. The idea behind the process can be seen in the schematic presented in Fig. 20. To obtain substrates suitable for SAE, two additional processes of EBL are necessary which includes EBL markers to align

**Figure 19:** Substrate processing steps for achieving a Josephson junction with a weak-link formed in-situ by shadowing.

the 80 nm holes on the adjacent Si(111) facets, as a first step, and to write 80 nm holes on these substrates, as the last step. The process steps are as follows:

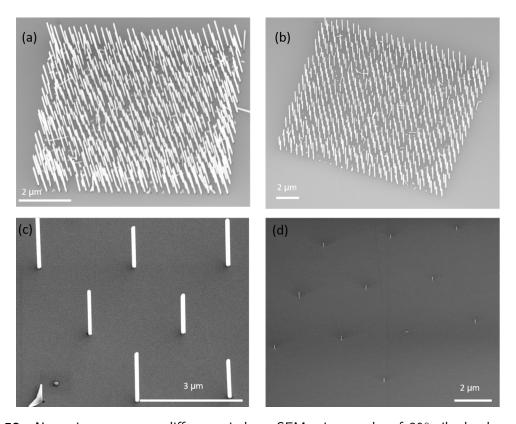

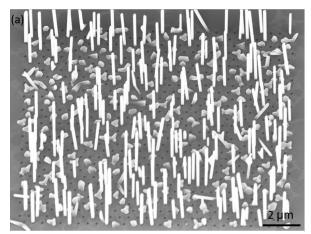

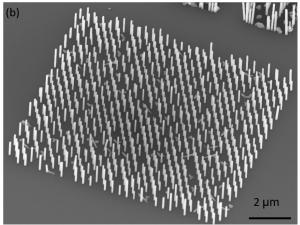

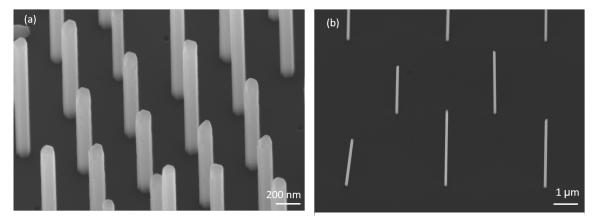

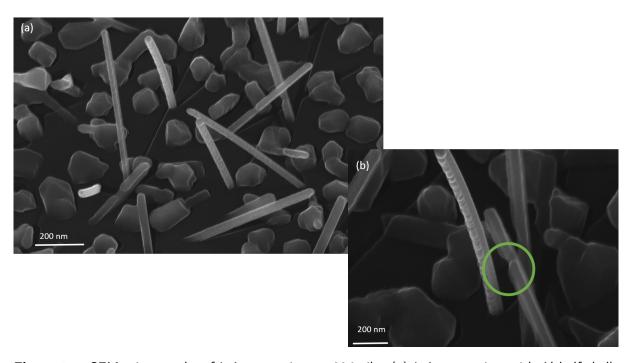

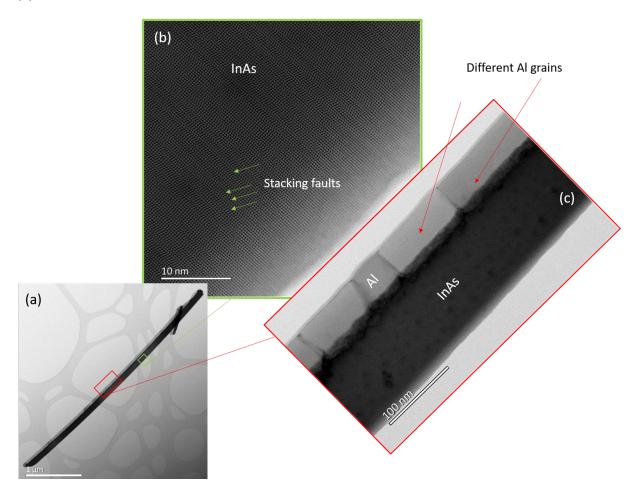

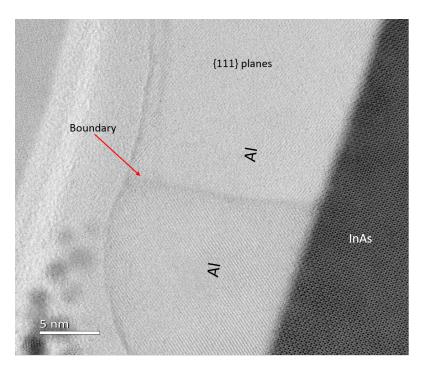

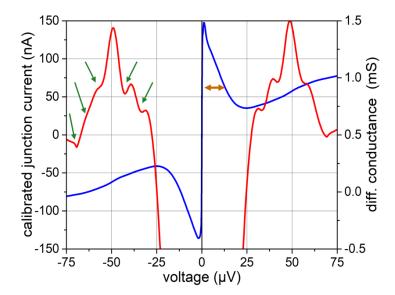

- The first EBL step is to implant the  $20~\mu m \times 20~\mu m$  squared EBL markers onto the sample surrounding a group of  $90\times 90$  square arrays. These markers ensure that amongst this set of  $90\times 90$  squares, all the growth holes are aligned to each other. So it begins with a diced Si(100) wafer with a 20 nm of thermal oxide layer. The sample is spin-coated with UV6 resist at 4000 rpm. This results in a resist thickness of approximately 600 nm. Furthermore, the resist is soft baked at  $130~^{\circ}\text{C}$  for 1 min. After the EBL writing process, the sample is developed using MF CD-26 solution for 90~s. Further on, the markers are etched into  $\text{SiO}_2$  and Si by dry etching anisotropic RIE process. First, a RIE with CHF $_3$  and  $\text{O}_2$  is used to etch the 20 nm oxide layer for 3 min and then 2 min of SF $_6$  etching is used to etch deep into Si at 20  $^{\circ}\text{C}$ . This etches  $1\mu\text{m}$  deep EBL markers into the substrate. Later the remaining UV6 is removed with 10 min using acetone and 5 min using IPA in a high powered ultrasonic bath. This process constitutes the first EBL step.