# Development and production of an intelligent PMT readout system for OSIRIS

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

Christian Wysotzki, M.Sc.

aus

Viersen

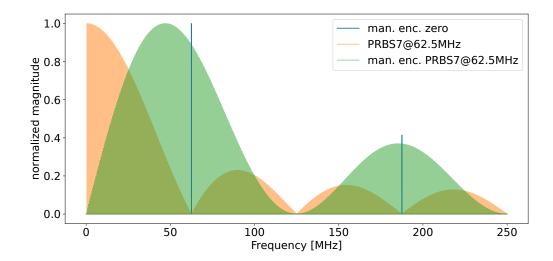

Berichter: Univ.-Prof. Dr. rer. nat. Achim Stahl

Univ.-Prof. Dr. rer. nat. Christopher Wiebusch

Tag der mündlichen Prüfung: 20.01.2023

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek verfügbar.

#### **Abstract**

The Jiangmen Underground Neutrino Observatory (JUNO) is a neutrino detector currently under construction in South China. The experiment is built to contribute substantially to central unsolved neutrino physics questions. Examples are the determination of the neutrino mass ordering and precision measurements of neutrino mixing angles.

An inalienable prerequisite for precise measurements is a high radiopurity of the detector, especially of the liquid scintillator. In order to investigate the radioactivity of the liquid scintillator, the dedicated Online Scintillator Internal Radioactivity Investigation System (OSIRIS) is built. It uses photomultiplier tubes (PMTs) for the detection of light caused by radioactive decays. A new system is developed for OSIRIS which attaches the PMT readout electronics directly at its back. This system directly processes the digitized PMT signals and is therefore denoted as intelligent PMT (iPMT).

The design of the iPMT system with a focus on the electronics is described in detail. As part of this thesis, an FPGA design for the PMT readout and the control of the iPMT is implemented and tested. Furthermore, an FPGA design for the synchronization of the iPMTs with each other and with calibration systems in OSIRIS is developed.

Characterizing measurements with a focus on central capabilities of the system are presented. This includes properties of the readout chain and an evaluation of the timing and synchronization system. An exemplary evaluation of the performance with a PMT is presented.

Concluding, the electronics assembly of the iPMTs for OSIRIS is described. Prior shipment to China, the iPMTs undergo functional verification tests, and the corresponding results are presented. In total, 75 iPMTs are successfully tested for the use in OSIRIS.

#### Zusammenfassung

Das Jiangmen Underground Neutrino Observatory (JUNO) ist ein Neutrinodetektor, der sich in aktuell in Südchina im Aufbau befindet. Das Experiment ist darauf ausgelegt substantielle Beiträge zu zentralen ungelösten Fragen der Neutrinophysik zu leisten. Dazu gehören beispielsweise die Bestimmung der Neutrino Massenordnung und Präzisionsmessungen von Neutrino Mischungswinkeln.

Um genaue Messungen zu gewährleisten sind sehr geringe radioaktive Verunreinigungen des Detektors, inbesondere des Flüssigszintillators, nötig. Um die Radioaktivität des Flüssigsszintillators zu überprüfen, wird das dedizierte Online Scintillator Internal Radioactivity Investigation System (OSIRIS) gebaut. Es nutzt Photomultiplier Tubes (PMTs) zur Detektion von Licht welches durch radioaktive Zerfälle hervorgerufen wird. Ein neues System, bei der die PMT Ausleseelektronik direkt am PMT befestigt wird, wurde für OSIRIS entwickelt. Dieses System verarbeitet die digitalisierten PMT Signale direkt und wird daher als intelligenter PMT (iPMT) bezeichnet.

Der Aufbau des iPMT Systems wird im Detail beschrieben, wobei der Fokus auf der Elektronik liegt. Als Teil dieser Arbeit wurde ein FPGA Design für die Auslese der PMTs und Kontrolle der iPMTs entworfen, implementiert und getestet. Desweiteren wurde ein FPGA Design für die Synchronisierung der iPMTs untereinander und mit Kalibrationssystemen in OSIRIS entwickelt.

Charakterisierende Messungen mit dem Fokues auf zentralen Fähigkeiten des Systems werden vorgestellt. Dies beinhaltet die Evaluation der Synchronisierung, sowie Eigenschaften der Datenauslese. Beispielhaft wird die Performance an einem PMT präsentiert.

Abschließend wird der Zusammenbau der Elektronik der iPMTs für OSIRIS beschrieben. Vor dem Export nach China wurde die Funktionalität der iPMTs getestet und die entsprechende Ergebnisse werden präsentiert. Für den Einbau in OSIRIS wurden insgesamt 75 iPMTs erfolgreich getestet.

## **Contents**

| A  | bstract                                       | i   |

|----|-----------------------------------------------|-----|

| Zι | usammenfassung                                | iii |

| C  | ontents                                       | v   |

| A  | cronyms                                       | vii |

| 1  | Introduction                                  | 1   |

| 2  | Neutrino oscillation                          | 3   |

|    | 2.1 Neutrino sources                          | 5   |

|    | 2.2 Open neutrino physics questions           | 6   |

| 3  | The Jiangmen Underground Neutrino Observatory | 9   |

|    | 3.1 JUNO overview                             | 9   |

|    | 3.2 JUNO physics program                      | 11  |

|    | 3.3 OSIRIS                                    | 13  |

| 4  | Intelligent Photomultiplier Tube System       | 19  |

|    | 4.1 Motivation and Concept                    | 19  |

|    | 4.2 Photomultiplier tubes                     | 21  |

|    | 4.3 iPMT mechanics overview                   | 22  |

|    | 4.4 iPMT electronics stack                    | 24  |

|    | 4.5 Surface Board electronics                 | 35  |

|    | 4.6 Timing system within OSIRIS               | 36  |

| 5  | FPGA and software design                      | 39  |

|    | 5.1 General design considerations             | 39  |

|    | 5.2 iPMT FPGA design                          | 40  |

|    | 5.3 Triggering with the Event Builder         | 48  |

|    | 5.4 Surface Board FPGA design                 | 50  |

|    | 5.5 iPMT software infrastructure              | 54  |

|    | 5.6 System startup and configuration          | 55  |

| 6  | iPMT system characterization                  | 59  |

|    | 6.1 PoE Board                                 | 59  |

|    | 6.2 Power consumption                         | 59  |

|    | 6.3 VULCAN configuration                      | 62  |

|    | 6.4 VULCAN parameter tuning                   | 63  |

|    | 6.5 VULCAN absolute current calibration       | 71  |

|    | 6.6 Readout transfer capability               | 83  |

vi *CONTENTS*

|     | 6.7   | Synchronous link and synchronization verification | 84  |

|-----|-------|---------------------------------------------------|-----|

|     | 6.8   | iPMT evaluation with a PMT                        | 91  |

| 7   | iPM   | T production                                      | 95  |

|     | 7.1   | iPMT electronics assembly                         | 95  |

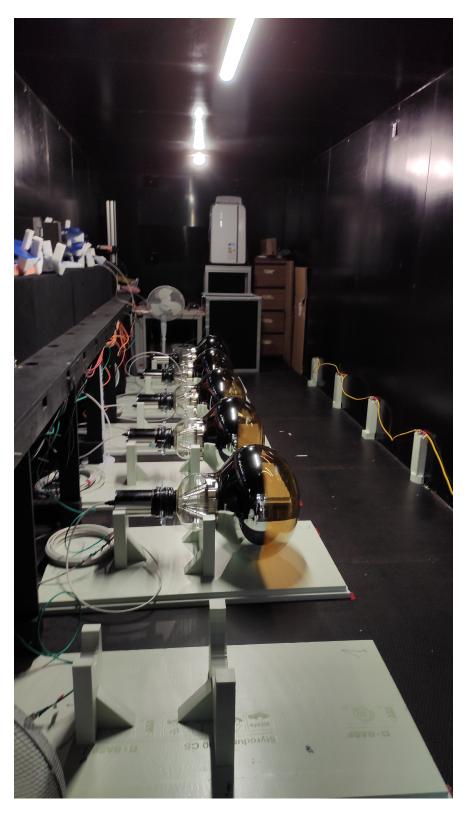

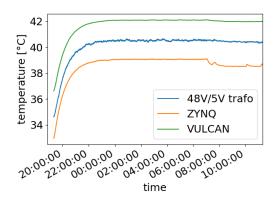

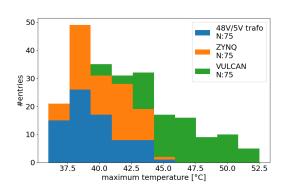

|     | 7.2   | Verification tests in the cooltainer              | 96  |

|     | 7.3   | Test results                                      | 98  |

|     | 7.4   | Production summary                                | 104 |

|     | 7.5   | Typical characteristics of an iPMT                | 104 |

| 8   | Sun   | nmary and outlook                                 | 107 |

| Ap  | pen   | dices                                             | 109 |

| A   | OSI   | RIS PMT parameters                                | 111 |

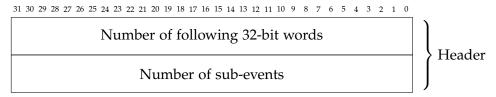

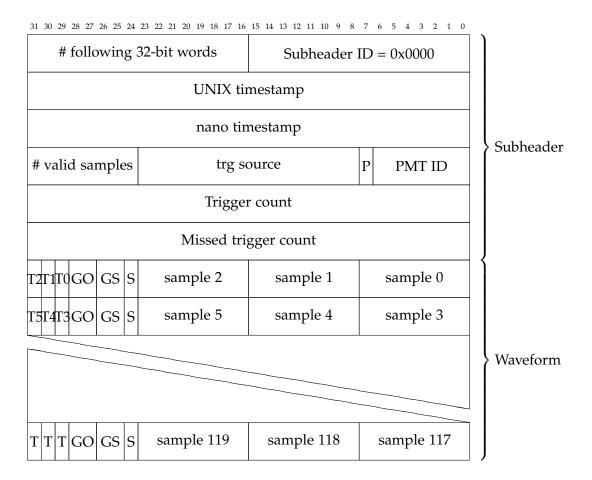

| В   | Dat   | a transmission protocol                           | 113 |

| C   | Clo   | ck and data recovery                              | 119 |

| D   | FPC   | A design                                          | 123 |

|     |       | FPGA design flow                                  | 123 |

|     |       | FPGA elements                                     | 124 |

| E   | Syn   | chronization test                                 | 125 |

| Lis | st of | Figures                                           | 127 |

| Lis | st of | Tables                                            | 131 |

| Bi  | bliog | raphy                                             | 133 |

## **Acronyms**

**AC** Alternating Current.

ADC Analog-to-Digital Converter.

ASIC Application-Specific Integrated Circuit.

AV Acrylic Vessel.

BER Bit Error Rate.

CD Central Detector.

CDR Clock and Data Recovery.

DAC Digital-to-Analog Converter.

DAQ Data Acquisition.

DC Direct Current.

DCR Dark Count Rate.

DMA Direct Memory Access.

EB Event Builder.

**EEPROM** Electrically Erasable Programmable Read-Only Memory.

FPGA Field Programmable Gate Array.

FSM Finite-State Machine.

FWHM Full Width Half Maximum.

HG High Gain.

HV High Voltage.

IBD Inverse Beta Decay.

IC Integrated Circuit.

IO Inverted Ordering.

**IP-Core** Intellectual Property Core.

iPMT intelligent PhotoMultiplier Tube.

viii Acronyms

I<sup>2</sup>C Inter-Integrated Circuit.

JTAG Joint Test Action Group.

JUNO Jiangmen Underground Neutrino Observatory.

LFSR Linear-feedback Shift Register.

LG Low Gain.

LS Liquid Scintillator.

LSB Least Significant Bit.

LVDS Low Voltage Differential Signaling.

MG Mid Gain.

NO Normal Ordering.

OS Operating System.

OSIRIS Online Scintillator Internal Radioactivity Investigation System.

**p.e.** PMT output signal equivalent to one **p**hoto **e**lectron.

PCB Printed Circuit Board.

PGA Programmable Gain Amplifier.

PL Programmable Logic.

PMNS Pontecorvo-Maki-Nakagawa-Sakata.

PMT PhotoMultiplier Tube.

PoE Power over Ethernet.

PPS Pulse Per Second.

PRBS Pseudo Random Binary Sequence.

PS Processing System.

RAM Random Access Memory.

RoB Readout Board.

SB Surface Board.

SCB Surface Connector Board.

SCCU Slow Control and Configuration Unit.

SNR Signal-to-Noise-Ratio.

Acronyms ix

**SoC** System-on-a-Chip.

TB Trigger Board.

TCP Transmission Control Protocol.

TIA Transimpedance Amplifier.

TTS Transit Time Spread.

UART Universal Asynchronous Receiver Transmitter.

UDP User Datagram Protocol.

VHDL Very High Speed Integrated Circuit Hardware Description Language.

**VULCAN** Integrated circuit dedicated for PMT readout designed by ZEA-2, Jülich.

## Chapter 1

## Introduction

In 1930, Pauli postulated the existence of a very light particle, the neutrino, to explain the continuous energy spectrum of the  $\beta$  decay. The existence of this particle could be confirmed almost three decades later, in 1956, by the Cowan-Reines neutrino experiment at the Savannah River Plant with a nuclear reactor as neutrino source [1]. Since then, many experiments have been conducted to unriddle the properties of neutrinos.

In 1968 the Homestake experiment measured neutrinos from the sun and found hints for a discrepancy between the standard solar model and the experiment [2]. The detection rate of solar neutrinos was significantly lower than predicted by the standard solar model, which was then called the *solar neutrino problem* [3].

A possible explanation had already been proposed several years earlier by Pontecorvo in 1957 [4]. He suggested neutrino oscillations as quantum mechanical phenomenon, in which the oscillations are due to the interference of different massive neutrinos [3, p. 245].

The existence of neutrino oscillation has been proven first by the experiments Super-Kamiokande in 1998 [5] and SNO in 2001 [6], which was recognized by awarding the 2015 Nobel prize to the leaders of the two experiments.

Following measurements of the neutrino mixing angle  $\theta_{13}$  by DayaBay [7], Double-Chooz [8] and RENO [9] allowed the meaningful planning of further experiments [10].

One of those experiments is the Jiangmen Underground Neutrino Observatory (JUNO), which is currently under construction in South China. It aims to provide precise measurements of neutrinos from various sources. Large effort is put into the control and monitoring of the radiopurity of the detector materials to reduce the backgrounds for the experiment. Of foremost importance is the radiopurity of the Liquid Scintillator (LS). A dedicated detector – the Online Scintillator Internal Radioactivity Investigation System (OSIRIS) – is built to monitor the radiopurity of the LS. Chapter 3 gives an overview over the neutrino experiment JUNO and its sub-detector OSIRIS.

OSIRIS' measurement of the radioactivity is based on the detection of light induced by the decay of radioactive isotopes. In order to detect these faint light signals, large area PhotoMultiplier Tubes (PMTs) are used.

A novel system of the readout of PMTs is implemented for OSIRIS. It features a dedicated set of electronics attached at the back of each PMT and is called intelligent PhotoMultiplier Tube (iPMT). A detailed description of this system is given in Chapter 4.

As part of the electronics, Field Programmable Gate Arrays (FPGAs) are used for the PMT readout and data processing. The development of the FPGA designs is part of this thesis and presented in Chapter 5. A characterization of the system, including the evaluation of the readout performance and the synchronization, is presented in Chapter 6.

As final section, parts of the production of the iPMTs are described in Chapter 7. This includes the assembly of the electronics and functional verification tests of complete iPMTs.

A summary of the results and an outlook on future developments are given in Chapter 8.

## Chapter 2

## Neutrino oscillation

The current best model describing elementary particles and their strong, electromagnetic and weak interactions as a quantum field theory is the standard model. Nonetheless, the experimental evidence exists, that the model is incomplete in several aspects, one of them regards the field of neutrinos.

(Anti-)Neutrinos are massless fermions in the standard model [11, p. 285] and exist in three flavors (particles:  $\nu_e$ ,  $\nu_\mu$ ,  $\nu_\tau$  antiparticles:  $\bar{\nu}_e$ ,  $\bar{\nu}_\mu$ ,  $\bar{\nu}_\tau$ ). They interact only weakly via charged current interaction ( $W^\pm$ ) or neutral current interaction ( $Z^0$ ) with other standard model particles. It has been observed that neutrinos periodically change their flavor depending on their energy and traveled distance. This phenomenon is called neutrino oscillation.

In contradiction to the standard model, neutrino oscillation requires non-vanishing neutrino masses. A flavor eigenstate of a neutrino, as it is produced from the interaction with a charged lepton can be written as linear combination of mass eigenstates

$$|\nu_{\alpha}\rangle = \sum_{\kappa=1}^{n} U_{\alpha\kappa}^{*} |\nu_{\kappa}\rangle \tag{2.1}$$

with the flavor eigenstates  $\nu_{\alpha}$  ( $\alpha=e,\mu,\tau$ ), the number of light neutrino  $n=3^1$ , the complex conjugate of the elements of the mixing matrix  $U_{\alpha\kappa}$  and the mass eigenstates  $\nu_{\kappa}$  ( $\kappa=1,2,3$ ) [11]. U is a 3 x 3 unitary matrix describing the flavor eigenstates as linear combinations of mass eigenstates

$$\begin{pmatrix} \nu_e \\ \nu_{\mu} \\ \nu_{\tau} \end{pmatrix} = \begin{pmatrix} U_{e1} & U_{e2} & U_{e3} \\ U_{\mu 1} & U_{\mu 2} & U_{\mu 3} \\ U_{\tau 1} & U_{\tau 2} & U_{\tau 3} \end{pmatrix} \begin{pmatrix} \nu_1 \\ \nu_2 \\ \nu_3 \end{pmatrix}. \tag{2.2}$$

<sup>&</sup>lt;sup>1</sup>Ignoring the possibility of additional sterile neutrinos, which do not undergo weak interactions [3, p. 247].

This matrix can also be written in the form of three rotations (with the second rotation depending on the phase  $\delta_{CP}$ ) and a phase matrix [11, p. 288, 12]

$$U = \begin{pmatrix} 1 & 0 & 0 \\ 0 & c_{23} & s_{23} \\ 0 & -s_{23} & c_{23} \end{pmatrix} \begin{pmatrix} c_{13} & 0 & s_{13}e^{-i\delta_{CP}} \\ 0 & 1 & 0 \\ -s_{13}e^{i\delta_{CP}} & 0 & c_{13} \end{pmatrix} \begin{pmatrix} c_{21} & s_{12} & 0 \\ -s_{12} & c_{12} & 0 \\ 0 & 0 & 1 \end{pmatrix} P_{\eta}$$

$$= \begin{pmatrix} c_{12}c_{13} & s_{12}c_{13} & s_{13}e^{-i\delta_{CP}} \\ -s_{12}c_{23} - c_{12}s_{13}s_{23}e^{i\delta_{CP}} & c_{12}c_{23} - s_{12}s_{13}s_{23}e^{i\delta_{CP}} & c_{13}s_{23} \\ s_{12}s_{23} - c_{12}s_{13}c_{23}e^{i\delta_{CP}} & -c_{12}s_{23} - s_{12}s_{13}c_{23}e^{i\delta_{CP}} & c_{13}c_{23} \end{pmatrix} P_{\eta}$$

$$(2.3)$$

with  $c_{ij} \equiv \cos \theta_{ij}$ ,  $s_{ij} \equiv \sin \theta_{ij}$  and the matrix  $P_{\eta}$  describing the Majorana phases which can be neglected for neutrino oscillation [13] (in case of Dirac particles  $P_{\eta}$  becomes the identity matrix). U is known as the Pontecorvo-Maki-Nakagawa-Sakata (PMNS) mixing matrix giving credit to those persons which formulated the mixing of different neutrino families [11].

The four free parameters in the matrix are denoted as the mixing angles  $\theta_{12}$ ,  $\theta_{13}$ ,  $\theta_{23}$  and the CP-violating phase  $\delta_{CP}$  [14].

In order to observe the neutrino oscillation, the time evolution of the flavor state has to be considered, since the neutrino is created as a pure flavor state in a weak interaction. The time evolution of a massive neutrino is given as superposition of planar waves

$$|\nu_{\alpha}(t)\rangle = \sum_{\kappa=1}^{n} U_{\alpha\kappa}^{*} e^{-iE_{\kappa}t} |\nu_{\kappa}\rangle$$

(2.4)

with  $E_{\kappa} = \sqrt{\mathbf{p}_{\kappa}^2 + m_{\kappa}^2}$  and  $m_{\kappa}$  ( $\mathbf{p}_{\kappa}$ ) the mass (momentum) of the neutrino mass eigenstate  $\nu_{\kappa}$  (quantities are expressed in natural units ( $c = \hbar = 1$ )) [3, p. 248].

The mass eigenstate can be expressed in terms of flavor eigenstates as following [3, p. 248]:

$$|\nu_{\kappa}\rangle = \sum_{\kappa} U_{\alpha\kappa} |\nu_{\alpha}\rangle. \tag{2.5}$$

Substituting the mass eigenstate in Eq. (2.4) results in

$$|\nu_{\alpha}(t)\rangle = \sum_{\beta} \left( \sum_{\kappa=1}^{n} U_{\alpha\kappa}^{*} e^{-iE_{\kappa}t} U_{\beta\kappa} \right) |\nu_{\alpha}\rangle$$

(2.6)

with  $\beta = e, \mu, \tau$  [3]. By this, the time evolved flavor state is expressed in terms of different flavor states. Since the mixing matrix U is not diagonal, a pure flavor eigenstate at t = 0 becomes a superposition of different flavor states for t > 0. The composition of the mass eigenstates is visualized in Fig. 2.1.

The probability for the transition from a flavor state  $\alpha$  to a flavor state  $\beta$  when the neutrino interacts and produces a charged lepton is given as [3, p. 249, 11, p. 288]:

$$P_{\nu_{\alpha} \to \nu_{\beta}}(t) = \sum_{\kappa=1, j=1}^{n} U_{\alpha\kappa}^* U_{\beta\kappa} U_{\alpha j} U_{\beta j}^* e^{-i(E_{\kappa} - E_{j})t}. \tag{2.7}$$

In the ultra-relativistic limit  $t \simeq cL$ , the dependency of  $P_{\nu_{\alpha} \to \nu_{\beta}}(t)$  on t is expressed as dependency on the distance L (baseline) [3].

2.1. Neutrino sources 5

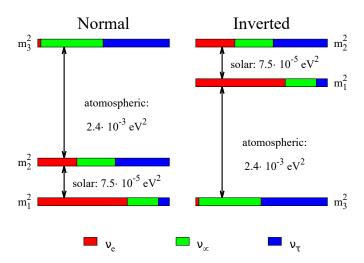

Figure 2.1: Illustration of the flavor composition of the three mass eigenstates  $m_1$ ,  $m_2$  and  $m_3$  [15]. The colors indicate the flavor composition of the mass eigenstates. Additionally the two mass ordering options (normal / inverted) are depicted. The relative ordering  $m_2 > m_1$  is known from solar neutrino measurements [16], but whether  $m_1 < m_2 < m_3$  or  $m_3 < m_1 < m_2$  is true, is unknown.

The transition probability in Eq. (2.7) is derived for neutrinos. For the case of antineutrinos, the corresponding coefficients can be calculated by the complex conjugate of the elements of U [3, p. 255]. As example, the electron anti-neutrino survival probability in vacuum is given

$$\begin{split} P_{\overline{\nu}_{e} \to \overline{\nu}_{e}} &= 1 - \sin^{2} 2\theta_{13} (c_{12}^{2} \sin^{2} \Delta_{31} + s_{12}^{2} \sin^{2} \Delta_{32}) - c_{13}^{4} \sin^{2} 2\theta_{12} \sin^{2} \Delta_{21} \\ &= 1 - \sin^{2} 2\theta_{13} \left[ c_{12}^{2} \sin^{2} \frac{\Delta m_{31}^{2} L}{4E} + s_{12}^{2} \sin^{2} \frac{\Delta m_{32}^{2} L}{4E} \right] \\ &- c_{13}^{4} \sin^{2} 2\theta_{12} \sin^{2} \frac{\Delta m_{21}^{2} L}{4E} \end{split} \tag{2.8}$$

with  $\Delta_{ij} = \Delta m_{ij}^2 L/4E$  and  $\Delta m_{ij}^2 \equiv m_i^2 - m_j^2$ , with the baseline L and the electron anti-neutrino energy E [17, 18, p. 2].

The vacuum solution can be used for reactor neutrino experiments on earth, since the terrestrial matter effects on  $P_{\overline{\nu}_e \to \overline{\nu}_e}$  are mostly negligible small, due to low neutrino energies and baselines  $L < 100 \, \mathrm{km}$  [18, p. 21].

The mass squared difference  $\Delta m^2_{21}$  is also denoted as "solar" mass splitting, due to its dominance for solar  $\nu_e$  oscillations. The "atmospheric" mass splitting  $\Delta m^2_{31}$  is dominant for atmospheric  $\nu_\mu$  and  $\overline{\nu}_\mu$  oscillations.

More comprehensive overviews of neutrino oscillation are given in [14], [11, p. 285 ff.] and [3].

#### 2.1 Neutrino sources

Neutrinos are generated by weak interactions either in man-made or natural sources. Due to their very low cross-section, a high flux in combination with large detectors is typically required for their measurement.

The sun produces a high flux of neutrinos via several processes, predominantly via the fusion of protons to helium [19]. The Homestake experiment, which has given first hints towards the neutrino oscillation, detected neutrinos from the sun.

Other naturally occurring neutrinos are generated from cosmic rays in Earth's atmosphere and therefore known as atmospheric neutrinos. Also supernovae are interesting sources, either in the form of a burst of neutrinos which are emitted during an explosion or in form of the flux of all past explosions, the Diffuse Supernova Neutrino Background (DSNB) [19].

In order to investigate neutrinos, dedicated accelerator-based neutrino sources have been designed. An example is the T2K experiment, where a 30 GeV proton bream is used to generated neutrinos which are measured in the far-detector Super-Kamiokande at a distance of 295 km [20].

Another important man-made neutrino source with a very high flux, which are not specifically designed as neutrino sources, are nuclear reactors. During the fission of low-enriched  $^{235}\mathrm{U}$ , the isotopes from  $^{235}\mathrm{U}$ ,  $^{239}\mathrm{Pu}$ ,  $^{238}\mathrm{U}$ , and  $^{241}\mathrm{Pu}$  and their decay chain products undergo decays and generate  $\overline{\nu}_e$  [19, p. 14]. The existence of neutrinos was actually proven by measurements with a nuclear reactor at the Savannah River Plant in 1956 [1]. Since then, several experiments like DoubleChooz, DayaBay or RENO have used reactors to investigate neutrinos and also upcoming experiments as JUNO use them as neutrino source.

#### 2.2 Open neutrino physics questions

There are several open question related to the field of neutrino oscillations. One major question is the ordering of the neutrino masses. The Normal Ordering (NO) refers to the order  $m_1 < m_2 < m_3$ , whereas the Inverted Ordering (IO) refers to  $m_3 < m_1 < m_2$ . From atmospheric and solar neutrino measurements it is known that  $\Delta m_{21}^2 \ll |\Delta m_{31}^2| \simeq |\Delta m_{32}^2|$  [11, p. 301]. Unknown is, whether  $m_3 > m_1$  (NO) or  $m_3 < m_1$  (IO) is realized in nature. A visualization of the two mass orderings is given in Fig. 2.1.

Determining the neutrino mass ordering would unriddle one of the major open neutrino physics questions, and is thus, one of the main focus of the neutrino experiments currently under construction [16, 21]. Knowing the mass ordering helps to define parameters for future experiments like neutrinoless double decay searches. Furthermore, it is a key parameter of the neutrino astronomy and neutrino cosmology [15].

Further open questions are [19]:

- The absolute mass scale of neutrinos

- Exact measurement of the neutrino properties

- CP violation

- Whether neutrinos are Majorana or Dirac fermions

• The number of neutrino generations. From the measurement of the total  $Z^0$  decay width, it is known that there are three light<sup>2</sup> weakly interacting neutrino generations [11, p. 285], but it would be possible that so-called sterile neutrino exist

More comprehensive overviews of open questions are given in [19, 22]. To answer open neutrino physics questions, several new experiments are under construction. The reactor anti-neutrino detector JUNO is one of them, with a focus on the neutrino mass ordering and the precision measurement of neutrino mixing parameters.

$<sup>^2 {\</sup>rm light}$  refers here to a neutrino mass  $m_{\nu} \leq m_{Z^0}/2$  [11, p. 285].

## Chapter 3

## The Jiangmen Underground Neutrino Observatory

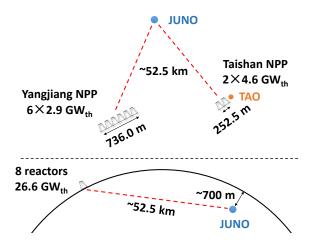

The Jiangmen Underground Neutrino Observatory (JUNO) is a future neutrino detector aiming to solve fundamental open questions in the regime of neutrino physics. The detector is currently under construction in South East China at about 40 km distance to Kaiping city, Jiangmen city, Guangdong province [15, p. 29]. The location is chosen to have an equal distance (baseline) of 52.5 km to the cores of each of two nuclear power plants in Yanjiang and Taishan (cf. Fig. 3.1).

FIGURE 3.1: Relation of JUNO to the nuclear power plants in Yangjiang and Taishan [23]. The Taishan Antineutrino Observatory (TAO) is a detector for measuring a reference anti-neutrino spectrum in a distance of about 30 m from one reactor core [24].

### 3.1 JUNO overview

An overview picture of the experimental site of JUNO and its campus is given in Fig. 3.2. JUNO itself is located underground with an overburden of more than 700 m of rock to shield the detector from cosmogenic background [15, p. 30].

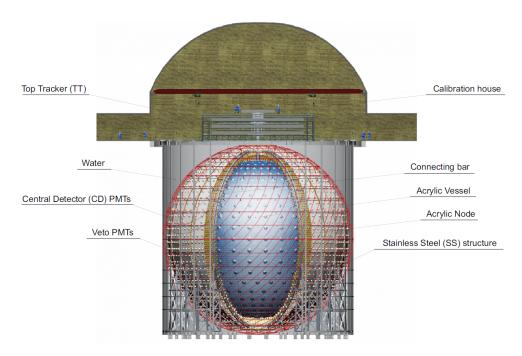

A drawing of the central detector hall of JUNO is shown in Fig. 3.3. The central part of the detector is a spherical **A**crylic **V**essel (AV) with a diameter of 35.4 m holding 20 kt of LS. The AV is instrumented with 17 612 20" PMTs and 25 600 3" PMTs which are also denoted as **C**entral **D**etector (CD) [25]. The expected photo-coverage is more than 75% and it is aimed for an energy resolution of  $< 3\%/\sqrt{E[\text{MeV}]}$  at

Figure 3.2: Image of the JUNO site under construction [23]. The underground facilities can be accessed via the slope tunnel or the vertical shaft.

FIGURE 3.3: Overview of the underground experimental hall [25].

1 MeV [25]. The AV and the PMTs are mounted on a stainless steel support structure which is placed in a cylindrical water pool to shield the detector from radioactivity of the surrounding rock. The water pool is also instrumented with PMTs (Veto PMTs) to detect cosmic ray muons via Cherenkov radiation [18, p. 110]. Additionally, the so-called top tracker is placed on top of the water pool to help with tagging and track reconstruction of cosmic muons.

Further facilities underground are rooms for the electronics, power and the LS purification (LS hall).

#### 3.2 JUNO physics program

JUNO detects the electron anti-neutrinos from the nuclear reactors via the Inverse Beta Decay (IBD) reaction [15]

$$\overline{\nu}_e + p \rightarrow e^+ + n.$$

A positron  $e^+$  and a neutron n are created from the reaction between the electron anti-neutrino  $\overline{v}_e$  and a free proton p. The positron subsequently annihilates with an electron into two 511 keV photons. The neutron loses its energy via scattering and thermalizes. It is captured by a free proton about 200  $\mu$ s later and yields a 2.2 MeV  $\gamma$ -ray [15]. This characteristic coincidence of a prompt (annihilation) and a delayed signal (capture) is used for the event selection. With a total combined thermal power of 26.6 GW from the nuclear reactors, about 60 IBD counts per day are expected [25].

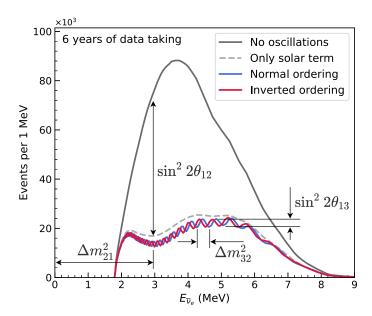

Fig. 3.4 shows a sketch of the IBD energy spectrum. This is a plot of the surviving electron anti-neutrinos as function of their energy (cf. Eq. (2.8)). The mass ordering is visible in the fine structure oscillation. A high energy resolution is required to distinguish the two orderings.

FIGURE 3.4: Visualization of the JUNO IBD energy spectrum after six years of data taking [23]. The dip around 3 MeV corresponds to the solar oscillation term, whereas the fast oscillation corresponds to the atmospheric term.

The IBD measurements can not only be used to determine the neutrino mass ordering, but also for the precise determination of other neutrino mixing parameters. JUNO aims to achieve a precision in the order of 0.5 % to 0.7 % for the parameters  $\sin^2\theta_{12}$ ,  $\Delta m_{21}^2$  and  $\left|\Delta m_{ee}^2\right|$  [15, p. 55]. A comparison of those three parameters with the current best fit values from the combination of experimental data is given in Table 3.1.

TABLE 3.1: Comparison of those oscillation parameters for which JUNO's precision is higher than the combined fit of current measurements. These global fit values are taken from [26]. Data for JUNO are taken from [15, p. 63] and include estimations for systematic uncertainties.

|                         | $\Delta m^2_{21}$ | $ \Delta m_{31}^2 $ resp. $ \Delta m_{ee}^2 $ | $\sin^2 \theta_{12}$ |

|-------------------------|-------------------|-----------------------------------------------|----------------------|

| Global 1σ               | 2.8 %             | 1.3 %                                         | 4.0 %                |

| JUNO expected $1\sigma$ | 0.59 %            | 0.44%                                         | 0.67%                |

Apart from the determination of the neutrino mass ordering and neutrino precision measurements, JUNO has a rich non-oscillation neutrino physics program. Those neutrinos do not stem from the nuclear reactors, but from other sources. Examples are the measurement of low energetic atmospheric neutrinos [27], diffuse supernova neutrino background [28], supernova burst neutrinos [29], geo-neutrinos [30] and searches for dark matter [31]. A comprehensive overview over the physics program is given in [15].

One part of the physics program is the measurement of solar neutrinos. In contrast to IBD events, these do not feature a coincidence signal but correspond to single events [32]. Thus, even lower backgrounds are required compared to IBD measurements.

#### 3.2.1 JUNO Backgrounds

Accidental backgrounds mimic the prompt and delayed events and need to be reduced. The radioactivity from the LS itself is denoted as *internal background*. In contrast, backgrounds from other detector components, the rock, the air, etc. are called *external background*. Several sources of natural radioactive backgrounds like <sup>238</sup>U, <sup>232</sup>Th, <sup>40</sup>K, <sup>226</sup>Ra or <sup>222</sup>Rn can be present in the materials used for the detector [25].

Rigorous effort has been put into the control of radioactivity in JUNO (described in more detail in [25]). It is a key factor to reduce the internal and external backgrounds to reach the required detector performance.

Apart from the careful selection of detector materials, the impact of the external background can be reduced by implementing an (energy dependent) fiducial volume cut. By this, events at the outer shell close to the border of the AV are excluded from the analysis. A fiducial volume cut is not useful for the internal background originating from the LS itself since the signals are distributed uniformly in the sensitive volume [32]. Therefore, the contamination of the LS with radioactive elements has to be minimized to reach the target detector performance.

A multi-step purification plant is installed to remove radioactive contaminants from the scintillator. This includes  $Al_2O_3$  filtration columns (for improving optical properties), distillation (to remove heavy metals and improve the transparency), water extraction (to remove radioisotopes from U/Th chains and  $^{40}$ K), and steam stripping

3.3. *OSIRIS* 13

(to remove gaseous impurities, such as Kr and Rn) [32, p. 19]. Tests with prototype plants have shown that the target contamination limit of  $1 \times 10^{-15}$  g g<sup>-1</sup> for U/Th is within reach [32, p. 19].

In order to verify the efficiency of the purification plant and for monitoring the LS during filling, the dedicated detector OSIRIS is built as last part of JUNO's purification chain [33].

#### 3.3 OSIRIS

The Online Scintillator Internal Radioactivity Investigation System (OSIRIS) is part of JUNO's liquid scintillator filling chain and located underground in the LS hall. As one of the last elements before the inlet to the CD AV it is designed to verify the radiopurity of the LS. Depending on the requirements from different analysis programs, two different limits for the concentration of isotopes of the U/Th decay chain are identified. A limit for the U/Th concentration for IBD-based analyses is set to  $1 \times 10^{-15} \, \mathrm{g \, g^{-1}}$ , and a limit for solar neutrino based analyses is set to  $1 \times 10^{-16} \, \mathrm{g \, g^{-1}}$  [33]. OSIRIS is designed to asses the  $1 \times 10^{-15} \, \mathrm{g \, g^{-1}}$  limit in real-time before filling the detector [25].

#### 3.3.1 Detector design

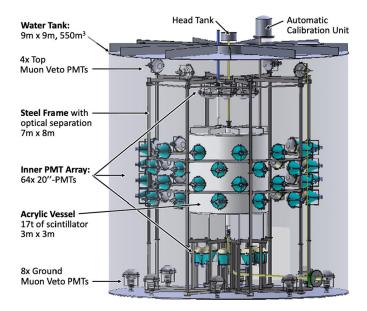

A drawing of the detector is shown in Fig. 3.5. A cylindrical steel tank with a height of 9 m and a diameter of 9 m houses most of the detector elements and the AV which is filled with 21 m<sup>3</sup> LS [33]. This vessel is surrounded by an ultra-pure water buffer for shielding against external radiation. 75 PMTs are placed within the buffer. 64 of them are facing towards the AV and are optically separated from the remaining PMTs. Latter build the muon veto and measure events by detecting Cherenkov radiation in the water buffer. Further parts of the detector like electronics racks are placed on the top of the steel tank.

**Liquid temperatures** OSIRIS is located  $\sim$ 700 m underground where the rock has a temperature of  $\sim$ 31 °C [18, p. 281]. The temperature of the ultra-pure water tank will be cooled to 21 °C which is the target temperature for the LS for the CD. The LS for OSIRIS is preheated to provide layers of LS within the AV due to the temperature induced densities differences. This filling strategy should prevent larger mixing between LS already residing in the AV and new LS.

#### 3.3.2 iPMT system

The light detection system for OSIRIS is a new development called intelligent Photomultiplier Tube (iPMT). These are PMTs with electronics directly attached to their back. For the synchronization of multiple iPMTs, additional electronics is required in form of so-called **S**urface **B**oards (SBs) which are located on top of the steel tank. The SBs provide also trigger signals for the calibration systems. The iPMT system is described in greater detail in Chapter 4.

The PMTs cover  $\sim$ 9% of the full solid angle and provide a light yield of about 280 p.e. MeV<sup>-1</sup> [33, p. 3]. The corresponding energy resolution is assumed as  $\sigma_E \approx 6\% \sqrt{E[\text{MeV}]}$ , whereas the resolution of the three-dimensional vertex reconstruction is expected to be in the order of 24 cm [33, p. 19].

FIGURE 3.5: Overview of the OSIRIS detector [33]. Not all infrastructure on top of the water tank is shown.

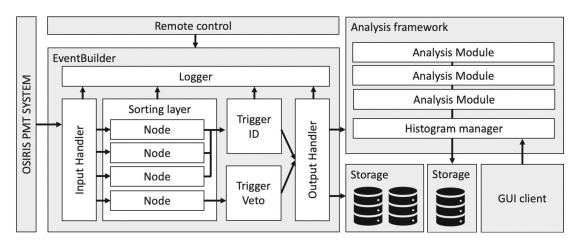

#### 3.3.3 Event Builder

As part of the iPMT concept, the event trigger is implemented purely software based. All iPMTs send their self-triggered hits<sup>1</sup> to a central instance, which is called Event Builder (EB). This software decides which data should be kept for later analysis and which data are discarded. The default trigger mode for the operation of OSIRIS is a coincidence of five PMT hits within a window of 70 ns [33, p. 16].

#### 3.3.4 Calibration systems

OSIRIS features two calibration systems, a *fiber system* and a *source insertion system*. The tasks of the fiber system are the precise calibration of the relative timing and charge of the iPMTs. Therefore, light can be injected from 24 different diffusors into the detector. A laser with a pulselength of 80 ps and a wavelength of 420 nm is used to illuminate the PMTs with very low light intensities [33, p. 12].

The source insertion system is based on the so-called automatic calibration unit (ACU) from the Daya Bay collaboration. It supports up to three sources which can be lowered individually into the detector via a cable. For OSIRIS, a blue LED, a multi-gamma source and a low-activity potassium source are foreseen. The LED can be used for cross-checking the fiber system and for higher light intensities. The multi-gamma source is primarily foreseen for the energy and position reconstruction. The low-activity potassium source will be used to monitor the LS light yield via the decay of <sup>40</sup>K [33, p. 14f.].

Both system are described in more detail in [33, p. 12 ff.].

<sup>&</sup>lt;sup>1</sup>Hits are signals which fulfill selection criteria, like crossing a certain threshold. These signals may be induced by random noise or by impinging light.

3.3. OSIRIS 15

#### 3.3.5 OSIRIS detection mechanisms and sensitivity

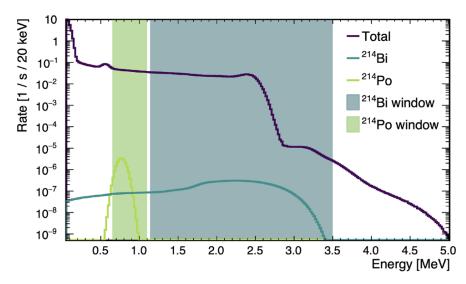

OSIRIS measures the concentrations of uranium and thorium by detecting a coincident decay of isotopes of the respective decay chain. Part of the decay chain of  $^{238}$ U is the isotope  $^{214}$ Bi which decays via  $\beta^-$  radiation into  $^{214}$ Po with a branching ratio of  $> 99\,\%^2$ . It features a broad energy spectrum with an end point energy of about  $3.2\,\text{MeV}$ .  $^{214}$ Po decays with a half life of  $T_{1/2} = (163.46 \pm 0.04)\,\mu\text{s}$  via  $\alpha$  emission into  $^{210}$ Pb. The emitted  $\alpha$  particle has an energy of about  $7.8\,\text{MeV}$ , but the visible energy is reduced to  $0.5\,\text{MeV}$  to  $1\,\text{MeV}$  due to quenching  $^3$  [33, p. 22]. The fast coincidence is denoted as Bi–Po event. A simulation of the  $^{214}$ Bi–Po energy spectrum including energy cut windows, which are used for the event selection, is shown in Fig. 3.6.

FIGURE 3.6: OSIRIS Bi-Po energy spectrum with energy cut windows for <sup>214</sup>Bi-Po [33].

A similar coincident signal is present in the decay chain of  $^{232}$ Th with the  $\beta^-$  decay of  $^{212}$ Bi into  $^{212}$ Po with a branching ratio of  $\sim$ 64 %.  $^{212}$ Po subsequently decays into to  $^{208}$ Pb via  $\alpha$  emission with a half life of  $T_{1/2}(^{212}$ Po) =  $(294.3 \pm 0.8)$  ns.

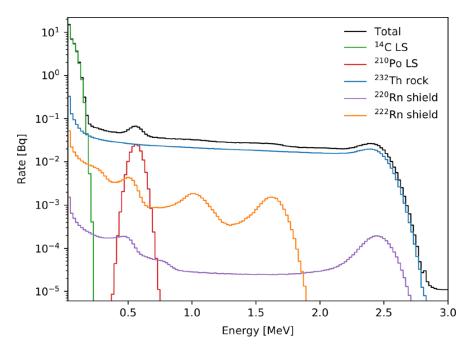

**Backgrounds** Backgrounds for OSIRIS stem from natural and cosmogenic radioactivity. Most radioactive decays produce single events and do not feature a coincident decay as in case of the Bi–Po. Nonetheless, accidental coincidences from single-events have to be considered [33]. Main contributors to OSIRIS backgrounds are <sup>40</sup>K and the isotopes from the <sup>238</sup>U and <sup>232</sup>Th decay chains (especially radon) from the outer detector material and the surrounding rock. A simulation of the total background is given in Fig. 3.7.

**Determination of U/Th abundance** With the assumption of a secular equilibrium, the limit on the mass abundance of  $^{238}$ U/ $^{232}$ Th can be directly calculated from the measured Bi–Po rates [33]. With the presence of radon emanated in the JUNO LS system the assumption of secular equilibrium does not longer hold.  $^{222}$ Rn ( $^{220}$ Rn)

<sup>&</sup>lt;sup>2</sup>These and following nuclear data in this section are taken from [34].

<sup>&</sup>lt;sup>3</sup>Quenching is part of the non-linear response of the scintillator to the ionization density [11, p. 554].

FIGURE 3.7: Energy spectrum of the total background rate [33].

are precursor isotopes of  $^{214}$ Bi ( $^{212}$ Bi) within the respective decay chain, introducing an additional Bi–Po rate superimposed on the Bi–Po events originating from U/Th decays. With relevant half lifes in the order of hours to few days, the isotopes are relatively short lived.

The radon contamination leads to different effective measurement times to reach the required limits depending on the operation mode.

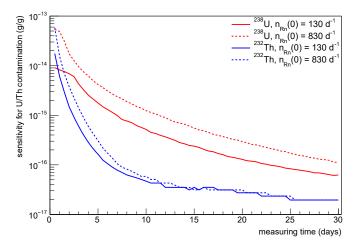

OSIRIS will be used in two operation modes. In the so-called batch mode, OSIRIS is filled with a LS sample and observes this for a time in the order of weeks. With the known decay profile of the radon isotopes, a time dependent fit can be performed. Fig. 3.8 displays the corresponding sensitivity for two scenarios of radon contamination. It takes 7 (2.5) days to reach the  $1 \times 10^{-15} \, \mathrm{g \, g^{-1}}$  limit for U (Th) [33].

FIGURE 3.8: Sensitivity of OSIRIS to <sup>238</sup>U/<sup>232</sup>Th for two different scenarios of an initial radon contamination of 130 and 830 counts per day [33].

3.3. OSIRIS 17

In the continuous operation mode, the LS is constantly replaced with fresh scintillator by feeding it at the top of the AV at an expected rate of about 1 m³ h $^{-1}$ . Thus, the passage of the scintillator through OSIRIS takes almost one day [33]. In this case, the determination of the U/Th contamination requires a more elaborated analysis taking into account the reduction in the decay rates when the LS slowly sinks within the AV. The sensitivity in this mode depends highly on the knowledge of the off-equilibrium radon rate. The expected upper limits are in the range from  $1.4\times10^{-14}\,\mathrm{g\,g^{-1}}$  to  $\sim\!1\times10^{-15}\,\mathrm{g\,g^{-1}}$  and thus close to the IBD limit. A more detailed description of the analysis is given in [33].

## Chapter 4

## Intelligent Photomultiplier Tube System

This chapter gives a detailed description of the iPMT system. The first section motivates the architecture and describes the design goals. The second part introduces shortly the basic principles of PMTs. The remainder of the chapter gives a detailed description of the system with a focus on the electronics design.

#### 4.1 Motivation and Concept

Neutrino detectors instrument typically large volumes, due to the very low cross-section of neutrino interactions with matter. Examples for such detectors are Double-Chooz with a target volume of 2 times 8 t [35], DayaBay with a target volume of 8 times 20 t [36], SuperK with a volume of 50 kt [37] or JUNO with its target volume of 20 kt [15]. Cost efficient devices to cover the large detector surfaces are PMTs. Typically, they have a diameter in the range from 8" (DayaBay [38, p. 17]) up to 20" (SuperK [37, p. 8], JUNO [18, p. 137]).

Due to the dimensions of the detectors, long coaxial cables are typically used to transmit the analog signals from the PMTs to the signal processing electronics. DoubleChooz, for example, used cables with a length of 20 m [35], DayaBay used cables with a length of up to 52 m [38].

The use of long coaxial cable has significant effects on the signal due to attenuation. Table 4.1 gives an overview over typical frequency dependent attenuation values for coaxial cables. The bandwidth required for PMT pulses is typically in the range up to  $\sim$ 400 MHz [39]. These effects becomes more severe with larger detectors. For the so-called external readout scheme for JUNO, coaxial cable length in the range of 80 m to 100 m were assumed [18, p. 223], which would result in an attenuation as given in Table 4.1. The frequency dependent attenuation leads also to a dispersion resulting in a pulse distortion and reduction in amplitude [40]. This effect can become especially important at low signal levels close to the noise floor.

In order to mitigate problems with long analog cables, a concept with digitizing and processing electronics directly attached to the PMT has been developed. They are named intelligent PhotoMultiplier Tube (iPMT), expressing the goal to design a system around a conventional PMT with a higher degree of integration and advanced functionality. The expression "intelligent PMT" has originally be coined for this concept for the JUNO central detector [18, p. 210ff.]. It has been developed as one of the possible readout schemes for JUNO, but has not been chosen as final scheme [39].

Table 4.1: Cable attenuation for different coaxial cables for a length of 100 m. RG303 has been used in DoubleChooz [35]. 609C5019A is a cable which has been evaluated for an external readout scheme for JUNO [18, p. 223]. Aircell 7 is a dedicated low-loss cable, but not suited for PMT's operating high voltage. An attenuation of 3 dB (10 dB) corresponds to an attenuation of the amplitude from 100 % to  $\sim$ 71 % ( $\sim$ 32 %) (using: attenuation [dB]=  $20 \cdot \log_{10}(V_{\rm rx}/V_{\rm tx})$  with the initial amplitude  $V_{\rm tx}$  and the recorded amplitude  $V_{\rm rx}$ ).

| frequency [MHz] | RG303 <sup>[71]</sup> [dB] | 609C5019A <sup>[18, p. 223]</sup> [dB] | Aircell 7 <sup>[72]</sup> [dB] |

|-----------------|----------------------------|----------------------------------------|--------------------------------|

| 50              | 9                          | -                                      | 4.29                           |

| 100             | 13                         | 12.3                                   | 5.97                           |

| 200             | 19                         | 17.7                                   | 8.59                           |

| 300             | 24                         | -                                      | 10.64                          |

| 400             | 28                         | -                                      | -                              |

A solution with short cables (about 1 m) to a dedicated box for digitization and processing for three PMTs is used for JUNO instead [25].

The idea of the intelligent PMTs is implemented in OSIRIS as described in Section 3.3 but with a complete redesign of the electronics. The concept aims for

- high Signal-to-Noise-Ratio (SNR) by mounting the electronics directly on the PMT pins

- use of the dedicated PMT readout Application-Specific Integrated Circuit (ASIC) VULCAN with advanced functionality

- implementation of performance improving algorithms at device level

- easily deployable system with standalone detector units

- use of commercial electronics for power distribution and system level trigger to profit from cost reduction in highly competitive markets

Further design goals of the iPMT are based on the requirements for OSIRIS. This has the consequence of partially relaxed requirements compared to JUNO, especially regarding reliability due to the shorter expected run-time of OSIRIS. Several aspects are taken into account for the design of the iPMTs, covering requirements from physics, system integration and mechanics.

**Physics requirements** The SNR should be on a level that the signals on single p.e. level (cf. Section 4.2) are clearly resolved and that the trigger threshold can be chosen such that those events are recorded. Large signals should be measurement with a lower resolution for signals up to several hundred p.e. The time resolution should be such that the PMT Transit Time Spread (TTS)  $\sigma_{\text{TTS}}$  (which is in the order of 1 ns to 1.5 ns, cf. Fig. A.1b) is the dominant contributor.

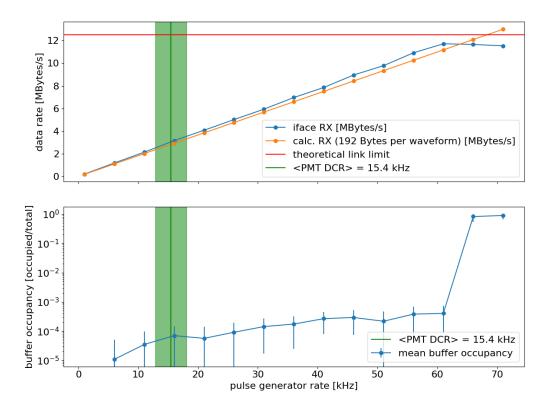

**System requirements** The data transmission capability of the system should be sufficient to transmit waveforms with a rate of the **D**ark **C**ount **R**ate (DCR) (cf. Section 4.2.1) of the PMTs plus a reasonable margin to the EB of OSIRIS (cf. Section 3.3.3).

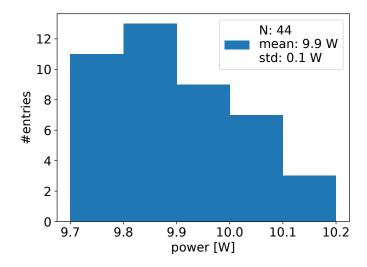

Since the water buffer of OSIRIS is kept at a temperature of 21 °C [33], heat which is produced by the iPMTs in the water buffer has to be removed. Thus, the power per channel should be on a reasonable level, which is for JUNO considered to be in the order  $\approx$ 10 W [39, p. 2].

**Mechanical requirements** Since the iPMT electronics is mounted at the back of a PMT (cf. Fig. 4.2) the design aims for a diameter in the order of the PMT neck diameter. With a glass diameter size of about 7.5 cm close to the signal pins, the **Printed Circuit Board** (PCB) diameter was chosen to 10 cm.

#### 4.2 Photomultiplier tubes

Since the iPMT is built around a PMT, a brief overview of relevant general PMT properties is given in this section.

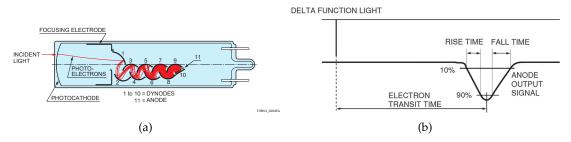

**Working principle** PMTs are very sensitive light detectors which are able to resolve signals ranging from single photons up to few thousand photons. A sketch of the working principle is given in Fig. 4.1a. An impinging photon is converted via the photoeffect in the photocathode into an electron. The electron is accelerated and focused towards the first dynode. Through secondary emission of electrons by the dynodes, further electrons are generated and an electron avalanche builds up [41]. The output signal of the PMT is the electron avalanche at the anode which can be measured as a current. The charge which corresponds to the signal of a single photon is denoted as single photon electron equivalent, short 1 p.e. (or single p.e.).

#### 4.2.1 PMT properties

The PMT properties which are of most relevance for this thesis are given in the following, more detailed information can be retrieved in [41].

**Dark count rate** Signals on single p.e. level are generated in a PMT even without illumination. This effect is called dark current, respectively dark count. It occurs mainly due to thermal emission of electrons from the photocathode or dynodes, which are subsequently amplified like electrons generated by impinging photons. The term **D**ark **C**ount **R**ate (DCR) refers to the signal rate for a certain threshold, often chosen to 50% of the mean single p.e. amplitude.

**Transit Time Spread** The transit time denotes the time between the generation of a photo electron at the cathode and the signal output at the anode. More relevant for the detector is the variation in the transit time, which is denoted as Transit Time **S**pread (TTS). For the PMT type used for OSIRIS, the TTS is in the range of 1 ns to 1.5 ns (cf. distribution in Fig. A.1b<sup>1</sup>).

<sup>&</sup>lt;sup>1</sup>Fig. A.1b states the TTS in terms of the Full Width Half Maximum (FWHM). This can be converted into a standard deviation under the assumption of a gaussian TTS with  $\sigma_{TTS} = \text{FWHM}_{TTS}/(2\sqrt{2\ln 2})$ .

FIGURE 4.1: (a) Sketch of a PMT cross section [41]. (b) Definition of transit time, rise time and fall time [42].

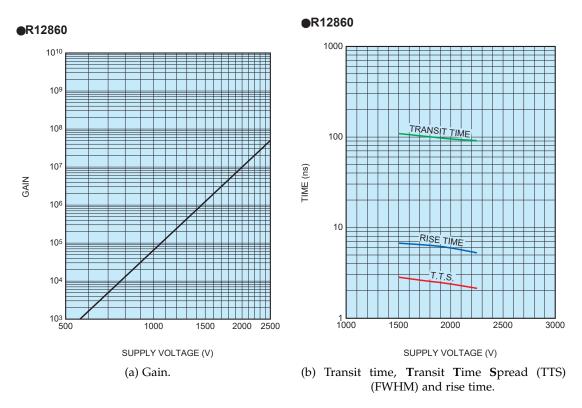

**Gain** The gain is defined as the current at the anode over the photoelectron current from the photocathode [41, p. 48 f.]. An alternative name for gain is therefore "current amplification". The gain *g* of a PMT is highly dependent on the applied high voltage and can be approximated by

$$g = A \cdot V^{kn} \tag{4.1}$$

with the applied high voltage V, with the constants A, k being determined by the structure and material of the PMT and n, the number of dynodes [41, p. 48f.]. In Fig. A.2a the gain vs. voltage curve is shown, a gain of  $1 \times 10^7 e \, e^{-1}$  is the nominal gain for the PMT type used in OSIRIS.

**Rise and fall time** The rise time of a PMT signal is defined as the time difference between reaching 10 % and 90 % of the amplitude as depicted in Fig. 4.1b. Accordingly, the fall time is defined as time from 90 % to 10 % of the peak pulse height. The rate of change of the signal puts certain requirements on the readout electronics in term of the bandwidth. Most relevant parts of the signal are expected in a frequency range up to  $f = 1/T_{rise}$  with the signal rise time  $T_{rise}$  [40]. The typical rise time for *Hamamatsu* 20" PMTs is 6 ns [73], corresponding to  $f \approx 170 \, \text{MHz}$ .

Hamamatsu PMT R15343 OSIRIS uses high-quantum efficiency PMTs of the type *Hamamatsu* R15343 which are identical to the type R12860 [43, 33, p. 93]. The PMTs have ten dynodes, which are arranged in a box and line structure [73]. Table 4.2 lists the properties of the type R12860.

#### 4.3 iPMT mechanics overview

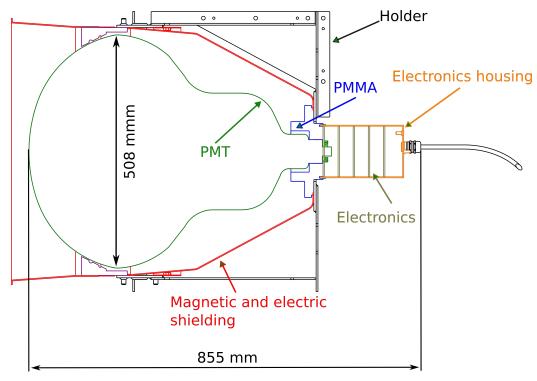

Fig. 4.2 shows a drawing of the main elements of an iPMT. The PMT is surrounded by an electromagnetic shielding consisting of alumina foils and amorphous metal. A PMMA (Polymethylmethacrylat) ring is glued to the PMT and the ring is screwed to a stainless-steel holder. On the backside of the PMT, a stack of electronic PCBs is soldered on the pins (electric connectors) of the PMT. This stack is described in detail in Section 4.4. It is encapsulated in a stainless steel shell, which is glued to the PMMA ring. The procedure of gluing all components onto the PMT is referred to as *potting*. For a better heat transfer, the shell is filled with mineral oil. A detailed description of the potting procedure is given in [44].

TABLE 4.2: Properties of the PMT type R12860. For the OSIRIS PMTs, the distribution of the nominal voltages is given in Fig. A.1c and a distribution of the TTS in Fig. A.1b.

| property                             | value                        |

|--------------------------------------|------------------------------|

|                                      |                              |

| diameter                             | 508 mm                       |

| weight                               | approx. 8 kg                 |

| typical quantum efficiency at 390 nm | 30 %                         |

| typical gain                         | $1 \times 10^7 \mathrm{e/e}$ |

| voltage for typical gain             | 2000 V                       |

| typical rise time                    | 6.0 ns                       |

| typical TTS (FWHM)                   | 2.4 ns                       |

FIGURE 4.2: Sketch of an iPMT including the holder for mounting in OSIRIS. Drawing provided by Cornelius Vollbrecht.

#### 4.4 iPMT electronics stack

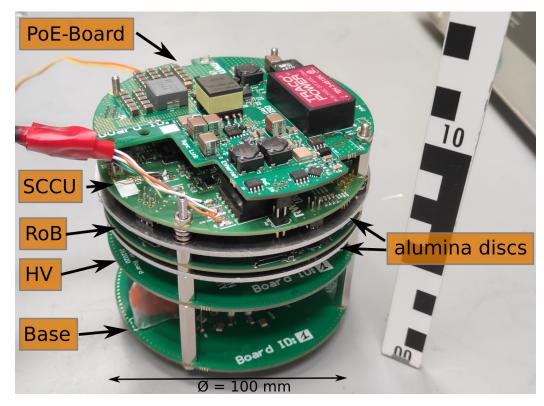

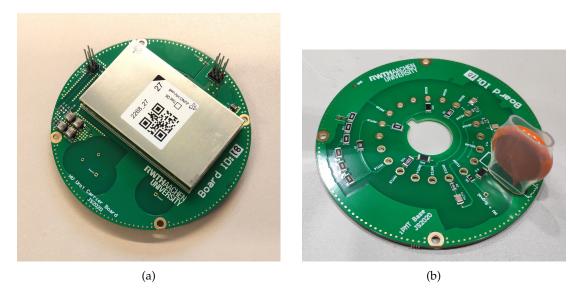

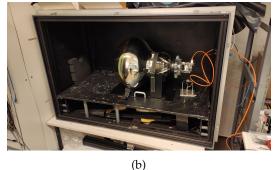

This section explains the electronics parts of an iPMT. Fig. 4.3 gives an overview of an assembled electronics stack. It consists of five boards with a diameter of 10 cm each. The development of the electronics was done by the working group under the leadership of Jochen Steinmann. Drawing the schematics and the PCB layouts have been done by Jochen Steinmann, whereas the work of this thesis concentrated on the debugging, testing and validation of the designs. The iPMT electronics stack consists of the following boards, which are abbreviated based on their functionality as following:

- **PoE-Board** The abbreviation PoE stands for **Power over Ethernet**, a standard for transmitting power via twisted-pair cables. Since this technique is used on the board, it is referred to as **Power over Ethernet** (PoE)-Board.

- SCCU-Board The Slow Control and Configuration Unit provides interfaces to other components and manages readout and control of sensors (also known as "Slow Control").

- **Readout-Board** Main tasks of the **Readout Board** (RoB) are the PMT signal digitization (readout) and processing.

- **HV-Board** The HV-Board provides **High Voltage** (HV) for the PMT. The typical PMT supply voltage for the used type is in the order of 2000 V.

- **Base-Board** The PMT requires certain voltages being applied to the pins which are connected to the different dynodes. The supply voltage from the HV-Board is divided into the required voltages on this board.

#### 4.4.1 Connectivity

The iPMT features a single CAT5e cable as power and data connection. The cable contains 4 twisted-wire pairs with an alumina foil based shielding for each pair. A braided shield encloses all wires. As measure against the propagation of water along the cable in case of a cable damage, a water-blocking powder is included. The outer jacket consists of high-density polyethylene (HDPE), which is used for its compatibility with ultra-pure water. The assignment of the wire pairs is shown in Table 4.3. Pairs 1 & 2 implement standard 100 Mbit Ethernet combined with PoE. Pairs 3 & 4 are used for synchronous transmission between the SB and the iPMT. The SYNC RX connection provides a dedicated data stream with an embedded 125 MHz clock signal for the synchronization of the iPMT (sync data stream).

The length of the cable varies depending on the mounting position within OSIRIS. For iPMTs mounted at the top of the detector the cable length is 17 m, for those at the center ring 22 m and iPMTs at the bottom have 25 m long cables [33, p. 12].

#### 4.4.2 PoE Board

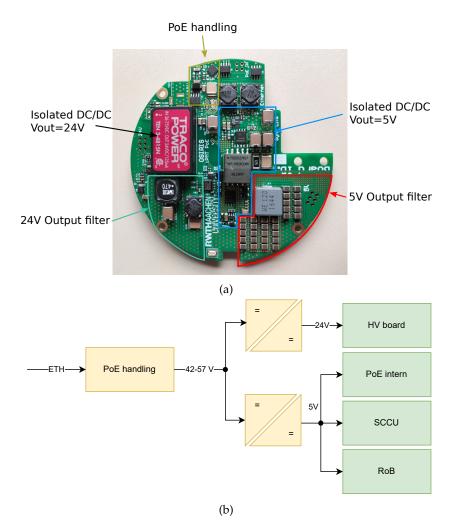

This board implements handling of the PoE protocol and subsequent conversion of the voltage from the PoE level to 24 V and 5 V. A picture of the board is shown in Fig. 4.4a with a highlighting of different functional blocks. PoE is a standard which defines the power delivery of twisted-wire pairs used in Ethernet communication. This board

Figure 4.3: Assembled electronics stack. Alumina discs are placed above and below the RoB for better heat transfer. The black/white divisions on the folding rule have a width of 1 cm.

TABLE 4.3: Wire pair assignment of the iPMT CAT5e cable.

| pair | name    | function                                      |

|------|---------|-----------------------------------------------|

|      |         |                                               |

| 1    | ETH RX  | asynchronous receive and power over ethernet  |

| 2    | ETH TX  | asynchronous transmit and power over ethernet |

| 3    | SYNC TX | synchronous transmission to SB                |

| 4    | SYNC RX | synchronous receive from SB                   |

implements the standard 802.3at-2009 PoE, also known under the name PoE+ by using commercially available Integrated Circuits (ICs). Two twisted-pairs are required for the power delivery. The voltage is in the range from 42.5 V to 57 V. The standard defines different classes of devices with varying delivered power. The iPMT is defined as a so-called Class 4 device, which would allow a maximum delivered power of 25 W. The next lower Class 3 allows for a maximum power of 12.95 W which has been considered as too limited. However, the power required by an iPMT is with about 10 W much lower and furthermore limited by the maximum power of the internal converters<sup>2</sup>

The PoE voltage has to be converted according to the requirements of the different components on the different boards. In a first step this is done by using an isolated DC/DC converter which converts the PoE input voltage to 5 V (denoted as 5 V DC/DC in the following). Other boards implement further conversion steps to e.g., 3.3 V, 2.5 V or 1 V as required on each board. A structural overview is given in Fig. 4.4b.

## 4.4.3 SCCU - Slow control and configuration unit

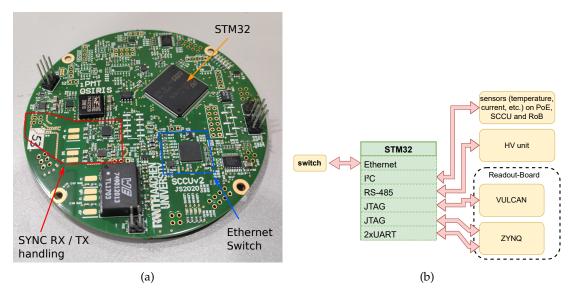

The Slow Control and Configuration Unit (SCCU) is the central communication interface of the iPMT. This board hosts a 4-port Ethernet switch (3 ports are used) to connect the Ethernet uplink with the RoB and with a microprocessor on the SCCU. This microprocessor is a STM32 IC which is based on an ARM Cortex CPU (cf. Fig. 4.5a).

The firmware for this chip has been written by Tim Kuhlbusch. It is stored on an internal 512 KiB flash memory. Changing the firmware of the STM32 after potting of the iPMT is not possible. Therefore, the firmware has been improved and verified over more than two years to ensure a correct operation.

The SCCU is used to interface to other system components (also on other PCBs) and provide access to these components via Ethernet (visualized in Fig. 4.5b). Thus, the SCCU acts as protocol translator between different (hardware) protocols and Ethernet. This includes the following protocols:

- Inter-Integrated Circuit (I<sup>2</sup>C) to PoE, SCCU, RoB (via a custom User Datagram Protocol (UDP)<sup>3</sup> based protocol)

- Joint Test Action Group (JTAG) connection to VULCAN and ZYNQ (via Xilinx Virtual Cable protocol [74])

- Universal Asynchronous Receiver Transmitter (UART) to the ZYNQ (via a telnet like protocol)

- EIA-485 to the HV module (same protocol as UART)

$<sup>^2</sup>$ The maximum input power of the 5 V converter is up to  $\sim$ 16 W. Additionally, the 24 V converter would be able to deliver up to 3 W. However, since this converter only supplies the HV module for the PMT, the load is rather stable and limited by the maximum PMT HV setpoint. A typical input power of the 24 V converter is 0.8 W (cf. Table 6.1).

<sup>&</sup>lt;sup>3</sup>a simple connectionless communication protocol without error checking and corrections.

Figure 4.4: (a) PoE-Board with functional blocks labeled. (b) Overview of the power distribution.

FIGURE 4.5: (a) SCCU PCB design with important components highlighted. (b) The STM32 IC on the SCCU provides access to different components via Ethernet by interfacing their respective protocol. VULCAN and the ZYNQ are described in Section 4.4.4.

#### 4.4.4 Readout Board (RoB)

The central components for the digitization and processing of the PMT data are placed on the RoB. Since this boards contains components which are crucial for the understanding of the system, they are described in detail in the following sections.

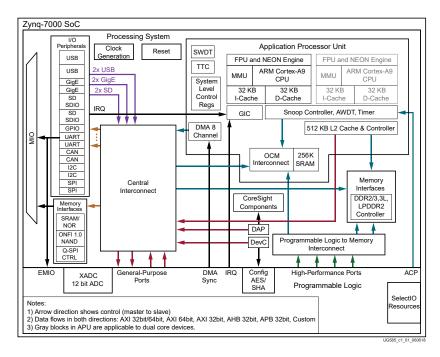

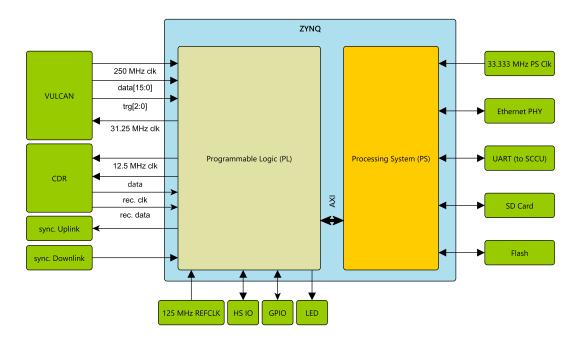

**ZYNQ** The central component of the RoB is a Xilinx XC7Z020. This device is a so-called **S**ystem-**o**n-a-**C**hip (SoC). An SoC integrates a number of functional blocks on one chip. For the XC7Z020 a dual-core ARM A9 Cortex processor is combined with an FPGA from the Artix-7 family of Xilinx. This allows to implement functionality as "hardware" in the FPGA part of the SoC, as well as in software, which is executed by the dual-core processor. In the following, the term **P**rogrammable **L**ogic (PL) is used as name for the FPGA part of the ZYNQ (cf. Fig. 4.7) and **P**rocessing **S**ystem (PS) denotes the dual-core processors. An overview of further functional blocks which are available in the SoC is given in Fig. 4.7. Only a selected functionality is used by the iPMTs. This includes:

- I<sup>2</sup>C

- UARTs

- SD card (for debugging purposes only)

- 100 Mbit Ethernet

- DDR3 RAM

- XADC for monitoring of the supply voltages and temperature

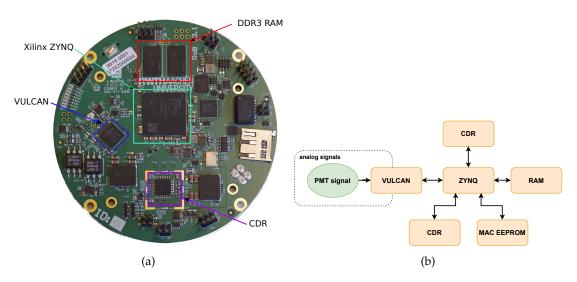

FIGURE 4.6: (a) RoB with different highlighted components. An explanation of the components is given in Section 4.4.4. Design partially supported by ZEA-2. (b) Overview of building blocks of the RoB.

FIGURE 4.7: Overview of the Zynq-7000 functional blocks [75, p. 27].

**DDR3 RAM** In total 8 Gbit of DDR3 memory (2 ICs with each 4 Gbit) are used in the design. RAM is required by the **O**perating **S**ystem (OS) which is executed on the PS as well as for short term memory for the storage of PMT data.

**MAC EEPROM** The design hosts a memory (Electrically Erasable Programmable Read-Only Memory (EEPROM)) with a pre-configured EUI-48 node address (also known as MAC address) in a non-writable section. These kind of addresses are used to identify devices in networks. For the iPMT, the address is used to uniquely identify the RoB (the SCCU hosts a dedicated EEPROM for their identification). The address is read during the boot stage (cf. Section 5.6) and subsequently used for network communication.

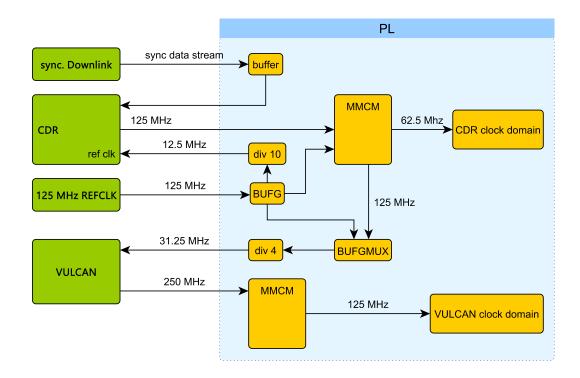

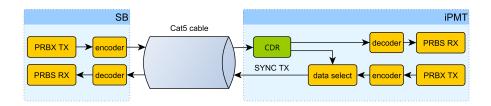

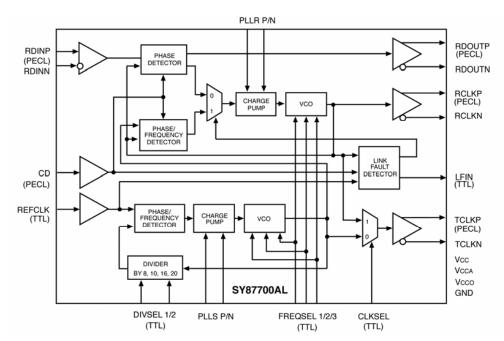

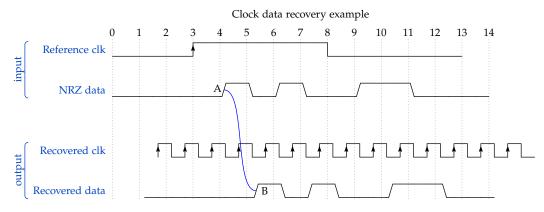

CDR An important IC is the Clock and Data Recovery (CDR) chip. The used device is a *Micrel SY87700AL*. From an input data stream it generates a clock ("recovered" clock) with the same frequency as the bit rate of the data stream. A copy of the input data stream and the "recovered" clock, which is properly aligned with the data stream, are sent out. This allows for the transmission of a clock signal and a data signal over one transmission line. For the iPMTs, this enables an efficient use of the four wire-pairs (cf. Table 4.3). It allows for having a synchronous uplink connection (from the iPMT to the SB) instead of having two downlinks, which would be otherwise required for clock and data transmission. A more detailed explanation of the data stream is given in Section 5.4.2, whereas details of the CDR functionality are given in Appendix C.

**Reference clock (REFCLOCK)** A crystal oscillator *Silicon Labs Si530* is part of the design to serve as low-jitter clock, especially as reference for the CDR. It has a fixed frequency of 125 MHz.

#### **VULCAN**

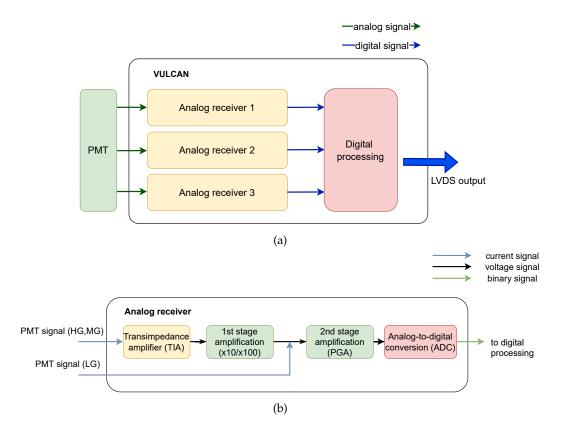

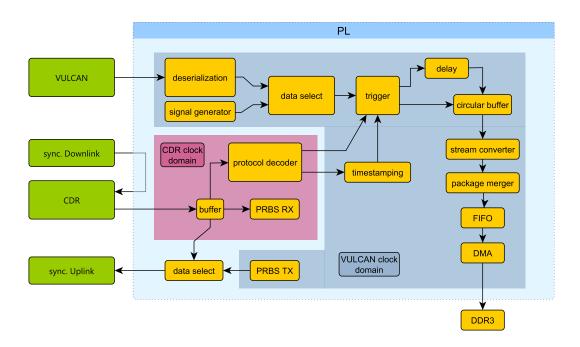

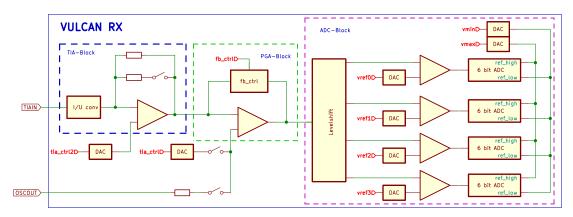

The readout board features a highly integrated receiver chip for PMTs with the name VULCAN. It has been developed by the central institute of engineering, electronics and analytics (ZEA-2) of the Forschungszentrum Jülich. Foreseen to be used as part of the readout electronics of the JUNO detector, it is designed to fulfill the requirements given in the JUNO conceptual design report [18, p. 193 ff.]. The objective of this receiver chip is the digitization and processing of the PMT signal.

A challenge for the digitization is the wide dynamic range range from sub single p.e. to few thousand p.e. with the required time resolution using only one Analog-to-Digital Converter (ADC). In order to overcome this problem, some experiments have used parallel digitization of the output signal with two different gains [45, 46]. Also the JUNO central detector electronics scheme is designed with two gains [47]. The concept of using two simultaneous sampling tracks is extended by VULCAN to three tracks (Fig. 4.8a), which are denoted as RX (receiver).

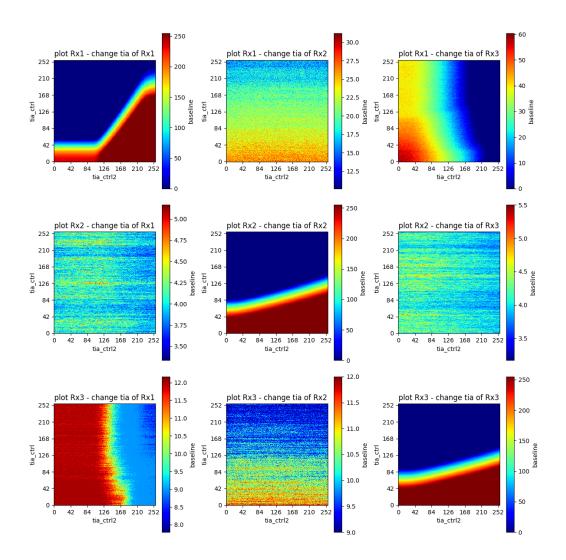

The chip is highly configurable, featuring in total 329 register. 80 of them are so-called status register, which are connected to status information of sub-modules and read-only. 249 registers are used for configuration of the different modules in the design.

**Interfaces** VULCAN provides a JTAG interface for the access to the aforementioned registers, it is connected to one JTAG port on the SCCU. For the data transmission, VULCAN implements in total 20 Low Voltage Differential Signaling (LVDS) lines, which are divided into 16 ADC sample lines, three trigger lines and one clock signal. They are used to interface with the FPGA (cf. Section 5.2.4).

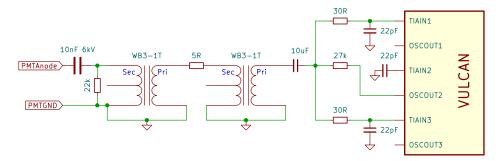

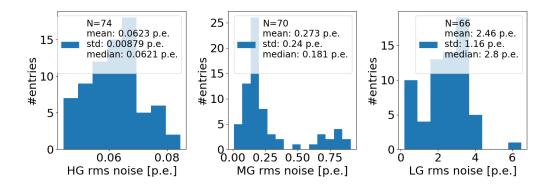

**Input section** Each RX features a transimpedance amplifier, a subsequent amplifier stage and an 8 bit ADC (Fig. 4.8b). The configuration of each RX is independent from the other RX. Thus, different amplifications for the individual RX can be configured to achieve the desired dynamic range. The RX are named by the configured amplification: The receiver with the highest amplification is denoted as **High Gain** (HG), the next lower amplification as **Mid Gain** (MG) and the lowest one as **Low Gain** (LG). Design values for the covered ranges and the corresponding precisions are given in Table 4.4. The connection of VULCAN to the PMT and the VULCAN configuration are described in Section 6.3.1.

TABLE 4.4: Design values for the range and precision of the three VULCAN receiver tracks [48, p. 14].

| receiver name | range               | precision |

|---------------|---------------------|-----------|

| HG            | 0 p.e. to 10 p.e.   | 0.1 p.e.  |

| MG            | 0 p.e. to 100 p.e.  | 1 p.e.    |

| LG            | 0 p.e. to 1000 p.e. | 10 p.e.   |

**Signal processing** VULCAN is a highly integrated receiver chip which also implements data processing and is not a pure ADC. Therefore, the data from the three ADCs are internally transferred to a dedicated data processor. Transmitting the data from the three ADCs to an other chip like the FPGA would require a very high-throughput connection with a high number of parallel data-lines and/or with very high speeds. Since the simultaneous transmission of data from all three ADCs is not required, it has been decided to implement only the transmission of one ADC output at the same time [48, p. 46]. This is denoted as *data selection*.

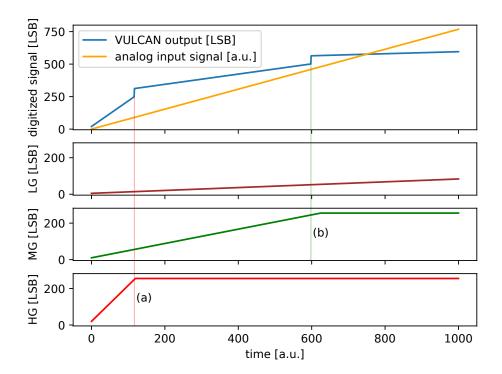

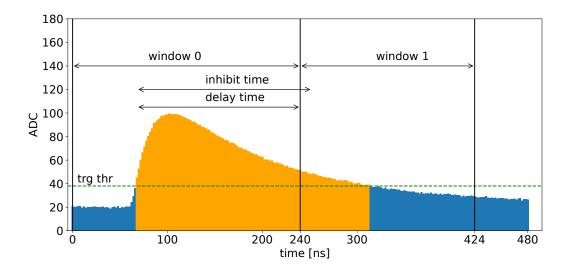

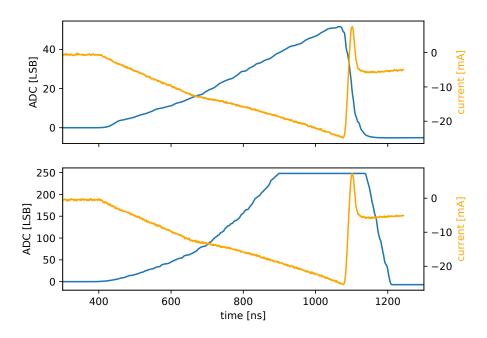

**Data selection** The data selection algorithm is implemented in the data processor of VULCAN. It is designed to select and transmit data from the RX which provides the highest resolution. An exemplary visualization of the data selection process is given in Fig. 4.9.

The selection process works roughly in the following manner: Data are selected from the HG RX as long as they are below or equal to a configurable upward switching threshold. If the ADC data cross the threshold, data are selected from the MG RX. The same logic applies for the transition from the MG to LG RX, but with a dedicated threshold. In order to prevent fast switching between the different RX if the data are close to the switching threshold, a hysteresis is implemented. When data are readout from the MG (LG), data in the HG (MG) have to fall below another configurable downward switching threshold to be selected. A detailed explanation of the algorithm is given in [48, p. 48ff.].

FIGURE 4.8: (a) Overview of VULCAN building blocks. (b) Scheme of one VULCAN receiver block.

The assignment of the physical receiver chain to its function as HG, MG or LG can be configured. Furthermore, it is possible to prevent switching to other receiver chains by setting a switching threshold of 255. The combination of those configuration options allows also the readout of a single RX, which is especially helpful for debugging purposes and for understanding the system response.

VULCAN can be configured to use the three trigger lines for decoding the source RX from which data were selected in terms of HG, MG and LG (i.e. not the RX number is decoded but the gain). The 16 data lines transmit two 8 bit samples from the same ADC. Thus, the data selection selects the ADC as source which provides the highest resolution for both samples. If a switching between ADCs would fall in between those samples, data would be selected from the ADC with the lower resolution.

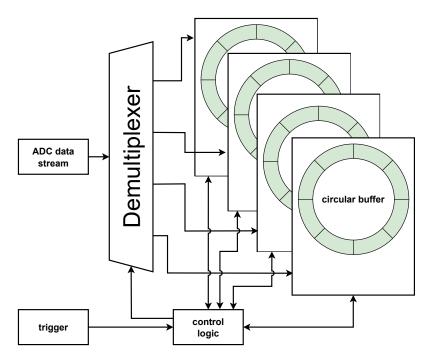

Further data reduction mechanism are implemented in VULCAN, including the intermediate storage of data within a circular buffer and the suppression of noise ([49], [48, Chapter 5]). These modes are not used in this thesis. Selected data are transmitted via LVDS lines to the FPGA without further processing.

**Time resolution** The IC is originally designed for sampling rates up to  $1 \, \text{GS s}^{-1}$  [50], which is based on the JUNO design requirements [18, p. 197ff.]. For the iPMTs, VULCAN is configured with a sampling rate of 500 Msps, since the chip is not validated for the full sampling rate.

FIGURE 4.9: Visualization of the data selection within VULCAN for a HG to MG gain ratio of 5 and a MG to LG gain ratio of 5. Each receiver has an individual baseline level which are set here to 20 for the HG, to 10 for the MG and to 5 for the LG. The upper plot depicts the output of the data selector with the most significant bits decoding the source receiver (0 LSB to 255 LSB: HG, 256 LSB to 511 LSB: MG, 512 LSB to 767 LSB: LG). Data are selected from the HG receiver as long as the HG upward switching threshold (250 LSB) is not crossed. Switching to the MG receiver is done at (a). Subsequently data are selected from the MG RX until the MG upward switching threshold of 245 LSB is crossed at (b).

**Bandwidth** The input bandwidth for VULCAN is determined by the requirements from PMT signals. VULCAN is designed for a bandwidth up to 500 MHz, to provide a fast rise time of pulses and accurate pulse shaping [51, p. 10f.].

**Input impedance** The transimpedance amplifier determines VULCAN's input impedance. It has a design value for the combined input impedance of about  $10\,\Omega\parallel10\,\Omega=5\,\Omega$  (cf. Section 6.3.1).

**Phase-locked loop (PLL)** An analog phase-locked loop frequency synthesizer has been designed for VULCAN with a focus on low noise, low jitter and high reliability [51, 52, 53, 54]. It provides the internal clocks for the ADC and the digital part of VULCAN as well as the LVDS output clock. The control voltage of the PLL is connected to an XADC input of the ZYNQ. This is useful for debugging purposes and checking the configuration of the PLL. The control voltage output is disabled per default to avoid effects on the PLL and has to be enabled via the configuration.

#### 4.4.5 HV and Base

Electronics for providing the correct voltages for the PMT operation are spread over the HV Board and the Base. The HV Board hosts the HV module (cf. Fig. 4.10a) and passes the PMT signal through to the RoB.

**HV module** The HV module is a dedicated module for generating an output voltage up to 3000 V from an input voltage of 24 V. A microcontroller is integrated into the module for monitoring and control of the high voltage. Communication to the HV module is done via a EIA-485 interface connected to the SCCU. Key parameters of the module are given in Table 4.5. The module has been developed by members of the JUNO collaboration under the leadership of JINR Dubna, Russia.

parametervalueinput voltage24 Voutput voltage range800 V to 3000 Vmaximum output current300 μAoutput ripple~10 mV

TABLE 4.5: Parameters of the HV module [39].

Furthermore, a high voltage capacitor with a capacitance of 10 nF is used to eliminate the high voltage **D**irect **C**urrent (DC) component for subsequent circuits (this capacitor is called *coupling capacitor* in the following). It is required since the photo cathode is on ground potential, which results in a positive high voltage for the anode. This scheme is typically used to have a single cable for the high voltage and PMT signal transmission [38, p. 18], [18, p. 59]. An alternative scheme would be the use of negative high voltage for the cathode (also called anode grounding scheme). This would have the disadvantage, that when grounded material like magnetic shieldings are in close contact to the photo cathode, electrons would be attracted to this ground potential, leading to an increase in noise [41, p. 87].

FIGURE 4.10: (a) High voltage carrier board. The HV module is covered with an alumina casing. (b) Voltage divider circuit for the PMT.

**Base** The Base Board is supplied with the positive high voltage from the HV module on the HV board. A voltage divider-circuit is implemented, based on the recommendation from *Hamamatsu*. Fig. 4.10b depicts the final version of the base.

## 4.5 Surface Board electronics

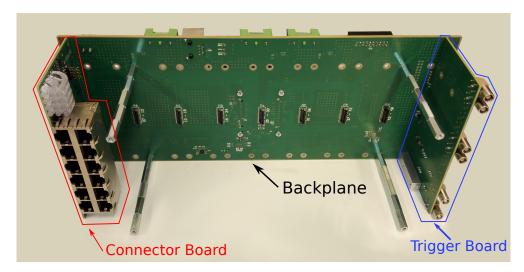

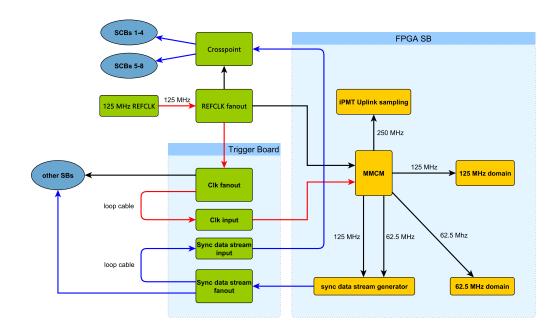

As described in Section 4.6 the **S**urface **B**oard (SB) is required within OSIRIS for timing and synchronization purposes. The name derives from the fact that they are located on top of the OSIRIS steel tank, opposed to the iPMTs located inside the tank.

The SB acts as a backplane for up to nine modules. One module slot is dedicated for the so-called Trigger Board (TB). The other eight slots can be filled with Surface Connector Board (SCB). Fig. 4.11 depicts a SB with a plugged Trigger Board (TB) and a SCB.

**Surface Board Backplane** The central element of the SB is a SoC module from *Trenz Electronic* (type TE0720-03-1CF). It features a Xilinx XC7Z020 SoC as it is used for the RoB (cf. Section 4.4.4), 1 GB DDR3-Random Access Memory (RAM), a 1 Gbit Ethernet connection and a 32 MB flash memory. The FPGA of the SoC connects to the slots for the Trigger Board and SCBs. A 125 MHz crystal oscillator (*Silicon Labs Si530*) is available as reference clock source (same type as on the RoB).

**Trigger Board** The Trigger Board is used as interface to the calibration systems and for the clock and sync data stream distribution between SBs. It provides the following connections:

- 1x High-speed differential clock input

- 4x High-speed differential clock output

- 1x High-speed differential data input (for sync data stream)

FIGURE 4.11: Image of a Surface Board backplane with a single SCB and a TB. The TB has not all connectors placed which are required for final operation (only one clock output and one data output are populated).

- 4x High-speed differential data output (for sync data stream)

- 2 x 2 single ended trigger outputs

The clock outputs are used to distribute a clock signal from one SB to other SBs. The outputs provide all the same signal by utilizing a dedicated clock buffer, which creates copies of the clock signal with a well controlled jitter. The same applies for the differential data outputs for the sync data stream.

The trigger outputs are arranged in two pairs. Each pair receives a dedicated signal from the FPGA and a dedicated buffer is used to create copies of the signal for the two outputs of this pair. It is possible to configure each output either with 3.3 V or 5 V level.

**Surface Connector Board** Each SCB provides connections for up to six iPMTs. Two RJ45 connectors per iPMT are used. One socket directly connects to the iPMT. It provides the synchronous connections via the SCB (SYNC RX and SYNC TX, cf. Table 4.3) and the asynchronous connection which is passed through from the second RJ45 connector (ETH RX and ETH TX). This second socket is connected with a PoE switch to provide power and a network connection to the iPMT.

# 4.6 Timing system within OSIRIS

This section describes several aspects of the iPMT concept which are relevant for its use within OSIRIS as detector system. A description of the requirements is followed by an explanation how it is implemented.

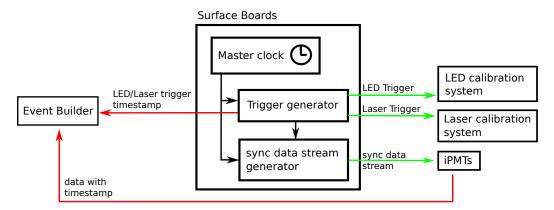

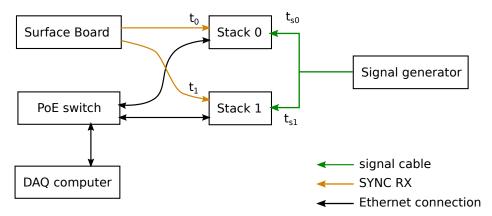

**Timing system** In order to synchronize the data from the iPMTs and the calibration systems within OSIRIS, a timing system is required. This system is based on timestamps which are used to tag the information from the iPMTs and the calibration systems. A timestamp is a 64bit integer number providing nanosecond resolution.

The upper 32 bit are used to store a UNIX-timestamp. The lower 32 bit state the nanoseconds within the second.

The information which need to be tagged with a timestamp are:

- 1. the trigger for the LED and Laser calibration system.

- 2. waveform data from the iPMTs

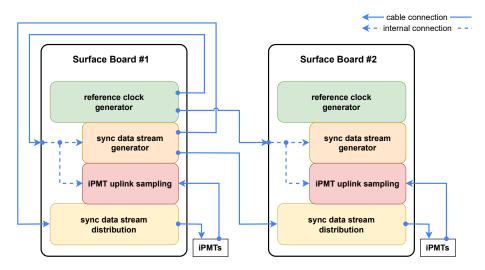

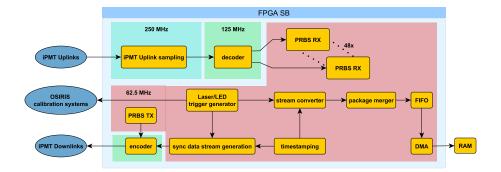

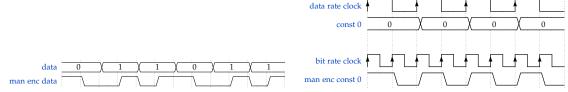

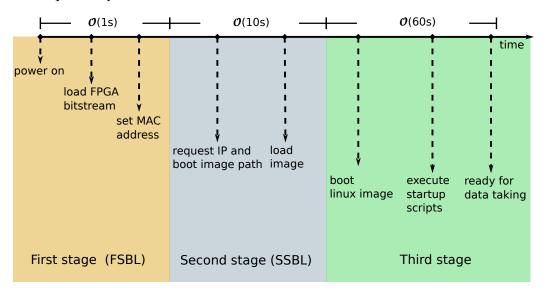

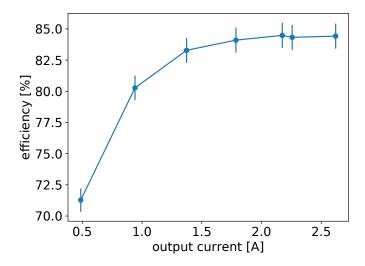

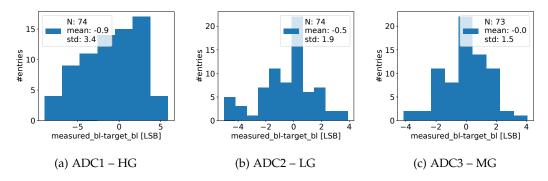

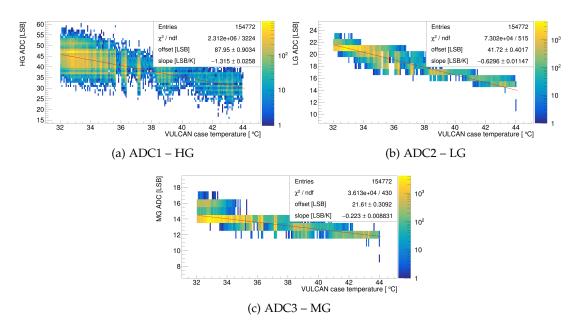

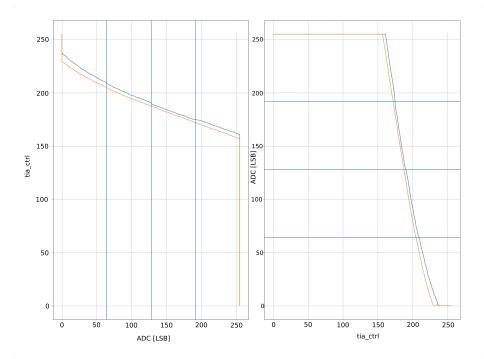

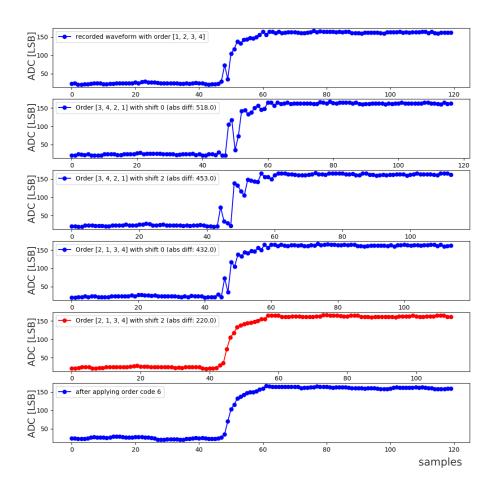

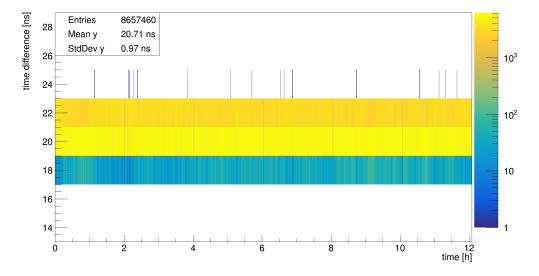

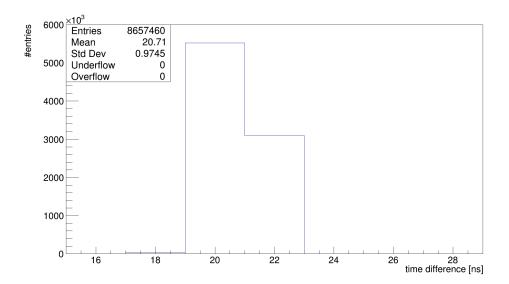

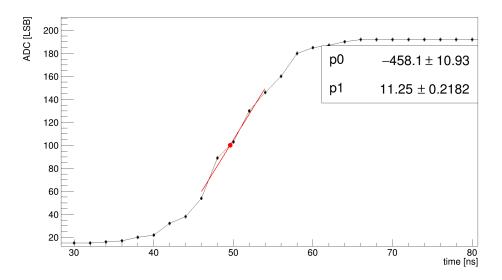

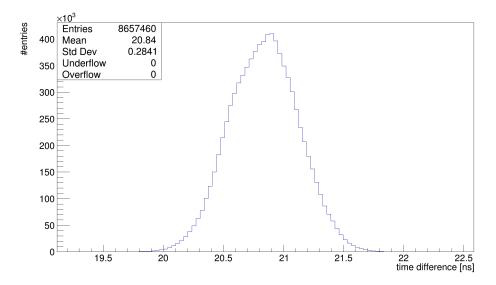

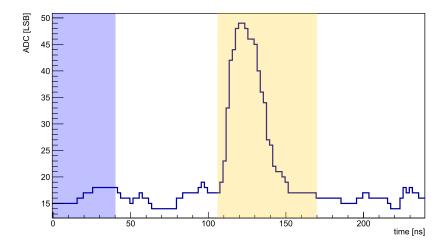

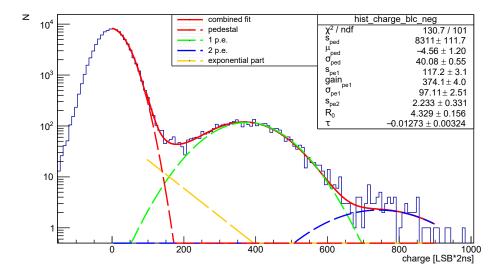

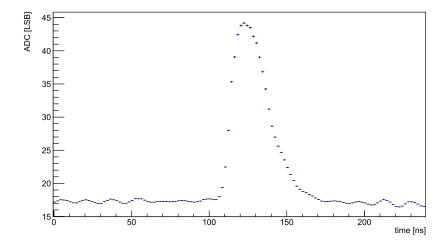

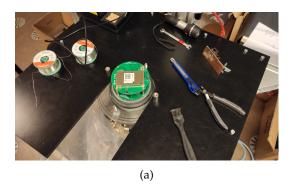

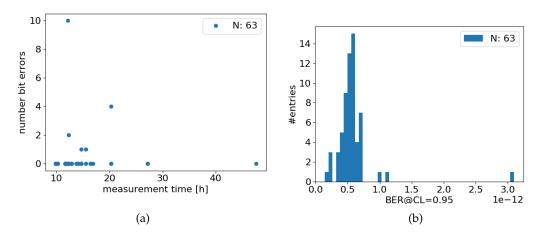

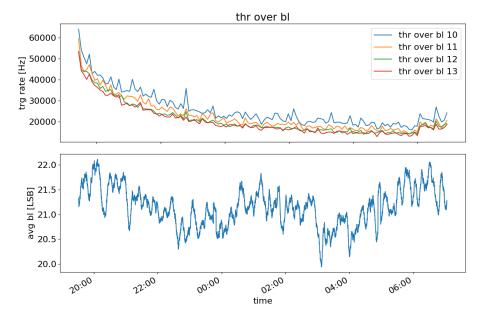

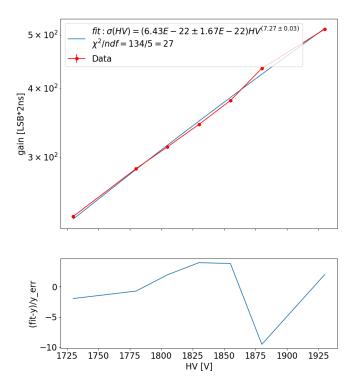

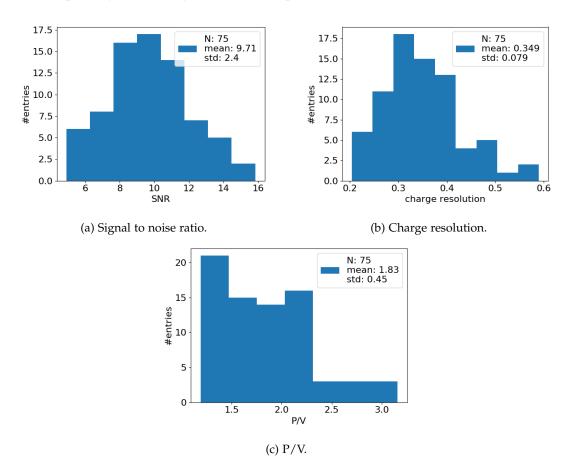

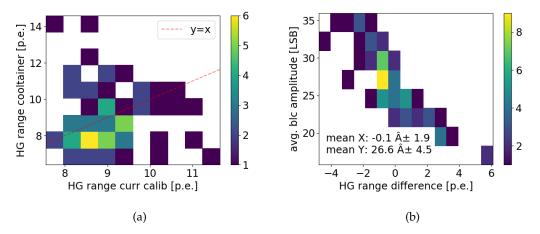

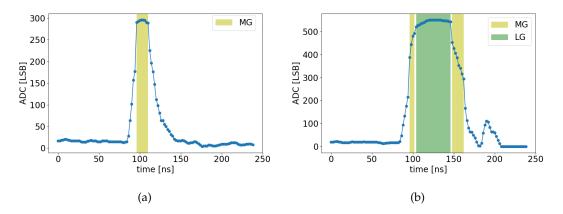

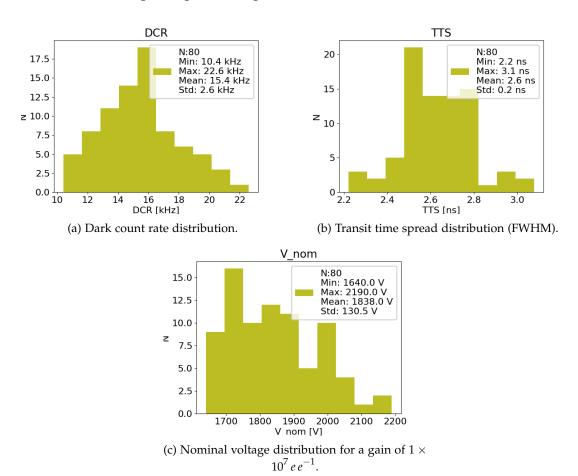

A major part of the timing system is implemented in the SB. Fig. 4.12 shows an overview of the system with the SBs as central component. The SB implements a master clock, which is based on a 125 MHz oscillator. The trigger signals for the calibration system are generated within the SB and directly tagged with a timestamp. This information is sent to the EB for further processing (event building).