Diese Arbeit wurde vorgelegt am Lehrstuhl für Hochleistungsrechnen (Informatik 12), IT Center.

# Entwurf eines statischen Leistungsmodells und Codegenerierung für Vektorbeschleuniger und Parallele Muster

# Designing a Static Performance Model and Code Generation for Vector Accelerators and Parallel Patterns

Bachelorarbeit

Tom Hilgers Matrikelnummer: 406581

Aachen, den 13. Januar 2023 Communicated by Prof. Matthias S. Müller

Erstgutachter: Prof. Dr. rer. nat. Matthias S. Müller (')

Zweitgutachter: Dr. rer. nat. Stefan Lankes (\*)

Betreuer: Semih Burak, M. Sc. (')

Adrian Schmitz, M. Sc. (')

(') Lehrstuhl für Hochleistungsrechnen, RWTH Aachen University IT Center, RWTH Aachen University

(\*) Institute for Automation of Complex Power Systems, E.ON Energy Research Center, RWTH Aachen University

| Ich versichere hiermit, dass ich die vorliegende Arbeit selbständig und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Alle Stellen, die wörtlich oder sinngemäß aus veröffentlichten und nicht veröffentlichten Schriften entnommen sind, sind als solche kenntlich gemacht. Die Arbeit ist in gleicher oder ähnlicher Form noch nicht als Prüfungsarbeit eingereicht worden. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                          |

| Aachen, den 13. Januar 2023                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                          |

# Kurzfassung

Moderne Supercomputersysteme haben eine verteilte und heterogene Struktur, die verschiedene Recheneinheiten wie CPUs, GPUs und andere Beschleuniger umfasst. Die Parallel Pattern Language (PPL) ermöglicht die hardwareunabhängige Programmierung solcher Systeme mit parallelen Mustern und generiert global optimierten Code unter Verwendung des Roofline Leistungsmodells. Diese Arbeit zielt darauf ab, die PPL zu erweitern, um Vektorbeschleuniger (VB) zu unterstützen, welche eine höhere Energieeffizienz als die gängigsten Recheneinheiten bieten. Das Roofline Modell wird erweitert, indem die besonderen architektonischen Merkmale von VBs berücksichtigt werden, wodurch eine Genauigkeit von ~80% bis 99% erreicht wird. Die PPL-Komponenten werden hinsichtlich der notwendigen Änderungen für die VB-Codegenerierung analysiert. Die Generierung von funktionalem Code erfordert nur begrenzte Anderungen an der Codegeneratorkomponente. Die Steigerung der Effizienz von Datentransfers in diesem Code erfordert Änderungen an der Frontendsprache und der Intermediate Representation. Diese Vorschläge werden zum Teil in einem Proof-of-Concept umgesetzt, das in der Lage ist, funktionalen und korrekten Code für VBs zu erzeugen. Dieser Code wird evaluiert, um mögliche Leistungsverbesserungen zu ermitteln.

**Stichwörter:** HPC, Vector Engine, Codegenerierung, Parallele Muster, Leistungsmodell

# **Abstract**

Modern supercomputer systems have a distributed and heterogeneous structure that incorporates various compute units such as CPUs, GPUs, and other accelerators. The Parallel Pattern Language (PPL) enables the hardware-independent programming of such systems with parallel patterns and generates globally optimized code using the Roofline performance model. This thesis aims to extend the PPL to support Vector Accelerators (VAs), which offer a higher energy efficiency than the most common compute units. The Roofline model is extended by considering the special architectural features of VAs, which achieves an accuracy of ~80% to 99%. The PPL components are analyzed regarding the necessary modifications for VA code generation. Generating functional code requires limited changes to the code generator component. Increasing the efficiency of data transfers in this code necessitates changes to the frontend language and intermediate representation. These proposals are partially implemented in a proof-of-concept that is capabable of generating functional and correct code for VAs. This code is evaluated to identify potential performance improvements.

**Keywords:** HPC, Vector Engine, Code Generation, Parallel Patterns, Performance Model

# **Contents**

| Lis | st of | Figures                           | хi   |

|-----|-------|-----------------------------------|------|

| Lis | st of | Tables                            | xiii |

| 1   | Intr  | oduction                          | 1    |

| 2   | Rela  | ated Work                         | 3    |

|     | 2.1   | Performance Models                | 3    |

|     |       | 2.1.1 Roofline Model              | 3    |

|     |       | 2.1.2 Other Models and Usage      | 4    |

|     | 2.2   | Code Generation                   | 5    |

| 3   | Bac   | kground                           | 7    |

|     | 3.1   | Roofline Model                    | 7    |

|     | 3.2   | Parallel Patterns                 | 9    |

|     | 3.3   | Parallel Pattern Language         | 9    |

|     |       | 3.3.1 Global Optimization         | 10   |

|     |       | 3.3.2 Toolchain Overview          | 11   |

|     | 3.4   | Vector Accelerators               | 12   |

|     |       | 3.4.1 Vector Processors           | 12   |

|     |       | 3.4.2 Comparison to CPUs and GPUs | 13   |

|     |       | 3.4.3 Practical Requirements      | 14   |

|     |       | 3.4.4 NEC SX-Aurora               | 15   |

|     | 3.5   | Benchmarks                        | 18   |

| 4   | Per   | formance Model                    | 21   |

|     | 4.1   | Proposed Model                    | 21   |

|     |       | 4.1.1 Concept                     | 21   |

|     |       | 4.1.2 Vector Length               | 22   |

|     |       | 4.1.3 Effective Memory Bandwidth  | 23   |

|     | 4.2   | Validation                        | 24   |

|     |       | 4.2.1 Setup and Methodology       | 25   |

|     |       | 4.2.2 Results                     | 25   |

|     | 4.3   | PPL Integration                   | 28   |

|     | 4.4   | Discussion                        | 30   |

| 5   | Cod   | le Generation                     | 33   |

|     | 5.1   | Coals                             | 33   |

### Contents

|     | 5.2   | Requi   | ${ m rements}$                      | 34 |

|-----|-------|---------|-------------------------------------|----|

|     |       | 5.2.1   | Frontend Language                   | 34 |

|     |       | 5.2.2   | Hardware Language and Cluster Model | 36 |

|     |       | 5.2.3   | Optimizer                           | 37 |

|     |       | 5.2.4   | Abstract Mapping Tree               | 38 |

|     | 5.3   | Code    | Generator Component                 | 39 |

|     |       | 5.3.1   | Programming and Execution Model     | 40 |

|     |       | 5.3.2   | Parallel Patterns                   | 41 |

|     |       | 5.3.3   | Visitor                             | 42 |

|     |       | 5.3.4   | Iterator Node                       | 42 |

|     | 5.4   | Imple   | mentation                           | 43 |

|     |       | 5.4.1   | Optimizer                           | 43 |

|     |       | 5.4.2   | AMT                                 | 43 |

|     |       | 5.4.3   | Code Generator                      | 44 |

|     | 5.5   | Evalua  | ation                               | 46 |

|     |       | 5.5.1   | Setup and Methodology               | 47 |

|     |       | 5.5.2   | Results                             | 47 |

|     | 5.6   | Discus  | ssion                               | 48 |

| 6   | Con   | clusion | and Future Work                     | 51 |

| Α   | Mea   | asurem  | ent Results                         | 53 |

| Bi  | bliog | raphy   |                                     | 55 |

| Lis | st of | Abbrev  | viations                            | 65 |

# **List of Figures**

| 3.1 | performance, main memory bandwidth, and L3 cache bandwidth are                                        |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | given as performance bounds. An algorithm with an operational                                         |    |

|     | intensity of 0.25 is fitted into these                                                                | 8  |

| 3.2 | The <i>Reduce</i> parallel pattern that combines partial results in the form of a tree. Based on [58] | ç  |

| 3.3 | The toolchain components and workflow of the PPL. Taken from [83].                                    | 11 |

| 3.4 | Vector Processors feature larger vector registers than CPUs with Single                               |    |

|     | Instruction Multiple Data (SIMD) capabilities                                                         | 13 |

| 3.5 | Overview of the SX-Aurora Type 10B Vector Processor                                                   | 15 |

| 3.6 | Sample cluster architecture with two nodes containing Vector Engines                                  |    |

|     | (VEs) that are connected by InfiniBand                                                                | 17 |

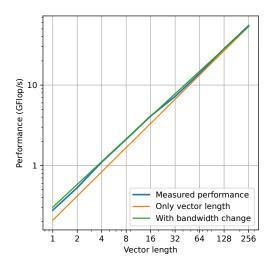

| 4.1 | Performance roofs for different vector lengths on the SX-Aurora                                       | 23 |

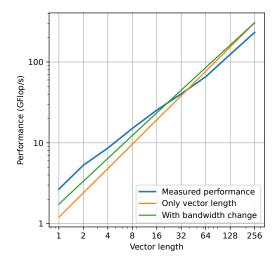

| 4.2 | The memory bandwidths of an SX-Aurora as a function of vector                                         |    |

|     | length as calculated by the developed performance model                                               | 24 |

| 4.3 | The model in relation to the performance of the memory bound                                          |    |

|     | benchmarks                                                                                            | 26 |

| 4.4 | The performance model predictions in relation to the observed per-                                    |    |

|     | formance of the cache bound benchmarks                                                                | 27 |

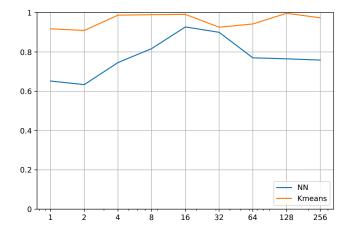

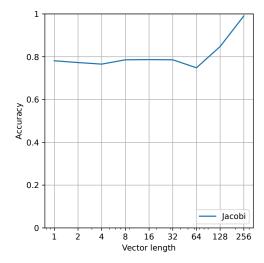

| 4.5 | Accuracy of the performance model for the compute bound benchmark                                     |    |

|     | over the vector lengths                                                                               | 28 |

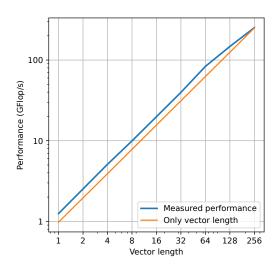

| 4.6 | The STREAM benchmark results in comparison to the bandwidth                                           |    |

|     | predicted by the performance model for different vector lengths on                                    |    |

|     | the SX-Aurora Type 10B                                                                                | 29 |

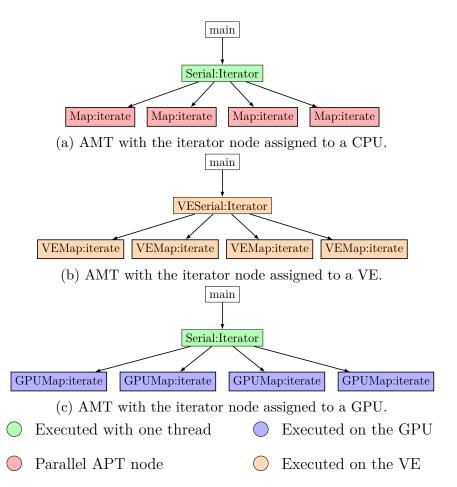

| 5.1 | Abstract Mapping Tree (AMT) definitions based on the code in List-                                    |    |

|     | ing 5.2 for CPUs, GPUs, and Vector Engines (VEs)                                                      | 39 |

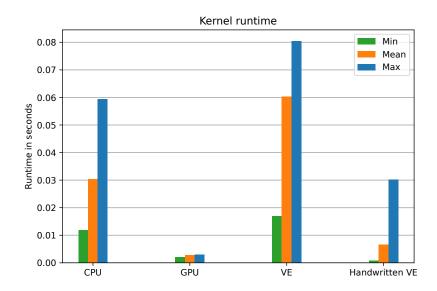

| 5.2 | Kernel runtime of the K-Nearest neighbors (NN) algorithm on different                                 |    |

|     | architectures                                                                                         | 48 |

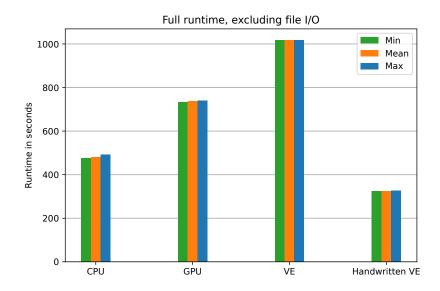

| 5.3 | Full runtime of the K-Nearest neighbors (NN) algorithm on different                                   |    |

|     | architectures                                                                                         | 49 |

# **List of Tables**

| 3.1 | A description of the key variables used in the Roofline model and     |    |

|-----|-----------------------------------------------------------------------|----|

|     | their units of measurement                                            | 8  |

| 3.2 | The relevant hardware properties of the Vector Engine (VE) used in    |    |

|     | this thesis                                                           | 16 |

| 3.3 | The machine balance of various processing units. Based on [65, 2, 91, |    |

|     | 73, 92, 44]                                                           | 17 |

| 3.4 | Operational details of the memory and cache bound benchmark algo-     |    |

|     | rithms                                                                | 19 |

| A.1 | Performance (GFlop/s) of the computing benchmarks on a VE for         |    |

|     | each vector length                                                    | 53 |

| A.2 | Performance (GByte/s) of the STREAM benchmarks on a VE for            |    |

|     | each vector length                                                    | 53 |

| A.3 | Measurement results of generated code on various architectures. The   |    |

|     | generated code is the K-Nearest neighbors algorithm                   | 54 |

# 1 Introduction

The performance of the most powerful supercomputer systems continues to increase despite the slowdown of Moore's Law [85]. The exascale era in HPC has arrived with supercomputers like Frontier [74], JUPITER [30], and Aurora [9]. Such supercomputer clusters are facing new challenges due to rising energy prices. The growing gap between compute and memory performance reduces the energy efficiency of memory bound codes on the most common hardware, i.e., CPUs und GPUs. A solution to this problem can be alternative architectures realized as specialized accelerators. Vector Accelerators (VAs), in the form of NEC Vector Engines (VEs) are such an alternative due to their higher energy efficiency [47].

Todays supercomputer clusters have a distributed and heterogeneous structure. A large number of individual nodes, that contain various compute units, are connected to form a single system. Optimizing applications on such systems requires a detailed understanding of the structure and used hardware. Such applications are often not fully optimized because application developers are experts in their own field of research and rarely in HPC. Even for HPC experts, learning the system structure and programming models is a complex and time consuming task. The unique structure of each cluster also limits the portability of applications. A solution to these problems can be the automatic generation of optimized code.

The Parallel Pattern Language (PPL) is being developed to offer such a solution. Currently in a prototype development stage, it is a component based source-to-source compiler, where applications are developed in a parallel pattern based Domain Specific Language (DSL). This enables a hardware-independent expression of parallelism. From this code, an intermediate representation [83] is generated in the form of an Abstract Pattern Tree (APT), on which a global optimization [96, 95, 61] is then applied. Several algorithmic efficiencies are used to account for a given system structure. The choice of the hardware on which an application is to be executed in whole or in part is based on a performance model. Based on this decision, optimized source code is then generated [82]. The performance model and code generator component support CPUs and NVIDA GPUs with their respective execution and programming models.

The general goal of this thesis is to lay the foundations for the generation of code for VEs by the PPL. A static performance model for VEs is developed as the first step. It has to consider the special architectural features of VEs. For example, the performance of an algorithm directly depends on its vectorizability. Another major characteristic is the memory hierarchy with a single cache level between registers and main memory. The validity of the model model is examined with several benchmarks that are partially based on real-world algorithms.

#### 1 Introduction

As the second step of the foundational work, code generation for VEs is investigated in the context of the PPL. General objectives are specified and requirements for the individual PPL components are defined. Suggestions for the implementation, which consider the distinct programming and execution model of VEs, are given in the context of this definition.

The code generation proposals are partially implemented in a proof-of-concept extension of the PPL that can serve as a foundation for subsequent work. The generated code for VEs is evaluated in terms of correctness and performance. It is compared with handwritten VE code, as well as generated code for CPUs and GPUs. Conclusions are drawn on optimization potential in the new implementation and the PPL in general.

The validation of the performance model is performed with several benchmarks. These are K-Means clustering (K-Means), K-Nearest neighbors (NN), a Jacobi solver, and a linear shifter. With the exception of the latter, all benchmarks are based on real-world algorithms and thus enable a realistic assessment of the performance model. The assumptions made in the model about the memory architecture of VEs are investigated with the STREAM benchmark [57]. The NN benchmark is further used to evaluate the proof-of-concept code generator.

The main contributions of this thesis are:

- The definition and validation of a static performance model for VEs.

- The design of code generation for VEs in the PPL by specifiying requirements and proposing implementation approaches.

- The partial implementation and subsequent evaluation of the specified code generator.

The thesis is structured as follows. Chapter 2 provides an overview of related work. Chapter 3 introduces the relevant concepts and foundations. These are the Roofline performance model, parallel patterns, the PPL project, Vector Processors (VPs), and the used benchmarks. Chapter 4 presents and validates the developed performance model. The chapter further describes how the model can be integrated into the PPL. The specifications and requirements for the PPL to generate code for VEs are described in Chapter 5. Additionally, a proof-of-concept implementation is presented and evaluated. Chapter 6 concludes this thesis by summarizing the results and giving an outlook on possible future work.

# 2 Related Work

There exists a wide range of literature on performance modeling. Not only are there many different performance models, but also extensions of these for new applications. Automated code analysis tools utilize these models for hardware-specific performance predictions. Automatic code generation is also a subject of research, for example in conjunction with code optimization techniques. All of this is discussed in this chapter and the main differences to this work are highlighted.

#### 2.1 Performance Models

Algorithm performance on specific hardware can be abstractly modeled. Such performance models are broadly divided into two categories: static and dynamic. Static models only consider information that is available before a program is executed. Dynamic models use information obtained through the execution of a program for more accurate performance predictions. Both are frequently extended to include new hardware architectures. This work extends the scope of hardware architectures covered by static models with a new extension of the Roofline model for Vector Processors (VPs) in general and the NEC SX-Aurora TSUBASA Vector Engine (VE) in particular.

#### 2.1.1 Roofline Model

The Roofline performance model [100] statically provides an upper bound on the floating-point performance of a computational kernel on a given architecture. The model is widely used, as can be seen by the plethora of published literature [104, 52, 20, 34], some of which is presented in this section.

Many extensions have been developed because the original model is designed for regular CPU architectures and does not consider special architectural features. Ilic et al. [42] extend the model by considering the entire memory hierarchy of modern CPUs because the original model only considers the main memory. Their model has an upper bound for each level of the memory hierarchy, which they term a cacheaware Roofline model. An extension used in various publications [53, 48, 103, 104] considers the different peak performance levels achievable on modern processors in a hierarchical model. They provide multiple upper bounds, e.g., for half, single, double precision, and more. The result of both cache-aware and hierarchical Roofline models is a comprehensive abstraction of the system architecture, which enables a detailed static analysis of computational kernels. With regard to the vector architecture

used in this thesis, the Roofline model represents a suitable option for performance modeling. This is because, like other architectures, they are primarily designed for floating-point performance and have a comparable memory structure. The cacheaware Roofline model is used as a starting point, as it incorporates the memory hierarchy consisting of main memory and cache. The concept of multiple compute roofs is also applied, using the vector length as the key factor for the achievable performance.

Both the original and some of the extended Roofline models have been adapted to other architectures. However, to the best of the author's knowledge, no extension specifically exists for vector architectures. Lopes et al. [52] explore the performance, power consumption, and energy efficiency limits of computational kernels on GPUs by adapting the cache-aware Roofline model. Another extension for GPUs replaces the floating-point operation-based approach with an instruction-based model to gain deeper insights into performance limits [23, 24]. To model Field Programmable Gate Array (FPGA) performance, Da Silva et al. [20] incorporate results from highlevel synthesis tools. Siracusa et al. [88] use a similar approach where the Roofline model guides an automatic design optimizer to improve the performance of HPC applications on FPGAs. Extensions also exist for other architectures, such as mobile Systems on a Chip (SoCs) [36] and compute nodes with heterogeneous memory [21]. Choi et al. [16] show that the Roofline model is also useful in modeling the energy consumption of algorithms. All these works consider the unique characteristics of the respective hardware in the Roofline analysis and equation. This work applies this approach to VEs with the vector length and effective memory bandwidth extensions.

Cabezas and Püschel [13] further develop the Roofline model by including an extended set of hardware-related bottlenecks. They also describe a tool that analyzes a given computational kernel using an execution model with directed acyclic graphs, which is similar to the Abstract Pattern Tree (APT) of the Parallel Pattern Language (PPL). The Roofline model and its extensions have also proven useful in dynamic performance analysis, providing an easy-to-understand visualization of the theoretically achievable and practically achieved performance. A well-known example of a dynamic analysis tool that utilizes the Roofline model is Intel Advisor [87]. Koskela et al. [48] describe it as an integrated approach that considers cache awareness, cache blocking, and different peak performance levels. Marques et al. [53] evaluate Intel Advisor and its use of the Roofline model. Since the PPL performs a fully automated static analysis, the previously mentioned approaches are not pursued in this work.

## 2.1.2 Other Models and Usage

The Execution-Cache-Memory (ECM) model, proposed by Treibig and Hager [94], is based on the same fundamental idea of Roofline that the runtime of computational kernels is either determined by the peak compute power or the data transfer time. It requires an analysis of the entire cache and memory hierarchy of modern microarchitectures. The model has been applied and evaluated on various architectures

and systems in a series of publications [33, 101, 89, 39, 38, 40] by authors from the University of Erlangen-Nuremberg and associated institutions. It is not used in this work based on an evaluation of the advantages and disadvantages in comparison to the Roofline model. This discussion can be found in Section 4.1.1.

The previously mentioned models are specialized for predicting the runtime time of algorithms on a single compute unit. Modern systems use a large number of different compute units in parallel, e.g., multiple CPU sockets and accelerators distributed among nodes in a cluster. Communication and network latency must be considered to model the execution of programs on multiple nodes. Culler et al. [19] introduced the LogP model in 1993, where they factor in communication latency, overhead, bandwidth, and the number of processing units. Similar to the Roofline model, several extensions and refinements have been proposed. LogGP [6] incorporates the impact of long messages into the model to better capture the benefits of large data transfers. LogCA [7] models the impact and speedup that accelerators can have on a system. An introduction of these models into the PPL for modeling network costs was already proposed and to some extent implemented in previous work [95]. As a result, a sufficient modeling is already achieved, making it unnecessary to extend it in this work.

Performance models have proven useful in automated static code analysis, where they can be used to improve performance predictions and find potential bottlenecks. A number of frameworks have been developed for this purpose. A recent example is Kerncraft, presented by Hammer et al. [34] in 2015. It focuses on the memory hierarchy and uses both the Roofline and ECM models in combination with a code analyzer. Another tool for static performance analysis and modeling is MIRA [59]. It has some internal similarities to Kerncraft, but focuses on compute, i.e. floating-point, performance and bottlenecks. The methods of these frameworks are not applied to the PPL code analysis in this work, since the performance modeling already achieves a satisfactory accuracy with the existing code analysis. Beyond Kerncraft and MIRA, there are more analysis frameworks, some of which also include dynamic or hybrid approaches. Examples include MAQAO [25], Empirical Roofline Toolkit [51], ExaSat [97], and PBound [63].

## 2.2 Code Generation

The current field of code generation for VPs and VEs encompasses only a limited amount of literature. The NEC compiler [69] supports C, C++ and Fortran compilation to machine code for VEs. The LLVM compiler also provides such functionality [49] and further supports OpenMP offloading to VEs [17, 18]. As in the PPL [83], both generate an intermediate representation from the source code. Unlike in the PPL, binary machine code is generated instead of new source code. In this work, an extension of the PPL to generate source code for VEs is designed and partially implemented. A comparable approach that generates VE source code is not known to the author. The code generator implementation of the PPL presented by

#### 2 Related Work

Schmitz [82] is extended in this work. The PPL utilizes a source-to-source approach, from a Domain Specific Language (DSL) based on parallel patterns to parallelized C++ code. A comparable pattern-based development tool is presented by Modak et al. [62]. Reiche et al. [79] present another approach that utilizes a DSL for hardware accelerator code generation. Only NVIDIA GPUs can be used as offload targets in the existing PPL implementation. This is achieved by generating parallel CUDA code. In this work, the existing code generator is extended for VEs by using VEDA [68] instead of the CUDA library. VEDA is only used in a limited number of works [11, 98].

# 3 Background

This chapter presents the relevant technical background to this thesis in five separate sections. Section 3.1 explains the Roofline model and its usage. Section 3.2 then introduces the concept of parallel patterns. Section 3.3 describes the Parallel Pattern Language (PPL), its concept and core components. Vector Accelerators (VAs) are described in Section 3.4 by introducing the general concept and special features of Vector Processors (VPs). The section further presents and describes the used hardware architecture and its most important features. An overview of the used benchmarks is given in Section 3.5. These are relevant for the model validation in Section 4.2 and performance evaluation of the proof-of-concept in Section 5.5

#### 3.1 Roofline Model

Static performance models are used to estimate the performance of an algorithm before it is executed. They have a simplified view of hardware and code properties, but capture the most important factors influencing performance. This performance is typically defined as the number of floating-point operations per second. The expected runtime can be calculated if it is known how many such operations an algorithm will perform.

The Roofline model [100] statically provides an upper performance bound for a computational kernel on a given hardware. It incorporates the main code and hardware characteristics in its calculation. In this work, the cache-aware Roofline model [42] is used as a starting point to consider the entire memory hierarchy of the modeled architecture. An important advantage of the Roofline model is the possibility of visualizing the achieved performance in relation to the performance bounds.

An architecture is characterized in the Roofline model by its peak performance Ppeak in floating-point operations per second (Flop/s) and the peak memory bandwidth  $\beta$  in bytes per second (Byte/s). The cache-aware Roofline model [42] makes a distinction between  $\beta_{mem}$ , for the main memory, and  $\beta_{cache}$ , for the cache. A computational kernel is represented by its operational intensity I, i.e., the number of bytes transferred per floating-point operation. These variables are listed in Table 3.1 for a better overview. The formula of the Roofline model to calculate the upper performance bound  $\pi$  is defined as

$$\pi = \min(Ppeak, I \cdot \beta). \tag{3.1}$$

| Variable | Description               | Unit      |

|----------|---------------------------|-----------|

| $\pi$    | Attainable performance    | GFlop/s   |

| Ppeak    | Peak hardware performance | GFlop/s   |

| I        | Operational intensity     | Flop/Byte |

| $\beta$  | Peak memory bandwidth     | GByte/s   |

Table 3.1: A description of the key variables used in the Roofline model and their units of measurement.

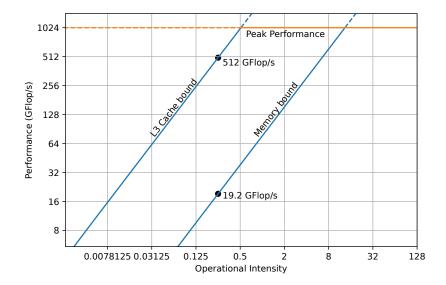

Figure 3.1: A sample visualization for the cache-aware Roofline model. Peak performance, main memory bandwidth, and L3 cache bandwidth are given as performance bounds. An algorithm with an operational intensity of 0.25 is fitted into these.

The cache-aware Roofline model is now explained in more detail with an example. Assume that a sample algorithm with an operational intensity of 0.25 is to be executed on an architecture with a peak performance of 1024 GFlop/s, 76.8 GByte/s main memory bandwidth, and 2 TByte/s L3 cache bandwidth. Other cache levels are omitted. This data is visualized in Figure 3.1 where the x-axis represents the operational intensity and the y-axis represents the achievable performance of the algorithm. It can be seen that the algorithm is memory or cache bound, therefore a distinction between the two must be made. The performance can reach 19.2 GFlop/s in case of memory boundness and 512 GFlop/s if it is cache bound. An implementation that does not achieve these values can be further optimized.

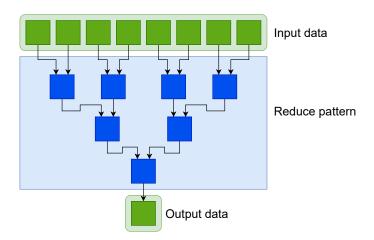

Figure 3.2: The *Reduce* parallel pattern that combines partial results in the form of a tree. Based on [58].

#### 3.2 Parallel Patterns

Software design patterns are generalized and reusable solutions for frequently occurring problems in software development. Parallel patterns [56, 58] describe such solutions for the concurrency domain of algorithms. Two parallel patterns are presented as an example in the following.

The *Map* pattern describes the independent application of a specific operation to the elements of a dataset. In practice, this means the implementation of a loop without dependencies between the iterations. The lack of dependencies allows an arbitrary level of parallelization to take place.

Another example is the *Reduce* pattern, which reduces a dataset into a single result by combining partial results. The pattern is often used to calculate the sum, minimum or maximum of the values of a dataset. Figure 3.2 provides a visualization of this pattern. It shows the input data which is combined step by step in the form of a tree to create a single output element. Parallelization can be achieved by assigning each combination of partial results to one thread. The degree of achievable parallelism is equal to the number of combinations per reduction step and decreases in each. The first step in the figure encompasses four combinations to reduce the eight input elements to four, which allows the use of four threads. This number is halved in the second step, where only two combinations take place. The final reduction to the single output element can then only be performed by a single thread.

## 3.3 Parallel Pattern Language

The PPL [61, 83, 96, 82] is a framework and toolchain for the efficient development of parallel programs for heterogeneous architectures. This section introduces the concept of global optimization and gives an overview over the toolchain components.

The descriptions are partially based on and inspired by previous work [12].

### 3.3.1 Global Optimization

The performance of an algorithm can be optimized on instruction, routine (local) and algorithm (global) levels. Both instruction and local level optimizations are already performed by hardware, compilers and with parallel programming models such as OpenMP [75]. The PPL builds on this and performs a global optimization in the context of execution on heterogeneous and distributed systems [95]. A global optimization considers the entire structure of an algorithm, to improve, for example, the overall parallelizability. For this purpose, larger structural elements, such as functions or parallel patterns, may be reordered, splitted or fused. This is accomplished in the PPL by representing the algorithmic structure in an Abstract Pattern Tree (APT) [61] where the nodes represent the parallel patterns and structures. The control and dataflow dependencies are represented by child nodes. Based on the APT, the global optimization is performed in three steps. Each step maximizes a well-defined algorithmic efficiency:

- Synchronization: Execute as many nodes, i.e. patterns, in parallel as possible.

- Inter-processor dataflow: Runtime minimal mapping of nodes to processors.

- Intra-processor dataflow: Runtime minimal mapping of tasks to the cores of a processor.

The global optimization is statically applied, which means that it relies entirely on the structural information obtained from the APT. No dynamic, i.e. runtime information about the actual computation is considered.

A set of global steps GSTEP can be obtained from the APT, where each represents a set of tasks, i.e. parallel patterns, that can be executed in parallel. The optimization based on the synchronization efficiency is hardware independent and seeks to minimize the total number of GSTEP while maximizing the number of tasks within each. This efficiency therefore represents the structural parallelism of the program.

For the inter-processor dataflow efficiency, the set of tasks within a *GSTEP* is mapped to the target architecture, described by a set of processors. The objective is a runtime-minimal mapping of tasks to processors. A processor is a homogeneous set of cores with a locally shared cache, such as a single CPU in a multiprocessor system or a streaming multiprocessor of a GPU. The optimization considers the execution cost of a task and the network cost of the necessary data transfers in order to statically model the runtime. The execution costs are based on the Roofline performance model [100], while the network costs are based on the LogP model [6].

Optimization on the basis of the intra-processor dataflow efficiency is performed by the code generator component. It optimizes the allocation of tasks to the individual cores of a processor by parallelizing with PThreads [71].

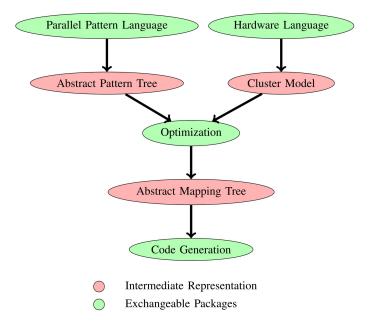

Figure 3.3: The toolchain components and workflow of the PPL. Taken from [83].

#### 3.3.2 Toolchain Overview

The PPL implementation [83] is a component-based toolchain in which some parts are interchangeable. It acts as a source-to-source compiler to increase application portability and let regular compilers perform additional, i.e. instruction and local, optimizations. An overview of the components and workflow can be found in Figure 3.3.

The central component is the optimizer, which performs the previously described global optimization. The optimization requires two input parameters, an APT and a hardware description. The APT is generated from source code in a Domain Specific Language (DSL). This simplifies the description of parallel patterns and thus also the generation of the APT. The description of the hardware on which a code is to be executed is given by a cluster model. It is generated from the JSON based Hardware Language (HL). The DSL and HL are the frontend to the developer. The result of the global optimization is a modified structure of the APT and a mapping to the given hardware. This information is stored in an Abstract Mapping Tree (AMT), in which the nodes now also model the execution on devices like GPUs and the necessary data transfers.

The information in the AMT is used by a code generator [82] that generates optimized and parallelized code for the respective target architectures. C++ code is generated to enable further optimization at instruction and local level by compilers. The generator also optimizes at the local level by parallelizing with PThreads for CPUs and CUDA for GPUs. The generated code uses MPI to address distributed memory in a heterogeneous system. A static Makefile is generated for the compilation on the target system.

Of these components, APT, cluster model, and AMT are part of the intermediate representation and are non-interchangeable. The frontend language, HL, optimizer, and code generator are freely interchangeable. For example, a new code generator supporting a different target architecture can be used instead of the current one by using the AMT as an interface.

### 3.4 Vector Accelerators

Flynn's taxonomy [26] distinguishes between several methods of executing instructions on data. Basic CPUs execute one instruction on one data element. This is referred to as Single Instruction Single Data (SISD). However, other methods can be used to improve performance. VPs use a technique called Single Instruction Multiple Data (SIMD). In this method, an instruction is executed on a group of data elements, called a vector. This, when supported by a memory system with sufficient bandwidth, can dramatically increase performance [31] while maintaining a similar power requirement [47, 1, 32]. SIMD is especially beneficial in multimedia [86, 5] and scientific applications [90, 35, 99] where only a few instructions are executed on a large amount of data. This section elaborates on the concept of VPs, their differences to CPUs and GPUs, and provides a description of the VP used in this thesis.

#### 3.4.1 Vector Processors

VPs have many distinctive features that separate them from other types of processors that might also implement SIMD. VPs usually utilize much longer vectors than regular CPUs with SIMD, thus processing more elements per instruction. Another difference is that VPs feature a fully variable vector length, meaning that a vector can take any length up to the architectural limit. Branching, i.e. conditional code, can slow down the pipelining of instructions, especially in the case of incorrect branch prediction. This is mitigated in VPs with predication [41, 78], where all possible branch paths are executed, but only on the vector elements for which the conditions are actually met. This is accomplished by using a mask vector register that contains the boolean values for each vector element and applying it to the conditional instruction. In Flynn's taxonomy, a CPU that implements predication is called associative [27]. To further improve performance, vector chaining [37, 93] is implemented. With this method, the results of one instruction are directly fed back into the execution units without additional memory references, which reduce performance.

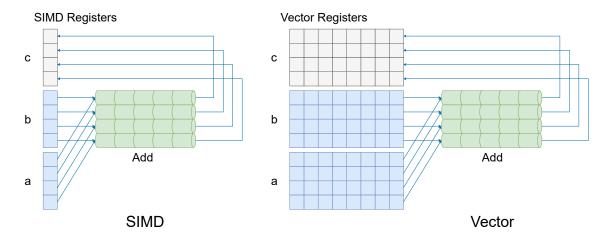

Modern CPUs use instruction pipelining, where instructions are executed in several substeps. VPs apply this concept to the data itself. Figure 3.4 illustrates this concept. The left side shows how CPUs with short vectors process data; in this case with a vector length of four. The right side shows how VPs process data. Their vectors are much longer, 32 elements in this example, and are only partially processed in each

Figure 3.4: Vector Processors feature larger vector registers than CPUs with SIMD capabilities.

cycle. Meaning that a single instruction is executed over multiple cycles, eight in this case. This reduces the load and latency of the instruction fetch and decode units. In addition, implicit loops can be formed, reducing the number of instructions and thus increasing memory efficiency. The (main) advantage of VPs over traditional CPUs and GPUs is a higher compute and energy efficiency, particularly for memory-bound codes [47].

Vector Accelerators are a special form of VPs. They are no longer the main execution unit of the system, but instead act as a co-processor. An x86 CPU acts as the main processor. VAs today take the form of a VP on a PCIe expansion card. Therefore, they experience the bottleneck of the PCIe bus to the host CPU and main memory, which can significantly slow down execution. For this reason VAs usually feature a dedicated high-speed memory subsystem.

## 3.4.2 Comparison to CPUs and GPUs

There are many differences between CPUs, GPUs and VPs, in particular in the way they implement SIMD. In the following, these differences are discussed with an emphasis on VPs.

#### **CPU SIMD**

Almost all modern CPUs support some form of SIMD. The most recent implementation in Intel and AMD x86 CPUs is called Advanced Vector Extensions (AVX) and can process up to 512 bits of data in a single Instruction [80]. This is not a long vector in comparison to VPs, where vector lengths have reached 16384 bits. While VPs feature a fully variable vector length, most SIMD implementations support only some fixed vector lengths, such as the powers of two between one and the maximum vector length. A difference between VPs and CPUs that is no longer present in

AVX-512 and ARM SVE2 [10] is predication, where masking vectors are applied to conditional instructions. Vector chaining, on the other hand, is missing in both AVX-512 and ARM SVE2. The results of an instruction are always written back to memory. In addition, widely used CPU architectures do not currently feature the form of data pipelining present in VPs. Which means that a new instruction is executed in each cycle, imposing a higher load and latency on the instruction fetch and decode units. CPU SIMD also consumes more power and thus generates more heat than normal instructions. As a result, Intel processors, for example, usually reduce their clock frequency when using all AVX units [84].

Because of the variety of available x86-extensions, programmers have to optimize their applications specifically for each target architecture and product generation. The use of architecture-specific intrinsics is one method of accomplishing this. This workload also increases over time, since many users are still operating processors with older extensions while new ones are frequently added.

#### **GPU SIMT**

GPUs implement a different form of SIMD, Single Instruction Multiple Threads (SIMT), by combining SIMD with multithreading [58]. A modern GPU has several thousand cores, each with its own Arithmetic Logic Units (ALUs), data caches, and register files. These cores execute instructions in groups called warps. The instruction is passed to a warp by a dedicated unit with a single instruction cache, instruction decoder, and program counter. Although all cores in a warp execute the same instruction, they do so on different data sets. The purpose of SIMT is to limit the overhead of fetching and decoding instructions [81]. To achieve non-scalar execution, VPs have large cores with many compute units. The GPU approach achieves this by synchronizing many small scalar cores. Similar to VPs, GPUs are specialized for high data throughput. One drawback of the SIMT approach is poor branching performance since all threads in a group must execute all branch paths, just masked for the various conditional instructions [77]. Afanasyev et al. [3] provide a more detailed comparison between the principles of vector processing and SIMT.

## 3.4.3 Practical Requirements

SIMD in general and VPs in particular place special demands on compute kernels in order to achieve high performance and to use the given resources efficiently. Such a kernel must not only be parallelizable, but also vectorizable. That is, several data elements must be processable with the same instruction. The code complexity must also be minimized, especially for branching, in order to guarantee efficient execution. However, a vectorizable kernel does not guarantee good vectorization, as is visible in the case of K-Means clustering: In the algorithm of Lloyd [50], the vector length is equal to the dimensionality of the data set. This makes vectorization inefficient for small dimensionality, i.e. short vectors. This is because the initialization time of the vector pipeline exceeds the time savings from vectorization. Accordingly, the

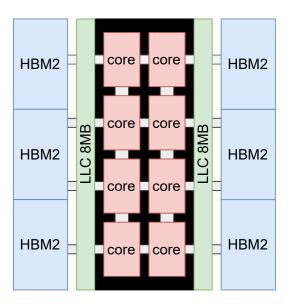

Figure 3.5: Overview of the SX-Aurora Type 10B Vector Processor.

input data must also be taken into account when evaluating the vectorizability of an algorithm.

#### 3.4.4 NEC SX-Aurora

The SX-Aurora TSUBASA is a Vector Accelerator (also called Vector Engine (VE)) manufactured by NEC and intended to be used as a PCIe co-processor [67]. It is the successor to the SX-ACE and was presented in 2018 [102]. The architecture has its roots in the early 1980s and has been continuously developed ever since [28]. The SX-Aurora is the first VP sold as a dedicated accelerator card rather than in a complete supercomputer system. Real world applications include weather forecasting [43], sea state prediction for militaries [76], page rank algorithms [4], and other memory-intensive applications. This section provides a detailed description of the architecture, performance, system integration and other features of the VE.

#### Architecture & Performance

The specific SX-Aurora model used in this work is the Type 10B [65] with 8 cores clocked at 1.4GHz. Figure 3.5 gives an overview of the architecture. All cores share 16 MB of Last Level Cache (LLC). The processor is connected to six High Bandwidth Memory (HBM) modules with a capacity of 48 GB and a total bandwidth of 1.229 TByte/s. Each core has a maximum bandwidth of 409.6 GByte/s to the main memory and 3 TByte/s to the LLC. Table 3.2 provides a summary of its most important hardware properties relevant for this thesis.

Each core consists of three main components, a Scalar Processing Unit (SPU), a Vector Processing Unit (VPU), and a memory subsystem. All relevant compute capability is provided by the VPU, while the SPU is designed to provide basic

| VE                    | Type 10B          |

|-----------------------|-------------------|

| Core Count            | 8                 |

| Clock Speed           | $1.4\mathrm{GHz}$ |

| Vector Length         | 256               |

| Peak DP Performance   | 2.15  TFlop/s     |

| Main Memory Size      | 48 GB             |

| Main Mamory Bandwidth | 1.229  TByte/s    |

| LLC Size              | 16 MB             |

| LLC Bandwidth         | 3  TByte/s        |

|                       |                   |

Table 3.2: The relevant hardware properties of the VE used in this thesis.

functionalities comparable to those of a CPU. A VPU hosts 64 vector registers, each with 256 entries and a width of 8 Byte, resulting in a vector length of 256 double elements. In comparison, the most recent SIMD implementations of Intel and AMD processors, e.g. AVX-512 [80], only have a vector length of 8 elements and are missing a deep pipeline. The compute capability of the VPU is provided by 32 parallel vector pipelines, each containing three Fused Multiply-Add (FMA) units, one Division/Square-Root (DIV/SQRT) unit and two ALUs. This results in a single VPU containing 96 FMA units, 32 DIV/SQRT units and 64 ALUs. All execution units are pipelined for higher efficiency. Meaning that, because there are 32 parallel vector pipelines per VPU, one vector instruction with a length of 256 is completed in 8 cycles.

The theoretical peak performance of the VE is determined by the number of cores and their number of execution units. Since each core features 96 FMA units, which achieve the highest performance compared to the other units, and each FMA unit executes two operation per cycle, the whole core can process 192 double elements per cycle. At the peak frequency of 1.4GHz, each core can achieve a peak double precision performance of 268.8 GFlop/s. The entire 8-core system can achieve 2.15 TFlop/s for double precision and 4.3 TFlop/s for single precision. In contrast, modern GPUs from NVIDIA, such as the V100 can achieve 7.066 TFlop/s for double precision and 14.13 TFlop/s for single precision [73, 92]. Besides the V100, which intended for data centers, consumer options can also outperform the VE in single precision performance. An example is the AMD Radeon RX6800 with 16.17 TFlop/s [2, 91].

An important metric for assessing the actual efficiency of hardware is machine balance. It is defined as the read and written bytes per (double precision) floating-point operation. This value has decreased in the the last decades [55], which means that fewer memory accesses are possible today than previously when reaching peak performance. Compute kernels that do not meet this requirement will therefore waste some of the potential peak performance and execute with lower efficiency. A higher machine balance means an increased efficiency. Table 3.3 lists the machine balance of various processing units, of which the SX-Aurora has the highest. This higher efficiency is also observed in practice [47].

| Device                      | Double Precision Performance (GFlop/s) | Memory<br>Bandwidth<br>(GByte/s) | Machine Balance<br>(Byte/Flop) |

|-----------------------------|----------------------------------------|----------------------------------|--------------------------------|

| NEC SX-Aurora<br>Type 10B   | 2150                                   | 1229                             | 0.572                          |

| AMD Radeon<br>RX6800        | 1010                                   | 512                              | 0.507                          |

| NVIDIA V100                 | 7066                                   | 900                              | 0.127                          |

| Intel Xeon<br>Platinum 8160 | 1612.8                                 | 128                              | 0.079                          |

Table 3.3: The machine balance of various processing units. Based on [65, 2, 91, 73, 92, 44].

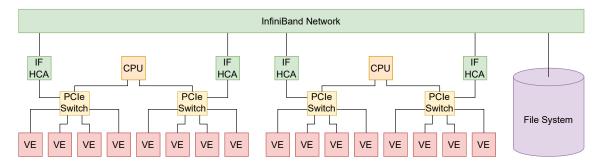

Figure 3.6: Sample cluster architecture with two nodes containing VEs that are connected by InfiniBand.

#### **System Integration**

The SX-Aurora Vector Engine is a PCIe add-in card and functions similarly to a GPU with some important differences. A VE combines vector processing with x86 architecture and programming paradigms. While a GPU has frequent data transfers between it and the host system, the VE typically only transfers data at the beginning and end of a program, or when using system calls [70]. This, along with the large main memory, avoids the PCIe bottleneck. Modern GPUs are programmed with specialized languages or APIs. Examples include CUDA [72], OpenGL [45], Vulkan [46] and DirectX [60]. In contrast, a VE executes standard C, C++ or Fortran code, which simplifies the development process. VE code is compiled by a proprietary compiler from NEC [64], which vectorizes and parallelizes the code automatically and further supports OpenMP and MPI. Due to these properties, VE programs behave similarly to any other Linux program and can use almost any Linux system call. These system calls are managed by the Vector Engine Operating System (VEOS) on the host CPU, called Vector Host (VH).

Since the SX-Aurora is designed to be used in supercomputer systems rather than personal computers or servers, it supports cross-card communication. In practice, this means that several VEs are connected via the PCIe Bus of a system. They are usually grouped together via a PCIe switch. An InfiniBand network can be used for additional connections to other nodes. Figure 3.6 shows an example of a cluster architecture. This sample architecture consists of a file system node and two identical compute nodes. These are connected by an InfiniBand network through a Host Channel Adapter (HCA). The compute nodes have eight VEs grouped using two PCIe switches connected to the CPU and the InfiniBand network.

#### **Execution Models**

VEs support several methods of executing programs [29, 66]. The first is native compilation and execution, which is done with the NEC compiler. Native execution offers the advantage of a coherent code and thus improved readability. Disadvantages are the possibly low performance of scalar code sections, I/O functions, and system calls. To address these disadvantages, other execution models are also supported.

An alternative to native code is offloading from the CPU to the accelerator. In this case, only the compute kernels that are specifically suited for VPs would be executed on the SX-Aurora. All other code remains on the main CPU of the system, which might result in runtime savings. Offloading code requires an interface to the VE in the form of either OpenMP offloading or VEDA (Vector Engine Driver API) [68]. OpenMP offloading is already implemented for GPUs [8, 22]. On the VE, it is currently only supported with an extension to LLVM, which is presented and evaluated by Cramer et al. [17, 18]. VEDA, on the other hand, is usable in common compilers as an includable library. It offers a variety of commands that provide greater control and flexibility than OpenMP offloading. It is also possible to offload parts of a program from the VE to the vector host. This is especially useful if host functions like system calls are rarely used.

This thesis uses both native compilation and VEDA to port validation benchmarks, while the presented code generation is entirely based on VEDA.

## 3.5 Benchmarks

In this thesis, several benchmarks are used, some of which are based on algorithms that are used in real-world applications. They possess different performance bounds, parallelizability, and vectorizability. The latter is particularly important with regard to the investigated vector architecture

The first algorithm is a K-Means clustering (K-Means) that is based on Lloyd's algorithm [50], and part of the Rodinia benchmark suite [14, 15]. It has a high degree of data parallelism, while still being memory bound. The algorithm partitions the data points on an n-dimensional grid such that each data point is assigned to the nearest of k clusters. These clusters are moved to the center of their partitioning.

This procedure is repeated in several iterations to find an optimal clustering. The vector length that can be achieved is equal to the dimensions of the grid and the data points.

The second used algorithm is K-Nearest neighbors (NN). Like K-Means, it can also be effectively parallelized and is memory bound. The used implementation is also part of the Rodinia benchmark suite. The algorithm finds the k nearest neighbors of an input point in a dataset. Unlike K-Means, this does not require multiple iterations but only needs to be performed once. Vectorizability in this algorithm does not depend on the dimensionality of the dataset, but only on the actual code design. In this implementation, a high degree of vectorization is possible.

A Jacobi solver is used, to cover cache bound algorithms. This algorithm changes array elements in a certain pattern, which is called a stencil. The exact pattern is based on the Jacobi method, which approximately solves a system of equations. Nested loops and branches permit only a partial vectorization, but that still results in significant performance improvements.

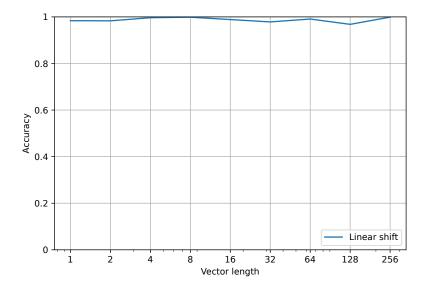

A new algorithm is implemented in order to investigate compute bound problems. It is a linear shift of a dataset by adding a fixed value to each data element. This shift can be performed in an arbitrary number of iterations to allow for a runtime that can be accurately examined. The algorithm is highly parallelizable over the iterations. A high degree of vectorization of the shift operations is possible.

The exact selection of these algorithms is based on various aspects. They have to cover the relevant cases in the Roofline and developed performance model. That is, compute, main memory, and cache boundedness. The code complexity also plays a role in the selection. It has to be relatively low in order to guarantee portability to VEs as well as ease of investigation within the time frame of this work. Table 3.4 gives an overview of the data used for the Roofline model.

| Algorithm                  | Boundness | Loads +<br>Stores | Flops | Operational Intensity $I$ |

|----------------------------|-----------|-------------------|-------|---------------------------|

| K-Means                    | Memory    | 23                | 8     | 0.0435                    |

| clustering<br>K-Nearest    | Memory    | 3                 | 6     | 0.25                      |

| neighbors<br>Jacobi solver | Cache     | 9                 | 6     | $0.083\overline{3}$       |

Table 3.4: Operational details of the memory and cache bound benchmark algorithms.

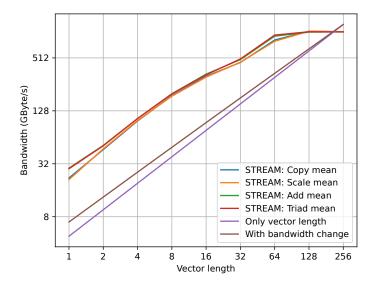

The STREAM benchmark [57] is used for additional validation. It measures the real achievable memory bandwidth of a hardware configuration with the help of four different kernels. By processing large arrays, these kernels minimize cache effects, which would distort the performance profile of the main memory. The original benchmark is modified to allow control of the vector length. This allows the relationship between vector length and memory bandwidth to be investigated. Thus, the assumptions made in the developed model can be analyzed.

# 4 Performance Model

Extending the Parallel Pattern Language (PPL) for Vector Engines (VEs) requires foundational work. The first step is the development of a performance model in order to predict the performance of an algorithm on VEs. The main constraint for this model in the context of the PPL is a static usability, based on hardware and code properties. A high accuracy for a wide range of algorithms must also be achieved. Section 4.1 presents a newly developed model that meets these requirements. Especially the accuracy is validated in Section 4.2 using the benchmarks introduced in Section 3.5. Section 4.3 then investigates how the model can be integrated into the PPL. A discussion on the results and proposals of this chapter follows in Section 4.4.

## 4.1 Proposed Model

This section introduces the developed performance model, which is composed of two newly developed extensions to the cache-aware Roofline model [100, 42]. Using it as the base model has a number of advantages that are outlined in Section 4.1.1. Section 4.1.2 and Section 4.1.3 then present the developed extensions.

## 4.1.1 Concept

Modeling the performance of algorithms on VEs does not require the development of a new model. Rather, existing models can be used and extended to cover the special characteristics and behaviors of VEs. There are two main requirements for such a model:

- 1. Static computability, based on code and hardware characteristics.

- 2. Accurate performance prediction for algorithms with different types of performance limitations.

Two models that meet these requirements are the Roofline [100] and ECM [94] models.

While both fulfill the aforementioned requirements, they achieve them with different methods. The cache-aware Roofline model [42] is chosen as the base model due to the following reasons: First, the performance modeling using both code and hardware properties only requires calculation with a single, simple formula (see Equation (3.1) and Table 3.1). Meanwhile, the ECM model requires the calculation of overlap and the use of more hardware properties, which might not be known for

a given architecture. For instance, the required cycles per data transfer, especially between the individual memory levels, are not entirely known for the proprietary SX-Aurora architecture. The second reason is that the Roofline formula can be quickly extended by adding new code or hardware factors. The relative complexity of the ECM model inhibits such extensibility. The third advantage of the Roofline model is its ease of visualization, which allows a programmer to quickly assess how much performance potential a code has. By using the cache-aware Roofline model, the entire architecture of the SX-Aurora is covered. Memory, cache and compute bound codes can be modeled.

### 4.1.2 Vector Length

The actual vector length in a computational kernel is crucial for the achievable performance on Vector Processors (VPs). For example, with a real vector length of 128 elements, only half of the available performance can be achieved on the SX-Aurora. The vector length should be integrated as a factor in the performance model to model this code characteristic. No version of the Roofline model published so far is specialized for VPs and considers the vector length as a key performance factor.

The vector length

$$V = \frac{v_{real}}{v_{max}} \tag{4.1}$$

is thus integrated into the Roofline Model as an additional factor, where  $0 < v_{real} < v_{max}$  holds. Here  $v_{real}$  is the real vector length within an algorithm and  $v_{max}$  is the maximum vector length supported by the architecture. On the SX-Aurora  $v_{max} := 256$  applies.

By adding the vectorization factor, the Roofline formula takes the form of

$$\pi = \min(Ppeak, I \cdot \beta) \cdot V. \tag{4.2}$$

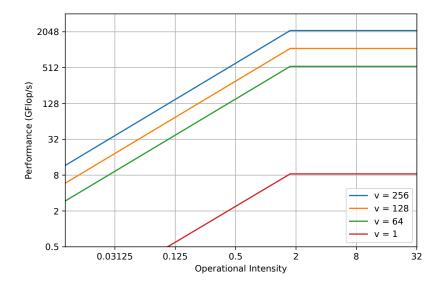

The original components of the formula (Ppeak, I, and  $\beta$ ) remain in their original form. The formula applies to both  $\beta_{HBM}$ , the main memory bandwidth, and  $\beta_{LLC}$ , the cache bandwidth. The multiplication with V ensures that the performance modeling for compute, memory, and cache bound codes depends on the vector length. The resulting performance scaling can be depicted within the established Roofline visualization, for which Section 3.1 provides an example. Figure 4.1 shows this exemplarily for the real vector lengths 256, 128, 64 and 1, where 256 is the upper and 1 the lower performance bound. However, any value between 1 and 256 can be used. The use of  $\beta_{LLC}$  is omitted for visual clarity. A new roof arises for each vector length.

The described extension maintains the Roofline model as a statically computable performance model. The information about the real vector length can be obtained with different (static) methods. For example, in K-Means clustering (K-Means), the vector length depends on the dimensionality of the dataset, while in other algorithms,

Figure 4.1: Performance roofs for different vector lengths on the SX-Aurora.

an analysis of the compute kernel is required. Consequently, static computation is possible in the context of the PPL toolchain.

## 4.1.3 Effective Memory Bandwidth

The initial validation of the newly added vectorization factor finds that it is not sufficiently accurate in modeling the behavior of the SX-Aurora in every case. In these measurements, some algorithms show higher performance than predicted by the model. This behavior is directly related to the vector length. For long vectors, the measured values are close to those predicted by the model. In contrast, for short vectors, the achieved performance is noticeably higher than predicted. To explain this discrepancy, the following hypothesis is put forward: The shorter the vector length, the higher the memory bandwidth achievable due to caching and prefetching effects. The validity of this hypothesis cannot be investigated further due to the proprietary nature of the SX architecture and the lack of response to contact attempts with NEC. However, a second extension based on the hypothesis is added to increase the accuracy of the vector length extended Roofline model on the SX-Aurora.

This is achieved by addressing the memory bandwidth.  $\beta_{HBM}$  is to be scaled non-linearly based on the vector length. The extension does not apply to  $\beta_{LLC}$ , since the mentioned discrepancies are not observed for cache-bound algorithms. This might be because cache effects are more pronounced when the main memory is used. The modified Roofline formula should still be easy to use, i.e. it should allow a straightforward performance calculation without requiring new variables. The exact formula is acquired by curve fitting to the benchmark performance. As a result, a

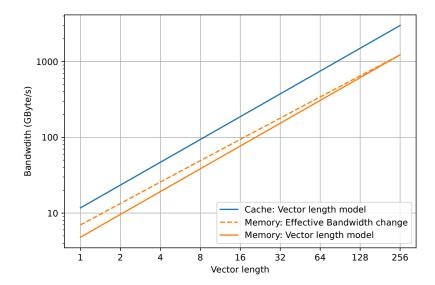

Figure 4.2: The memory bandwidths of an SX-Aurora as a function of vector length as calculated by the developed performance model.

new scaling factor

$$X = 100 \cdot \ln(\frac{1}{V}) \tag{4.3}$$

is introduced. This is added to the existing memory bandwidth. The Roofline formula for memory-bound algorithms thus takes the form of

$$\pi = \min(Ppeak, I \cdot (\beta_{HBM} + X)) \cdot V. \tag{4.4}$$

This achieves a non-linear scaling of the memory bandwidth. Figure 4.2 provides a visualization of the resulting differences in achievable bandwidth on an SX-Aurora as a function of the vector length. The cache bandwidth is represented by the blue line. The dotted orange line is the non-linearly scaled bandwidth, while the solid orange line is the originally assumed bandwidth. The distance between the two lines decreases as the vector length increases.

This second extension still allows a static performance prediction. In contrast to the first extension, no further analysis of the code is required. Only the distinction whether a code is bound by main memory or cache bandwidth becomes important. However, this is already necessary in the original cache-aware model.

## 4.2 Validation

An important requirement for any performance model is its accuracy when applied to real algorithms. Although such models have a simplified view of hardware and code properties, they capture the most important factors influencing performance.

The previously presented model is examined in this section in terms of its accuracy. For this purpose, the used setup and methodology are presented in Section 4.2.1. This is followed by the presentation and analysis of the results in Section 4.2.2.

## 4.2.1 Setup and Methodology

The extended model is validated using the benchmarks presented in Section 3.5. These cover all relevant cases, i.e. compute, memory, and cache boundness. The mean runtime of the compute kernels of the algorithms is measured over ten executions. It is converted into the performance in GFlop/s using the arithmetic and memory operation count from Table 3.4. An exception here is the STREAM benchmark, for which the memory bandwidth is calculated. Since the vector length is central to the extended model, the performance of each algorithm is examined for vector lengths between one and 256 elements. In order to reduce the time required for data collection while maintaining the same validity, the vector length only assumes powers of two in this range. The exact measurement results can be found in Tables A.1 and A.2.

In K-Means, the positions for five clusters are searched. In this algorithm, the vector length is equal to the dimensionality of the dataset. For this reason, a separate dataset is used for each vector length. To limit the runtime, the number of data points depends on the vector length. For a vector length of one or two, each dataset contains ten million elements. For all other lengths, it contains one million elements. In K-Nearest neighbors (NN), the k=50 nearest neighbors are searched in a data set containing 32768 points. Only the kernel calculating the distances is considered in the performance measurement. The Jacobi solver is executed on a 32768 by 32786 matrix in 50 iterations. In the compute bound linear shift kernel, the data set consists of six arrays, each with a length of 256, which are used in 50 billion iterations. The STREAM benchmark uses a data set with 100 million elements. Consequently, a single double array of this length consumes 800 MByte, which prevents cache effects.

All algorithms are executed on the nca01 node of the RWTH cluster. On this node, only the Type 10B Vector Engine is relevant for the measurements. Sections that are executed on the CPU, such as file I/O, do not affect the runtime measurements. The code is compiled with the NEC compiler [69] version 3.5.1. Correctness of the results is confirmed by a comparison with the results of the original code for CPUs.

#### 4.2.2 Results

The two investigated memory bound algorithms show distinct performance profiles. The average runtime standard deviation is 0.000015% for K-Means and 0.00347% for NN. The performance of K-Means is closer to the model than that of NN. As seen in Figure 4.3a, K-Means is very close to the scaled bandwidth model for all vector lengths. In contrast, the performance observed in NN (Figure 4.3b) is higher than predicted by the scaled model for short vectors, up to length 16. This might be

- lation to the performance predicted by the model extensions.

- (a) Measured performance of K-Means in re-(b) Measured performance of NN in relation to the performance predicted by the model extensions.

(c) Accuracy of the model for NN and K-Means over the vector lengths.

Figure 4.3: The model in relation to the performance of the memory bound benchmarks.

caused by unexpectedly strong cache effects. For all longer vectors, the performance is lower than predicted.

The accuracy of the model across all vector lengths and both algorithms is 86.7%. A breakdown across the individual vector lengths can be found in Figure 4.3c. It also shows that the performance of K-Means is closer to the predicted performance, with an average accuracy of 95.9%, than that of NN with 77.5%. Figure 4.3c also depicts how the measured and predicted performance of NN converge up to vector

(a) Measured performance of the Jacobi (b) Accuracy of the performance model for solver in relation to the predicted performance of the performance model extensions.

Figure 4.4: The performance model predictions in relation to the observed performance of the cache bound benchmarks.

length 16 and then diverge again beyond that. K-Means remains much closer to the model over all vector lengths. The performance measured by the Jacobi solver is higher than the performance predictions of the model, which results in an average accuracy of 77.3%. Figure 4.4a visualizes this fact. A more detailed overview on the accuracy is provided by Figure 4.4b. Both figures show that the predicted and observed performance almost match at the maximum vector length of 256. This behavior can be explained by register effects that might increase the performance for shorter vectors. The average standard deviation is 0.00135%. In the case of the compute bound algorithm, the model has an average accuracy of 98.7%. An overview of the accuracy across the different vector lengths is provided by Figure 4.5. The average standard deviation is 0.017%.

The STREAM benchmark is used to investigate the hypothesis of the non-linearly scaling memory bandwidth. Namely, whether it can actually be observed in practice. The measurement results are shown in Figure 4.6, where a large discrepancy between the measured and predicted values can be seen. For example, the Copy kernel at a vector length of 32 elements achieves a bandwidth of 498.58 GByte/s. The bandwidth-scaled model predicts 217.52 GByte/s, which is less than half of the observed value. A specific reason for these remarkable differences could not be identified. The benchmark is not cache bound, since all used arrays are too large to fit into the cache. This is proven by the profiling tools of the SX-Aurora which show a cache hit ratio of less than 0.1%.

Figure 4.5: Accuracy of the performance model for the compute bound benchmark over the vector lengths.

## 4.3 PPL Integration

The Roofline model, including its cache-aware form, is a static performance model. The addition of the vector length does not change this. It can, for example, be determined by the used data set, a factor which is statically known in the PPL, or with other code properties like statically defined loop ranges. Although it is possible to determine the actual vector length at runtime, this should be done by static code analysis in the context of PPL.

Statically finding the vector length in a given code section is a two-step process. The first step is to determine the loops that will be vectorized by the NEC compiler. However, not only individual loops but also nested loops can be vectorized. There are two cases of nested loops. The first are the tightly nested loops where multiple loops can be merged together to form a single vectorizable loop. Tightly nested loops only have instructions in the innermost loop. The other loops that are not tightly nested might not be vectorized together. Instead, only the innermost loop may be vectorizable. An exerpt from the kernel of an n-dimensional K-Means clustering in Listing 4.1 serves as an example. Here, the two loops are not tightly nested and only the innermost, that iterates over n-features, can be vectorized. Thus, in this case the actual vector length is equal to m-in (256, n-features). It should be noted that n-features is the dimensionality of the dataset and therefore statically available.

Other factors that can inhibit vectorization of any loop are **data dependencies**, **non-standard function calls**, **branches** (except in the case of min, max, compression, expansion, and search), **data transfers**, **I/O operations**, and **array initializations**. These general restrictions can be used to find the loop that will

Figure 4.6: The STREAM benchmark results in comparison to the bandwidth predicted by the performance model for different vector lengths on the SX-Aurora Type 10B.

Listing 4.1: An exerpt from K-Means clustering that assigns a datapoints to clusters.

```

for (int j = 0; j < nclusters; ++j) {</pre>

2

float dist = 0.0;

3

for (int k = 0; k < nfeatures; ++k){</pre>

4

dist += (feature[i][k]-clusters[j][k]) * (feature[i][k]-

clusters[j][k]);

5

}

6

(dist < min_dist) {

7

min_dist = dist;

8

index = j;

}

9

10

}

```

be vectorized. The second step of the analysis then finds the vector length inside this loop. After performing this analysis, the real vector length is determined and can be used in the model. This further means that integrating the model with this extension into the PPL is possible.

The second extension also preserves the performance model as a static analysis. The importance of the distinction between main memory and cache bound algorithms increases. This distinction must be made statically in the PPL and is based on the analysis of the variables used in an algorithm. If the memory requirements are smaller than the cache size, then the algorithm is cache bound. This condition can be used in the PPL, since both variable types and array sizes are defined statically, and thus the required memory space can be calculated. In the case of the SX-Aurora,

these variables must require less than 16 MB of memory in total. This limit can also be derived in the PPL from the cache size that is defined in the Hardware Language (HL). The model can therefore also be used with this extension in the PPL.