# Harnessing Stochasticity and Negative Differential Resistance for Unconventional Computation

Von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

Tyler Aaron Hennen

M.Sc.

aus Minnesota (USA)

Berichter: Univ.-Prof Dr.-Ing. Rainer Waser

Univ.-Prof Dr.-Ing. Tobias Gemmeke

Tag der mündlichen Prüfung: 11.07.2023

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

#### **Abstract**

Recently, there has been a resurgence of interest in materials with unusual electronic properties such as strong nonlinearity, hysteresis, and memory. This interest is due in part to the end of Moore scaling as well as the emergence of novel computing architectures. Currently, computational performance is limited by the memory bottleneck, as physical memory is not fast or large enough to feed the central processing unit (CPU) pipeline. One alternative is to introduce a new tier of memory that must be substantially faster and more scalable than existing Flash storage. Another approach is to develop schemes that take advantage of in-memory computation, as in the brain-inspired concepts of neuromorphic computing (NC). To reach their full potential, each of these strategies rely on the ability of new classes of memory technologies to exploit physical mechanisms yet to be fully harnessed on an industrial level.

This dissertation contains an investigation of two such nascent nanotechnologies in the category of resistive switching (RS). The first, redox-based resistive random access memory (ReRAM), is capable of mimicking biological synapses by allowing storage of large numbers of interconnected and continuously adaptable resistance values. The second technology is based on Cr-doped V<sub>2</sub>O<sub>3</sub>, a correlated-electron material for which electronic control of Mott insulator-to-metal transitions potentially offers a fast and durable way to emulate certain dynamical behaviors of neurons. Here, we apply reimagined methods and analysis of electrical measurement to these synaptic and neuronal devices. The newly acquired data sheds further light on the nature of the resistance transitions and is used to design physically validated device models for embedding in large-scale neuromorphic simulations.

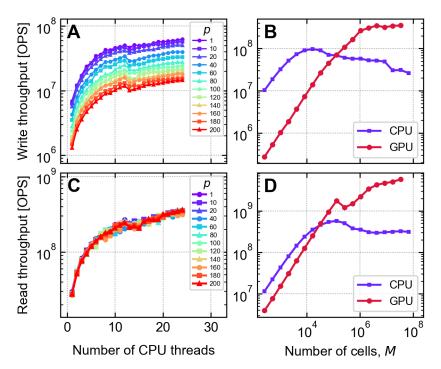

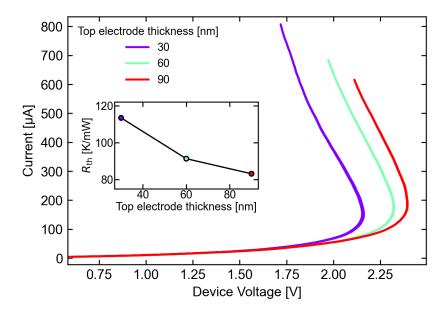

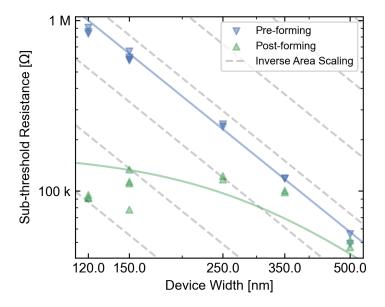

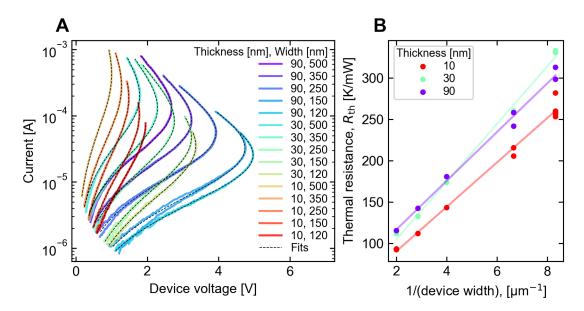

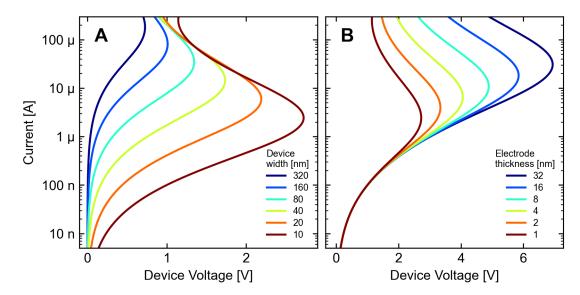

The measurement circuitry developed here addresses long-standing challenges in the external stabilization of device test structures, and allows (I, V) switching curves to be captured eight orders of magnitude faster than with commercially available equipment while causing significantly less electrical stress to the measured devices. Applying the measurement system, we introduce a new stochastic device model for solid-state synapses that is trained on a mass quantity of statistical measurement data of ReRAM. This model enables extremely fast (>  $10^8$  OPS) and accurate simulations of large synaptic arrays (>  $10^9$  cells) and provides a powerful new tool for statistical analysis of resistive switching data. Next, we identify an electro-thermal mechanism behind the negative differential resistance (NDR) and excitable dynamics observed in  $(V_{1-x}Cr_x)_2O_3$  nanodevices. We show fast volatile switching (< 10 ns), high switching endurance (>  $10^{12}$  cycles), and favorable scaling characteristics in

this promising Mott insulating material. A coexisting non-volatile (NV) mechanism is investigated and the conditional occurrence of filamentation in the devices is linked to circuit instabilities, with wider implications for NV switching in other RS materials. The  $(V_{1-x}Cr_x)_2O_3$  study culminates in a physical model that covers the scaling behavior and threshold adaptability, and is closely fit to observed oscillatory data.

#### Kurzfassung

In jüngster Zeit hat das Interesse an Materialien mit ungewöhnlichen elektronischen Eigenschaften wie starker Nichtlinearität, Hysterese und Speicherfähigkeit wieder zugenommen. Dieses Interesse ist zum Teil auf das Ende der Moore'schen Skalierung sowie auf die Entwicklung neuartiger Computerarchitekturen zurückzuführen. Derzeit wird die Rechenleistung durch den Speicherengpass begrenzt, da der physische Speicher nicht schnell oder groß genug ist, um die Pipeline der Zentraleinheit (CPU) zu speisen. Eine Alternative ist die Einführung einer neuen Speicherebene, die wesentlich schneller und skalierbarer sein muss als der vorhandene Flash-Speicher. Ein anderer Ansatz besteht darin, Systeme zu entwickeln, die die Vorteile des In-Memory-Computings nutzen, wie bei den vom Gehirn inspirierten Konzepten des neuromorphen Computings (NC). Um ihr volles Potenzial auszuschöpfen, ist jede dieser Strategien auf die Fähigkeit neuer Klassen von Speichertechnologien angewiesen, physikalische Mechanismen auszunutzen, die auf industrieller Ebene noch nicht vollständig genutzt werden.

In dieser Dissertation werden zwei solcher aufstrebenden Nanotechnologien in der Kategorie des resistiven Schaltens (RS) untersucht. Die erste Technologie, der redoxbasierte resistive Direktzugriffsspeicher (ReRAM), ist in der Lage, biologische Synapsen zu imitieren, indem er die Speicherung einer großen Anzahl vernetzter und kontinuierlich anpassbarer Widerstandswerte ermöglicht. Die zweite Technologie basiert auf Cr-dotiertem V<sub>2</sub>O<sub>3</sub>, einem Material mit korrelierten Elektronen, bei dem die elektronische Kontrolle von Mott-Isolator-zu-Metall-Übergängen eine schnelle und dauerhafte Möglichkeit zur Nachahmung des dynamischen Verhaltens von Neuronen bieten könnte. Hier wenden wir neuartige Methoden und Analysen elektrischer Messungen auf diese synaptischen und neuronalen Bauteile an. Die neu gewonnenen Daten werfen ein weiteres Licht auf die Natur der Widerstandsübergänge und werden verwendet, um physikalisch validierte Bauteilmodelle für die Einbettung in groß angelegte neuromorphe Simulationen zu entwerfen.

Die hier entwickelte Messschaltung löst die seit langem bestehenden Probleme bei der externen Stabilisierung von Teststrukturen und ermöglicht die Erfassung von (I,V)-Schaltkurven um acht Größenordnungen schneller als mit handelsüblichen Geräten, wobei die gemessenen Bauteile deutlich weniger elektrisch beansprucht werden. Mittels Anwendung des Messsystems stellen wir ein neues stochastisches Modell für Festkörpersynapsen vor, das auf einer großen Menge statistischer Messdaten von ReRAM trainiert wurde. Dieses Modell ermöglicht extrem schnelle (>  $10^8$  OPS) und genaue Simulationen von großen synaptischen Arrays (>  $10^9$  Zellen) und bietet ein leistungsfähiges neues Werkzeug für die statistische Analyse von resistiven Schaltdaten. Danach identifizieren wir einen elektrothermischen Mechanismus hinter dem negativen differentiellen Widerstand und der

neuronalen Dynamik, die in  $(V_{1-x}Cr_x)_2O_3$ -Nanobauteilen beobachtet werden. Wir zeigen schnelle flüchtige Schaltvorgänge (< 10 ns), hohe Schaltausdauer (>  $10^{12}$  Zyklen) und günstige Skalierungseigenschaften in diesem vielversprechenden Mott-Isolatormaterial. Ein koexistierender nicht-flüchtiger Mechanismus wird untersucht und das bedingte Auftreten von Filamentierung in den Bauelementen wird mit Schaltungsinstabilitäten in Verbindung gebracht, was weitreichende Auswirkungen auf nicht-flüchtiges Schalten in anderen RS-Materialien hat. Aus der  $(V_{1-x}Cr_x)_2O_3$ -Studie resultiert ein physikalisches Modell, welches das Skalierungsverhalten und die Anpassungsfähigkeit des Schwellenwerts abdeckt und eng mit den beobachteten oszillierenden Daten übereinstimmt.

#### Acknowledgements

This dissertation was written during my doctoral research at the Institut für Werkstoffe der Elektrotechnik 2 (IWE2) at RWTH Aachen University, in collaboration with Western Digital Corporation (WDC). This involved relocating across the planet, an experience that expanded my mind in ways I never could have predicted. At this point, I would like to acknowledge the contributions of many people who helped make this work possible.

I am grateful to Prof. Rainer Waser for his persistence in recruiting me, for the opportunity to work in the IWE2, and for the support in the meantime. Also, thanks to Prof. Tobias Gemmeke for agreeing to co-examine the thesis. I thank Dirk J. Wouters for advising from IWE2, for reviewing the thesis, and for many helpful discussions over the years.

I am immeasurably thankful to Daniel Bedau, advisor of the projects from the WDC side. Ten years ago, Daniel planted the seed of my interest in doing a PhD in a foreign country, and later made me aware of IWE2. During my time here he maintained the collaboration, however painstakingly, and continued to support and discuss the work in detail on a weekly basis. The industrial resources he contributed really elevated what was possible to do here.

Thanks Martina Heins for always being pleasantly willing to help and for being dynamic in unusual circumstances, and thanks Ulrich Böttger for extending my contract an absurd number of times.

I thank Jonathan A. J. Rupp and Johannes Mohr, colleagues who grew and optimized the VCrOx thin films and participated in the investigations.

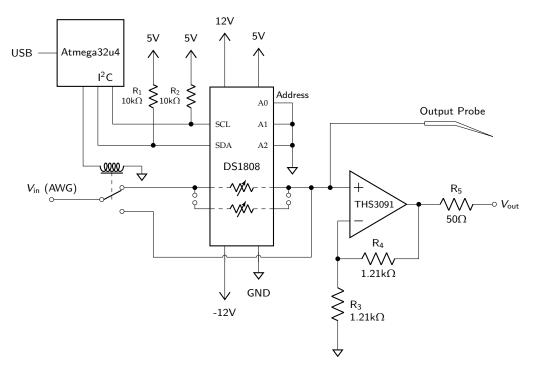

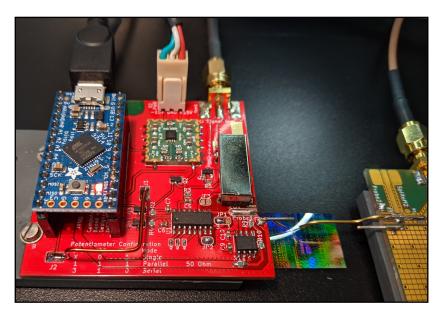

Thanks to Erik Wichmann, professional Hiwi and the only one within 30 km<sup>2</sup> who can operate a soldering iron, for working on the electronics, the PCB designs, and diagrams in the unholy TikZ language. Thanks to Eugen Gebert for helping build the temperature stage. Thanks to Alejandro García for helpful contributions to our bespoke instrumentation library. Thanks to Markus Beschow for adapting the COMSOL model.

I am ridiculously grateful to Anne Siemon, Marcel Schie, Camilla La Torre, Moritz von Witzleben, and Carsten Funck, without whom I never would have survived the logistics of living in Germany.

Thanks, Carlos Rosário, for being the only one who ever read any of my papers.

Thanks to our external collaborators, Peter Warnicke, Etienne Janod, Danylo Babich, Julien Tranchant, and Hongchu Du, for discussions and characterizations of the VCrOx films. Thank you Jeffrey Lille, Oleksandr Mosendz, Jean-François Nodin, and Gabriel Molas for fabrication of the ReRAM devices. Also thank you to the rest of our collaborators at WDC, Alexander Elias, Jim Rainer, Hans Richter, Derek Stewart, Joyeeta Nag, Wen Ma, and Michael Grobis.

Thanks to my very important teachers and mentors, Louis Cliff Grosberg and Prof. E. Dan Dahlberg, and thanks Prof. Eric Fullerton for investing in my early PhD career.

Thanks to Thomas Pössinger for the great illustrations. Thanks Udo Evertz for keeping the network up and giving me admin rights. Thanks Erhard Halfmann for roasting the coffee that fueled my writing.

Finally, a big thank you to my mom and dad, who I hold fully responsible for my existence. I hope this giant unintelligible book makes you proud.

#### **Contents**

| Al | ostrac | t                                                  | iii |

|----|--------|----------------------------------------------------|-----|

| A  | knov   | vledgements                                        | vii |

| In | trodu  | ction                                              | 1   |

| 1  | Fun    | damentals                                          | 5   |

|    | 1.1    | Redox-based resistive switching mechanisms         | 5   |

|    | 1.2    | Correlated electrons and the vanadium oxide system | 8   |

|    | 1.3    | Electrical measurements of resistive switching     | 10  |

|    | 1.4    | The electro-thermal switching mechanism            | 16  |

|    |        | 1.4.1 Thermistor dynamics                          | 16  |

|    |        | 1.4.2 The geometry of volatile switching           | 19  |

|    |        | 1.4.3 Oscillations and excitability                | 25  |

|    |        | 1.4.4 Field effects                                | 29  |

| 2  | Elec   | trical measurement setup                           | 31  |

|    | 2.1    | Digital potentiometer stabilization circuit        | 31  |

|    |        | 2.1.1 Design principles                            | 32  |

|    |        | 2.1.2 Implementation                               | 34  |

|    |        | 2.1.3 Measurement demonstrations                   | 38  |

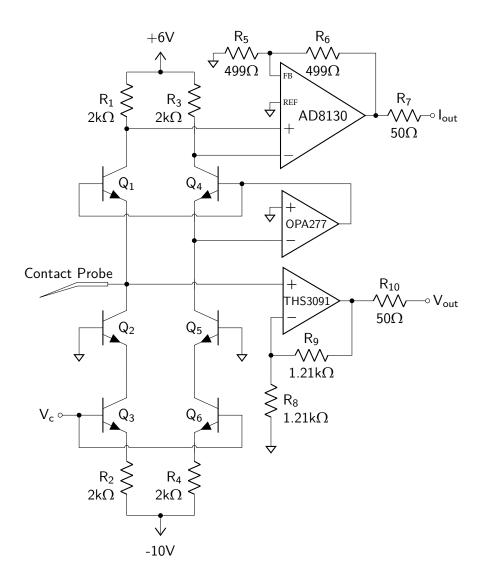

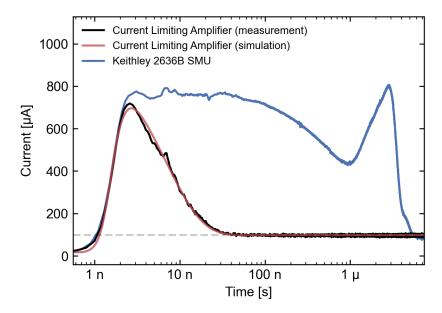

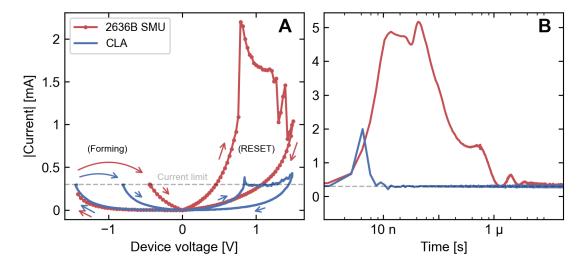

|    | 2.2    | Current limiting amplifier                         | 40  |

|    |        | 2.2.1 Design principles                            | 40  |

|    |        | 2.2.2 Implementation                               | 42  |

|    |        | 2.2.3 Measurement demonstrations                   | 46  |

|    | 2.3    | Discussion                                         | 58  |

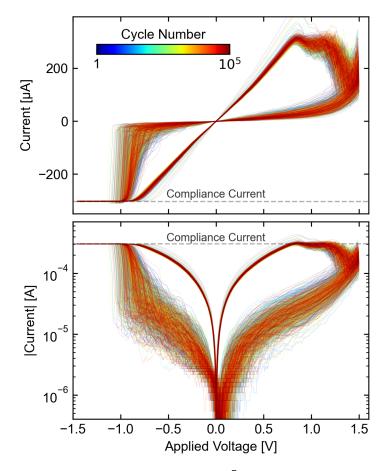

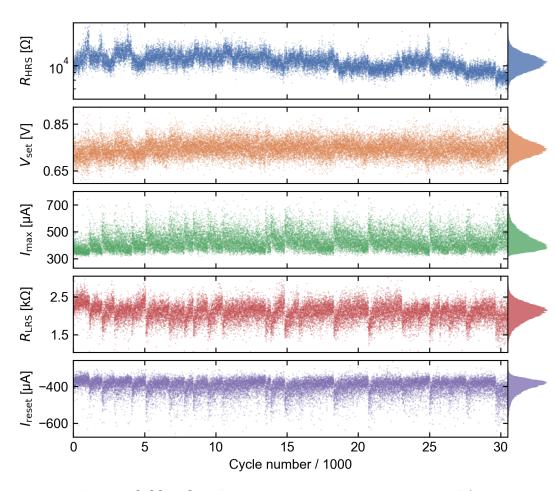

| 3  | Fast   | stochastic modeling of synaptic arrays             | 61  |

|    | 3.1    | Methods                                            | 62  |

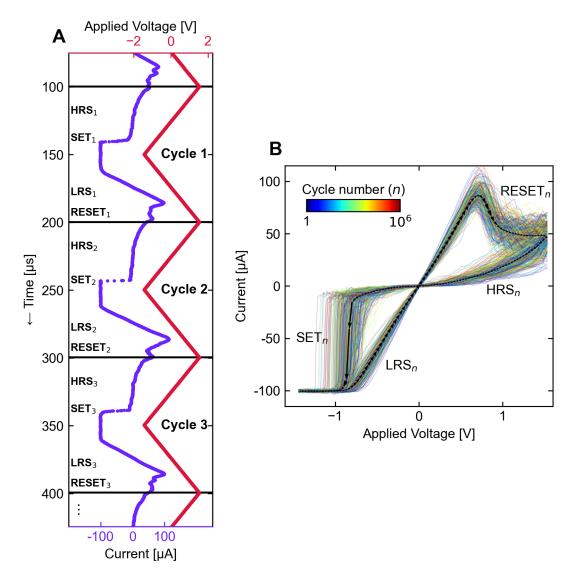

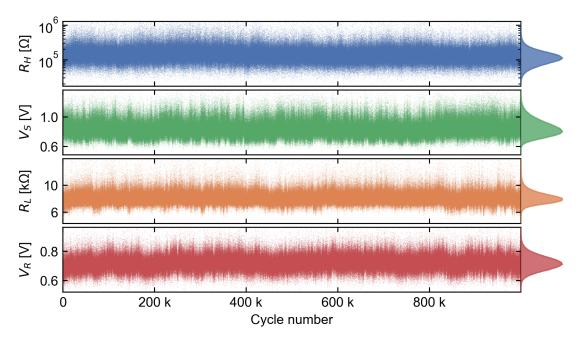

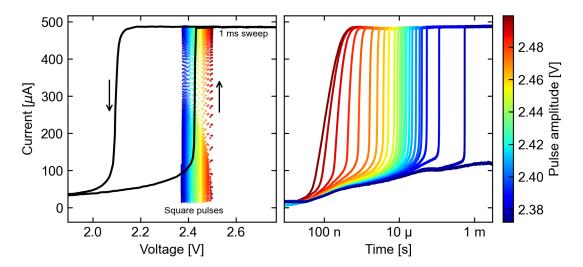

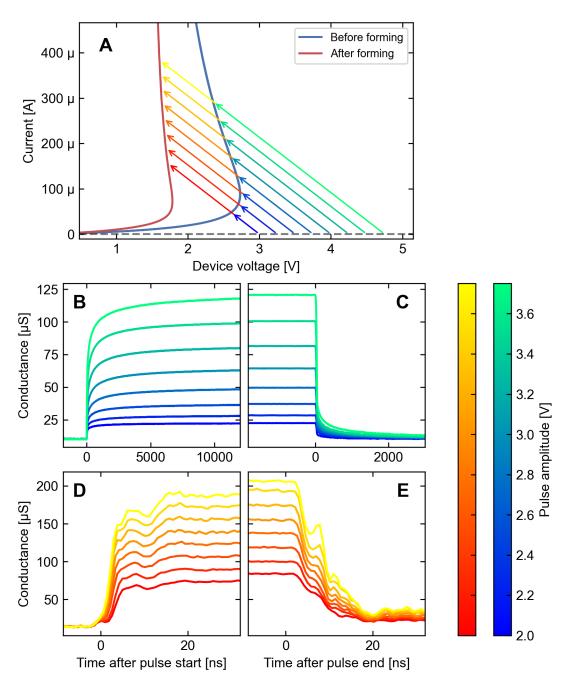

|    |        | 3.1.1 Data collection                              | 64  |

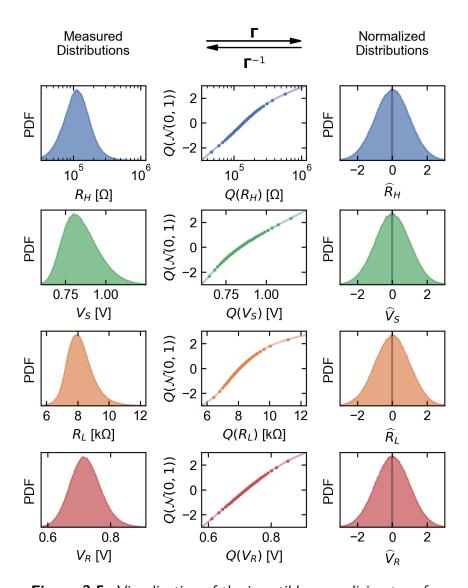

|    |        | 3.1.2 Feature extraction                           | 67  |

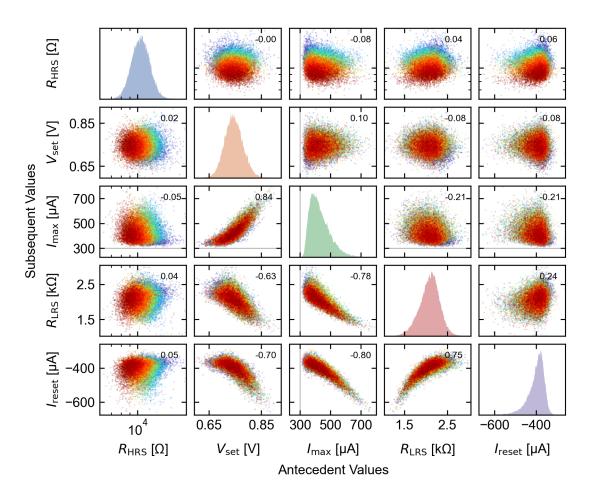

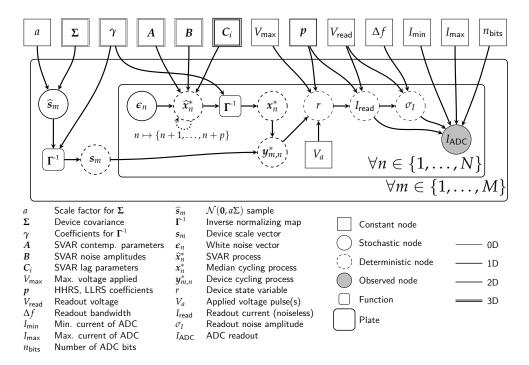

|    |        | 3.1.3 Stochastic modeling                          | 68  |

|    |        | 3.1.4 Program implementation                       | 79  |

|    | 3.2    | Simulation results                                 | 80  |

|    | 3.3    | Benchmarks                                         | 83  |

|    | 3.4    | Discussion                                         | 84  |

| 4  | Mot    | t-oxide neuronal nano-devices                      | 87  |

|    | 11     | Thin film deposition                               | 87  |

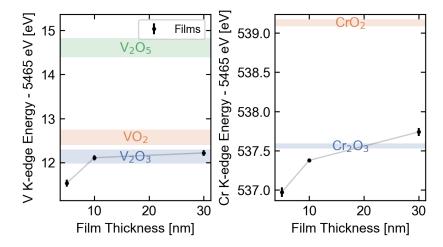

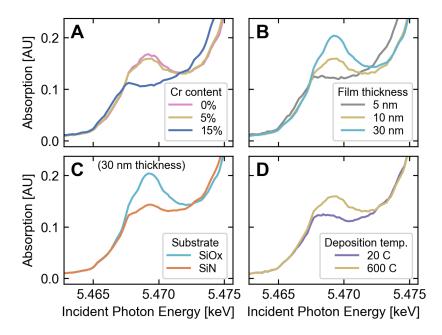

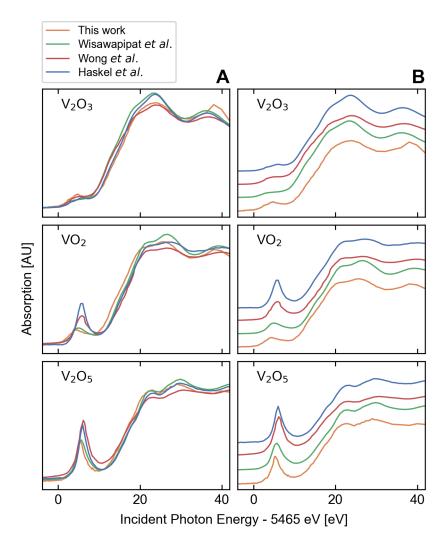

|    | 4.2   | Film characterization with X-ray absorption |                                     |     |  |

|----|-------|---------------------------------------------|-------------------------------------|-----|--|

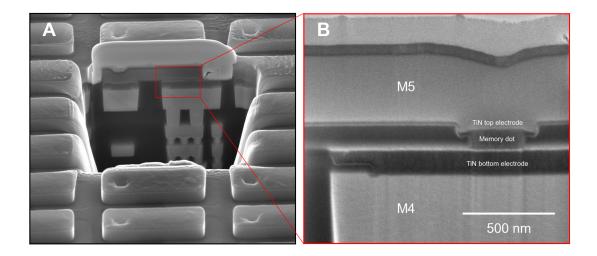

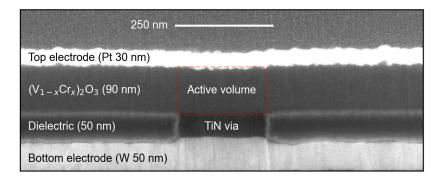

|    | 4.3   |                                             | device fabrication                  | 94  |  |

|    | 4.4   | Electri                                     | ical characterization               | 95  |  |

|    |       | 4.4.1                                       | The pristine state                  | 95  |  |

|    |       | 4.4.2                                       | Non-volatile effects                | 105 |  |

|    |       | 4.4.3                                       | Switching dynamics                  | 111 |  |

|    |       | 4.4.4                                       | Oscillatory/spiking behavior        | 116 |  |

|    | 4.5   | Electro                                     | o-thermal modeling                  | 119 |  |

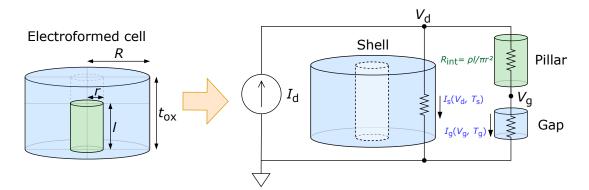

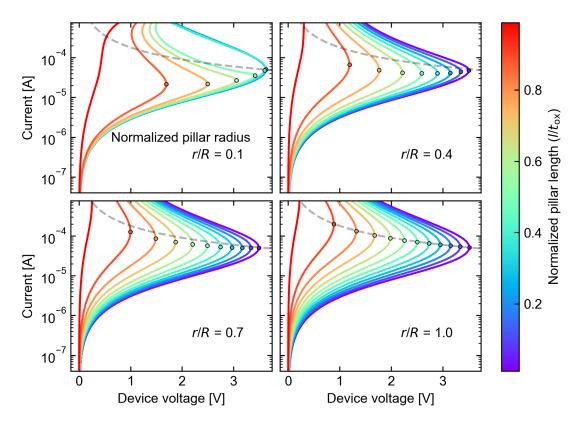

|    |       | 4.5.1                                       | Scaling of the NDR steady state     | 119 |  |

|    |       | 4.5.2                                       | Non-volatile model                  | 122 |  |

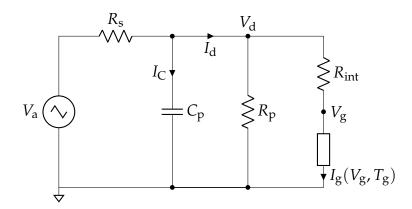

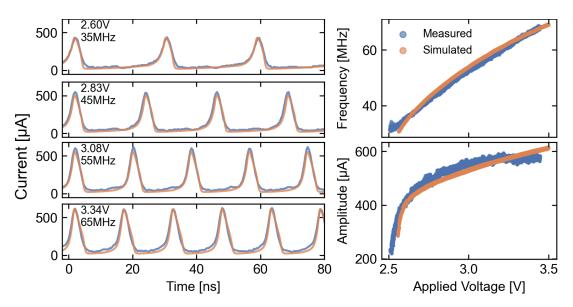

|    |       | 4.5.3                                       | Oscillatory model                   | 126 |  |

|    |       | 4.5.4                                       | Finite element analysis             | 129 |  |

|    | 4.6   | Discus                                      | ssion                               | 135 |  |

| Co | nclus | sion                                        |                                     | 137 |  |

| A  | Para  | meter                                       | assignment for the thermistor model | 141 |  |

| В  | Zoo   | of ther                                     | mistor behavior                     | 143 |  |

| Bi | bliog | raphy                                       |                                     | 145 |  |

#### List of Abbreviations

**RS** Resistive Switching

ReRAM Resistive Random Access Memory

CeRAM Correlated electron Random Access Memory

NV Non-Volatile

TS Threshold Switching

IMT Insulator to Metal TransitionNDR Negative Differential Resistance

PCB Printed Circuit Board

CLA Current Limiting Amplifier

DUT Device Under Test

CtC Cycle-to-Cycle

DtD Device-to-Device

ML Machine Learning

HRS High Resistance State

LRS Low Resistance State

IRS Intermediate Resistance State

CMOS Complementary Metal-Oxide-Semiconductor

BJT Bipolar Junction Transistor FET Field Effect Transistor

SPA Semiconductor Parameter Analyzer

SMU Source Measure Unit CC Compliance Current

VCM Valence Change Mechanism

MIM Metal-Insulator-MetalTMO Transition Metal OxideDOS Density Of States

TEM Transmission Electron Microscopy

SEM Scanning Electron Microscopy

XAS X-ray Absorption Spectroscopy

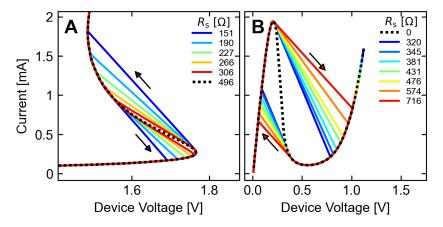

SNR Signal to Noise Ratio

CPU Central Processing Unit

GPU Graphics Processing Unit

ODE Ordinary Differential Equation

PDE Partial Differential Equation

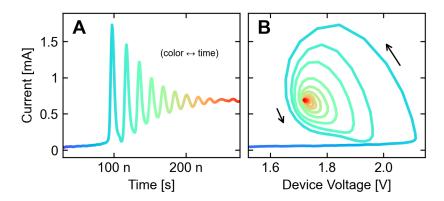

DAE Differential-Algebraic Equations

### **List of Symbols**

| Symbol           | Name                                  | Unit                           |

|------------------|---------------------------------------|--------------------------------|

| I                | Current                               | A                              |

| $I_{d}$          | Device current                        | A                              |

| V                | Voltage                               | V                              |

| $V_{\rm a}$      | Applied voltage                       | V                              |

| $V_{\rm d}$      | Device voltage                        | V                              |

| $V_{ m S}$       | SET voltage                           | V                              |

| $V_{ m R}$       | RESET voltage                         | V                              |

| P                | Power                                 | W                              |

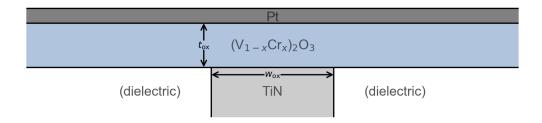

| $t_{ox}$         | Oxide/device thickness                | m                              |

| $w_{ox}$         | Oxide/device width                    | m                              |

| а                | Conduction parameter                  | S                              |

| b                | Conduction parameter                  | K                              |

| С                | Conduction parameter                  | $\sqrt{V}$                     |

| α                | Conduction parameter                  | $\mathrm{S}\mathrm{m}^{-1}$    |

| $\gamma$         | Conduction parameter                  | $\sqrt{m/V}$                   |

| T                | Device temperature                    | K                              |

| $T_0$            | Ambient temperature                   | K                              |

| $R_{ m s}$       | Series resistance                     | Ω                              |

| $R_{d}$          | Device resistance                     | Ω                              |

| $R_{\mathrm{H}}$ | Resistance of a high resistance state | Ω                              |

| $R_{ m L}$       | Resistance of a low resistance state  | Ω                              |

| ho               | Electrical resistivity                | $\Omega$ m                     |

| $\sigma$         | Electrical conductivity               | $\mathrm{S}\mathrm{m}^{-1}$    |

| $\kappa$         | Thermal conductivity                  | ${ m W}{ m m}^{-1}{ m K}^{-1}$ |

| $C_{\rm p}$      | Parallel capacitance                  | F                              |

| $R_{th}$         | Thermal resistance                    | ${ m K}{ m W}^{-1}$            |

| $C_{th}$         | Thermal capacitance                   | $ m JK^{-1}$                   |

| t                | Time                                  | S                              |

| $k_B$            | Boltzmann constant                    | $ m JK^{-1}$                   |

| $\mu_0$          | Vacuum permeability                   | $\mathrm{H}\mathrm{m}^{-1}$    |

#### Introduction

For over 75 years, the notion of a "computer" has been largely synonymous with the general purpose digital architecture attributed to the Hungarian-American polymath, John von Neumann [1]. Miniaturization, integration, and optimization of semiconductor-based electronic devices has since propelled the advancement of computer hardware in this classic architecture to the incredible level of today. However, fundamental inefficiencies of the von Neumann paradigm are becoming relevant for modern workloads, as a larger share of the available energy is spent shuttling data back and forth between storage and locations where it can be processed [2, 3]. Despite the overwhelming success of the technological strategy of recent decades, physical and economic constraints are making the same approach increasingly challenging to follow into the future [4].

Along with the rise of machine learning (ML), modern trends in computing have likewise emphasized neuromorphic architectures that implement brain-inspired algorithms directly on the hardware level [5–7]. These approaches, through in-memory computation and massive parallelism, excel in new classes of computational problems and offer promising advantages with respect to power consumption and error resiliency. While complementary metal-oxide-semiconductor (CMOS)-based neuromorphic computing (NC) implementations have made substantial progress recently [8, 9], new materials and physical mechanisms may ultimately provide better opportunities for energy efficiency and scaling [7, 10–15].

A functionality sought after in NC applications is an ability to mimic the biological building blocks of the brain; neurons and the synaptic connections between them. To cover different electronic aspects of this behavior, many schemes make use of resistive switching (RS), which refers to a broad class of related phenomena wherein the resistance of two-terminal devices can be controlled via electrical stimuli [16]. Several solid-state memory technologies in this category, such as phase-change memory (PCM), magnetic random access memory (MRAM), resistive RAM (ReRAM), and correlated electron RAM (CeRAM), are emerging as candidate components, each exploiting different material properties [11, 17–19].

Among the device candidates, ReRAM is attractive for its simplicity of materials and device structure, providing the necessary CMOS compatibility and scalability [20]. ReRAMs, also controversially called memristors [21–31], are essentially two-terminal nanoscale electrochemical cells, whose variable resistance state is based on manipulation of the point-defect configuration in an

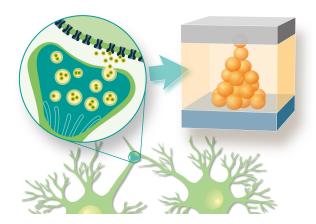

**Figure 1:** In loose analogy to biological synapses, two-terminal solid-state nanodevices such as ReRAM can store the strength of network connections as electrical resistance states. The devices, consisting simply of patterned metal-insulator-metal material stacks, have an adjustable resistance level determined by the ionic configuration inside the insulating layer.

oxide material (depicted in Fig. 1). This redox-based switching mechanism is intrinsically analog, allowing a range of stable resistance levels to be stored and adjusted through application of bipolar voltage stimuli. However, various non-idealities such as stochasticity, nonlinearity, and noise are prominent features of these devices that, for better or for worse, critically impact the performance of systems composed of them [32, 33].

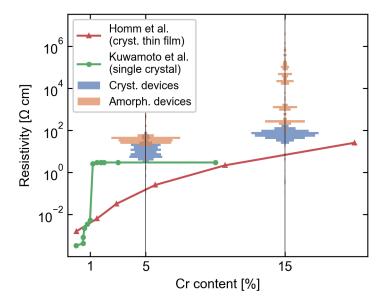

Another promising possibility currently being explored is to use electronically controlled insulator-to-metal transitions (IMTs) arising due to electronelectron correlation effects [34]. Cr-doped  $V_2O_3$  is a well-known example of a Mott insulating material supporting a particular kind of IMT called a Mott transition, which could prove to be a robust basis for future volatile or non-volatile memories [35]. At the same time, similar volatile switching phenomena commonly occur in nanodevices due to electro-thermal feedback effects, which involve either simple thermal activation, temperature-induced IMTs, or both [36, 37]. These types of devices continue to attract attention due to their interesting dynamical behavior in circuits [38–40]. The effects, which include spiking and oscillations, are viewed increasingly in the context of neural networks [41, 42].

This dissertation addresses remaining challenges in electrical characterization and modeling of synaptic and neuronal devices, as required by next generation memory and computing architectures. It is divided into four chapters. We begin in Chapter 1 by providing background information on selected volatile and non-volatile RS phenomena while introducing important concepts in electrical measurements that pertain generally to the rest of the work.

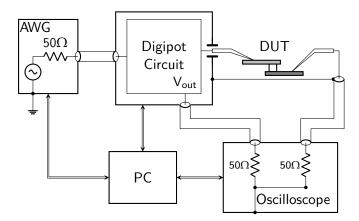

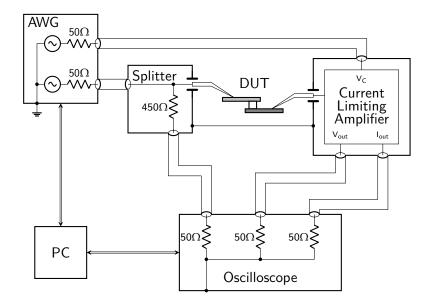

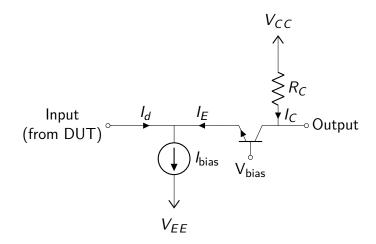

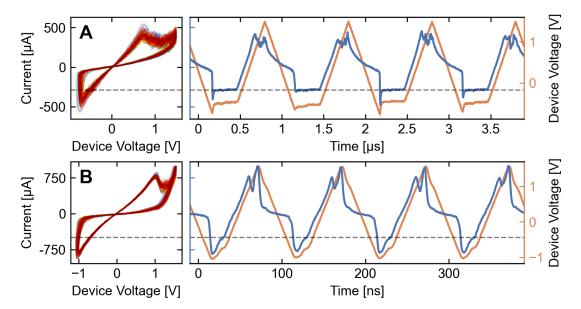

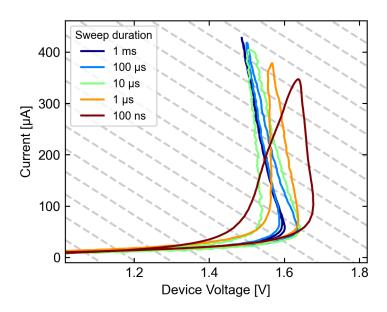

Emerging devices are based on only partially understood mechanisms, and may exhibit strong non-linearity, negative differential resistance (NDR), oscillations, stochasticity, and memory effects. In assessing the electrical capabilities of RS devices, it is important to consider not only the device material properties but also the effects of feedback, instability, excess electrical stress, and the general role of the driving circuitry on measurement data. Chapter 2 describes the design of two new measurement circuits specialized in characterization of RS. We demonstrate extraction of important statistical information from mass collection of (I,V) cycles at eight orders of magnitude faster rates than possible using commercially available equipment. This is done while also capturing important transient events during switching, which usually escape detection. The developed circuits are then employed for electrical measurements in the rest of the work.

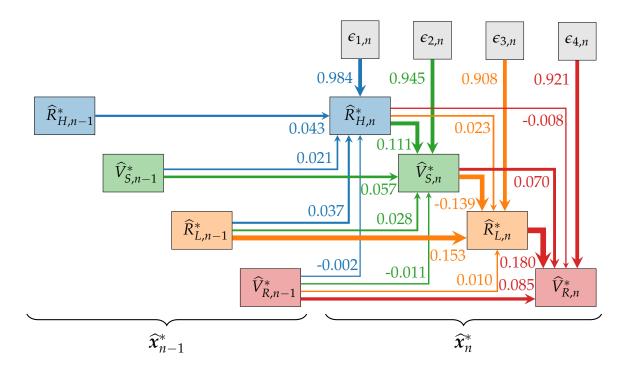

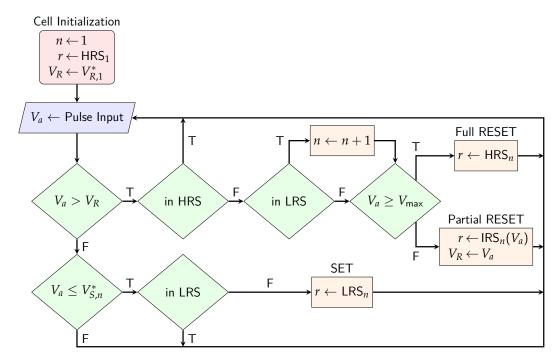

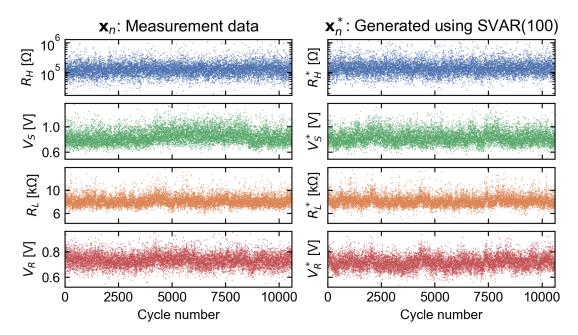

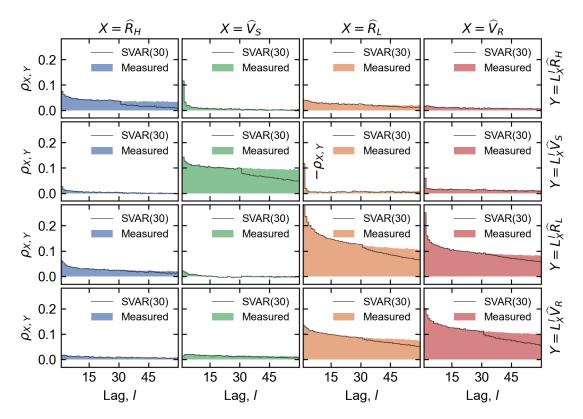

Modern ML models have reached an astonishingly large and everincreasing size, with recent examples exceeding a hundred billion weights [43]. Before comparable hardware implementations based on solid-state memories can become a reality, large-scale network designs need to first be evaluated by computer simulations. Training, validation, and optimization of such networks involves a huge number of simulated devices, voltage pulses, and current readouts. Within this process, it is important to accurately consider the constraints of the underlying hardware in detail. Therefore, lightweight, fast, and accurate stochastic simulations of the individual synaptic devices are a key requirement. In Chapter 3, we present a new data-driven approach for modeling large collections of stochastic synapses. We created a hierarchical statistical model based on vector autoregression and probability density transformation, which replicates the measured stochastic behavior of memory cells very closely. We provide high-performance, parallelized implementations for both CPUs and GPUs and demonstrate simulation of over one billion cells simultaneously with throughputs exceeding one hundred million weight updates per second.

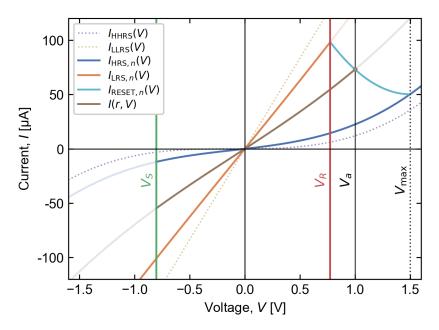

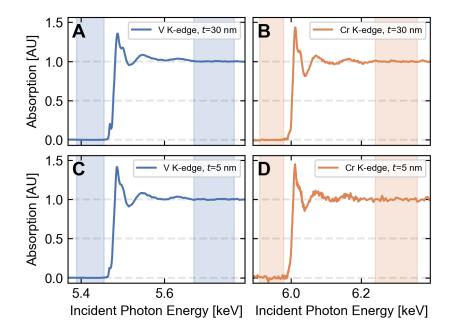

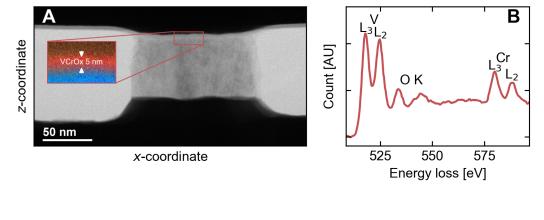

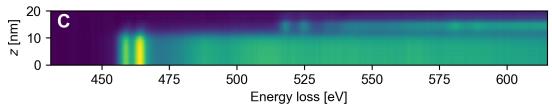

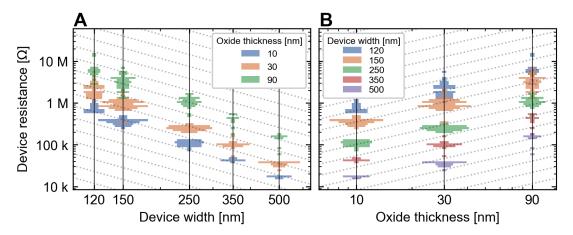

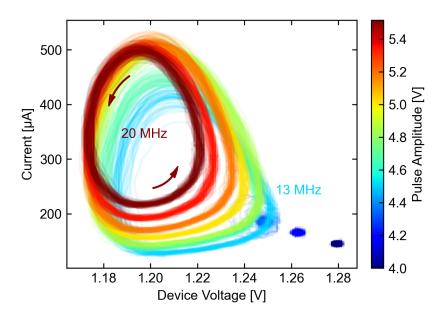

In Chapter 4, nano-devices based on the Mott-insulating material  $(V_{1-x}Cr_x)_2O_3$  are investigated. The electronic structure of the material is probed with synchrotron X-ray measurements, and the electrical operation of corresponding nano-patterned devices is extensively characterized. Among the results are a volatile NDR effect with below ten nanosecond switching speeds, endurance over a trillion cycles, and oscillatory modes in the tens and hundreds of megahertz range [44, 45]. The device operation clearly involves an electro-thermal mechanism as a volatile precursor to a separate non-volatile switching mechanism, which is likely of nano-ionic origin. New insights are inferred from careful electrical measurements of the various states that can be set up in the devices by using current-limiting feedback. These insights address the question of how the conductivity inside the switching material is spatially redistributed as a result of NV switching operations, and specifically how the degree of filamentation is connected to the material properties and to the measurement conditions. Finally, physics-based differential equation models are developed to fit the measured dependence

of time, temperature, and length scale on device operation, which enable simulations of neuromorphic systems based on these devices [46].

#### Chapter 1

#### **Fundamentals**

This chapter introduces the different memory technologies studied in this dissertation, mainly in the context of electrical measurement; the principal experimental tool used in the work. Section 1.1 first covers ReRAM based on the electro-migration of oxygen vacancies, and Section 1.2 discusses the correlated electron material  $(V_{1-x}Cr_x)_2O_3$ . Section 1.3 is concerned with the challenges in electrical measurement of these devices and how they relate to current practices. Finally, in Section 1.4 we take a step back to look at the ubiquitous effect of device Joule heating, providing illustrative examples useful for understanding simple measurement situations where coupling with the impedance of an external measurement circuit has unexpected consequences.

#### 1.1 Redox-based resistive switching mechanisms

All insulating layers suffer a loss of their insulating properties if a sufficient voltage is forced across them for a sufficient amount of time. The mechanisms of this so-called dielectric breakdown effect are various [47], but commonly involve an instability where the driving force of the physical processes responsible for the increasing material conductivity is subject to positive feedback. This runaway process can rapidly lead to structural or chemical changes in the insulator, eventually forming a conductive pathway through the material which may persist long after the electrical stimulus is removed.

Left unimpeded, the destructive effects of breakdown are considered an irreversible phenomenon, leaving no possibility to recover an insulating state. This breakdown effect has been thoroughly investigated in the field of oxide reliability, where its role in the failure of thin gate oxides make it an effect to be avoided. However, the field of resistive switching (RS) takes a different perspective on the same class of effects. The basic objective of RS is to interrupt the process before it causes permanent and irreversible damage to the material, so that the device resistance state can be repeatedly and reliably modulated by applying voltage signals with alternating polarity, duration, or amplitude. Provided that such devices can be (re)programmed to stable resistance levels, they can then be employed as binary or multi-level non-volatile memories, or as weights in an artificial neural network.

Non-volatile RS effects occur in a wilderness of different materials, and essentially every thin insulating layer between two electrodes can show persistant and reversible resistance transitions. This amusingly includes beer, whiskey, bananas, honey, leaves, and milk [48–52]. Broadly speaking, a class of RS can be distinguished by the involvement of mobile defects in the material that locally increase its conductivity. Different spatial configurations of the defects with different total resistance levels can be set up through migration of the defects under the applied field as well as temperature and/or concentration gradients. A detailed classification of these effects has been made according to the insulating and electrode materials used and to the type of defects responsible for the switching effect [16], though the switching mechanisms and modes are not all mutually exclusive and can occur under different types of electrical control and in statistically overlapping regimes [53–56].

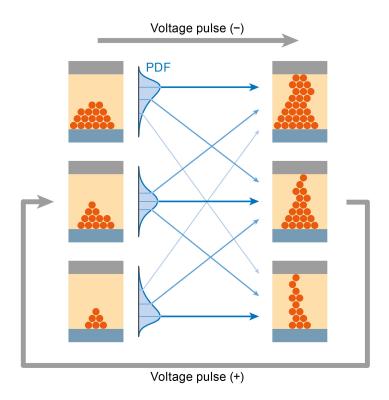

**Figure 1.1:** Resistance states in VCM-based ReRAM devices depend on the configuration of oxygen vacancy defects (drawn as orange circles) in the oxide layer. Application of voltage pulses can produce new states, which exhibit a probabilistic dependence on past states, leading to long-range correlations. Starting with effectively infinite state possibilities (represented by the three cell states on the left) an applied voltage pulse brings about a set of transition probabilities to many possible subsequent states (right).

For the specific case of the valence change mechanism (VCM) that is employed in the ReRAM investigated in this work, the non-volatile effect is mediated by oxygen vacancy defects in a binary transition metal oxide (TMO)

resistive layer, which act as mobile electron donors to increase the local material conductivity [20]. The oxygen vacancies, either already present in the deposited oxide (e.g. TaOx or HfOx) or generated through redox reactions at the oxide/electrode interface, then drift under the applied electric field, with their mobility activated by Joule heating. Under a constant applied voltage, a rising concentration of oxygen vacancies locally increases the driving force for their production and/or migration (namely, the electric field and temperature), causing the defects to assemble and form one or more filamentary conductive paths through the film [57–60].

The basic requirement for an electronic device serving as an artificial synapse is to moderate the flow of electrical signals through connections in a network. Left undisturbed, the device ideally maintains a fixed weight, or dependence between the voltage across the two device terminals, V, and the resulting current through the device. Further, for learning there must be some means of affecting the weight in a durable way. Bipolar ReRAMs have an adjustable (potentially nonlinear) and non-volatile resistance state, which is based on the size and shape of a conducting filament that partially or fully bridges the insulating gap of the oxide material. Simplistically, when V exceeds certain threshold levels, the resistance state begins to transition toward lower or higher values depending on the voltage polarity, which corresponds to growth and shrinkage of the conducting filament. When the filament only partially bridges the insulating gap, conduction may be limited for example by tunneling through a Schottky barrier of a material interface, leading to a relatively high resistance levels [20, 61]. As the filament grows and gradually bridges the gap, the resistance decreases as conduction transitions towards the ohmic type.

There are a number of technologically promising features of VCM-based ReRAMs that make them attractive for next generation memory and computing architectures [12]. The simple device structure can be fabricated using a wide variety of CMOS-compatible materials [62, 63]. ReRAMs also have good write endurance [64], support high read/write speeds [65–68], and have strong potential for 3D integration [69]. Importantly, the effect can be scaled to nanometer dimensions as only a small number of ions need to participate in the switching process in principle [70–72].

However, several drawbacks currently stand in the way of widespread application of these devices. These stem from the fact that filamentary states in the material are electrically delicate, prone to instability, and the transitions between the states are strongly stochastic (see Fig. 1.1). Therefore, a central challenge for ReRAM devices is dealing with the intrinsically random nature of their switching processes, which leads to large variability in the programmed resistance states and switching parameters [73, 74]. Achieving an acceptable level of control of ReRAM devices will require an in-depth understanding of the statistical processes at play, as well as an optimization of the active materials together with the control circuitry.

## 1.2 Correlated electrons and the vanadium oxide system

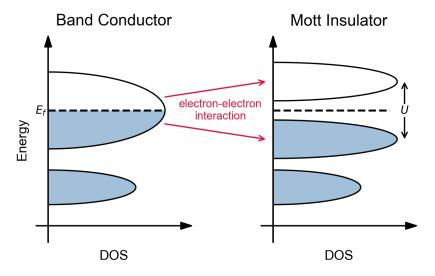

Mott insulators, named after the 1977 Nobel leureate Sir Nevill Francis Mott, are a class of materials with unusual electronic properties arising due to strong electron-electron correlation effects. Simplistic models used to calculate the electronic band structure of these materials neglect the electron-electron interactions and predict a conductive ground state. However, an insulating state in fact arises because, essentially, Coloumb repulsion suppresses the transfer of electrons from one atomic site to another. This phenomenon is treated approximately in the single band Hubbard model, where a Hamiltonian describes a competition between the forces of kinetic energy and the on-site repulsive potential [75]. In Mott insulators, the electron correlation effect causes a splitting of the electron bands as shown qualitatively in Fig. 1.2 [76].

Figure 1.2: In the Hubbard model, half-filled conduction bands are split into upper and lower Hubbard bands due to electron-electron interactions. Depending on the balance between the bandwidth and the Hubbard energy, U, the material may be in a Mott insulating state.

Mott materials are good insulators, yet they are precariously close to being conductors. Insulator to metal transitions (IMTs) can be induced by various physical stimuli such as temperature, pressure, or doping [77]. It was recently shown that Mott insulators subjected to electric pulses can undergo an IMT linked with the creation of a conducting filamentary path [78]. This raises fundamental research questions about whether these transitions can be harnessed to create new scalable device technologies: are they suitable materials for memory, selectors, or neuromorphic elements [79]?

The binary vanadium-oxide system has been intensely studied since the early beginnings of condensed matter physics. It known to exist in over 20 different stable phases, many with IMT behavior due to correlated electron effects [80, 81]. The sesquioxide system  $(V_2O_3)$  is a famous example of a material

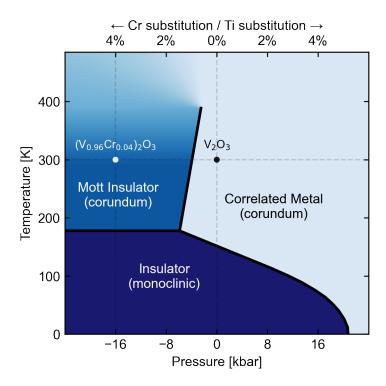

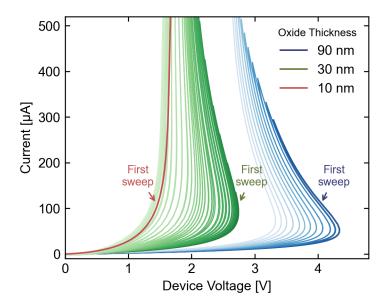

with a canonical Mott IMT that can be driven by pressure or doping, as shown in the phase diagram of Fig. 1.3. Under ambient conditions,  $V_2O_3$  is a correlated metal, but substitution of a few percent of the V sites with Cr biases the material in a Mott insulating state. IMTs have been observed in  $(V_{1-x}Cr_x)_2O_3$  thin films, where they are known to depend very sensitively on the stoichiometry, phase, and strain conditions [82–86]. Application of short electric pulses to the material can also induce an isostructural IMT, which is a possible basis for volatile or non-volatile memory applications [34, 35, 87]. Due to the advanced lithography nodes, very thin functional layers below 10 nm are a key requirement for all of these envisioned applications. At such small thicknesses, stoichiometry and phase purity become increasingly difficult to characterize, and the interface of the oxide with the substrate plays an important role which can serve either to facilitate or hinder the Mott transition behavior.

**Figure 1.3:** Phase diagram of  $(V_{1-x}Cr_x)_2O_3$  vs. concentration of the Cr dopant (x), pressure and temperature. Doping brings the correlated metal into an insulating state, which can theoretically be switched back to the metallic state using an applied voltage. Pressure and doping are shown as having equivalent effects on the phase, though this has been refuted [88]. Data was extracted from [89].

In Chapter 4, the electronic structure of  $(V_{1-x}Cr_x)_2O_3$  films as thin as 5 nm is probed by X-ray absorption spectroscopy and switching behavior in corresponding high-quality nanodevices are scrutinized through different kinds of electrical measurements.

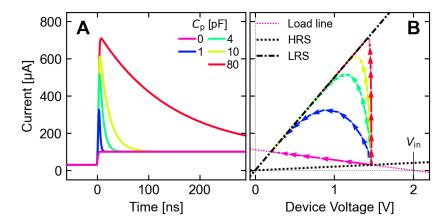

#### 1.3 Electrical measurements of resistive switching

An electrical measurement records the response (i.e. the current and/or voltage at specific nodes/branches) of a particular driving circuit when a test device is connected at its measurement terminals. In the case of RS, the stochastic two-terminal devices are elements of the circuit that simultaneously measures and controls them. Resistance transitions in RS materials can occur on timescales below 1 ns [66–68], but the nanoscale material volumes involved cannot normally survive prolonged exposure to the voltage required to initiate the transition, as the current density quickly reaches levels that can cause irreversible damage [90]. To prevent this and to keep the process in a reversible regime, a strategy is necessary to limit the duration and amplitude of voltage applied to the active part of the device during switching.

A challenging aspect of electrical characterization of RS devices is that measurements depend not only on the materials and structures used in device fabrication, but are also sensitively dependent, often in unexpected ways, on the measurement circuitry used. Generally, this is a consequence of coupling between the ultra-fast physical dynamics of the device under test (DUT) and the frequency-dependent feedback of the external driving circuit. Together, these coupled dynamics determine the current and voltage trajectories experienced by the DUT through time during its resistance transitions. Parasitics in the system have a large influence because they can store and release energy comparable to, or in excess of, what is needed to induce switching in the nano-scale material volumes. Thus, electrical measurements often do not probe device characteristics directly, and easily overlooked details of the test system, such as the model number of an instrument or the stray capacitance introduced by a short length of coaxial cable, can have an important impact on switching data [91–94].

Another fundamental challenge in using electrical measurement as an experimental technique relates to a concept known in control theory as observability [95]. Device stochasticity and path-dependence originate from nanoionic processes which occupy an extremely high-dimensional physical state space, but these internal states are difficult to infer using the few output signals available for electrical measurement. In other words, currents and voltages are a very indirect probe of what is really happening inside of the device, and the resulting data is therefore subject to many conflicting interpretations. On top of this, electrical instrumentation is technically complicated, and there are many sub-optimal ways to measure that still produce (I, V) data in a similar format. This data tends to be detached from critically relevant measurement details, which further impairs the chance for a productive interpretation.

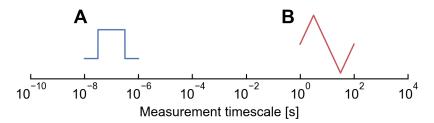

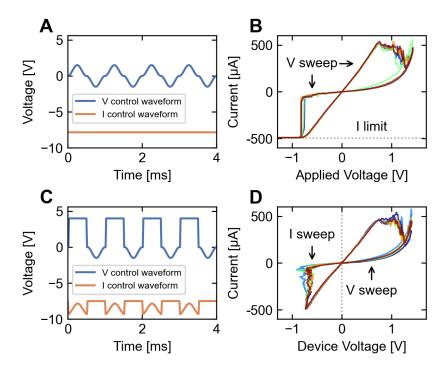

Notwithstanding a diversity of experimental possibilities to address this seemingly bleak situation, reported RS electrical measurements overwhelmingly fall into the two categories represented in Fig. 1.4. To a large extent, these techniques were inherited from existing standards, methods, and equipment used in optimization of semiconductor devices, without specific adaptation to the unique challenges faced by RS devices [96–99].

**Figure 1.4:** Conventional electrical measurements of RS devices largely fall into two rigid categories. Voltage driving signals are applied directly to the DUT and are either **(A)** square pulse waveforms on short timescales or **(B)** (quasistatic) sweeps at very low frequency.

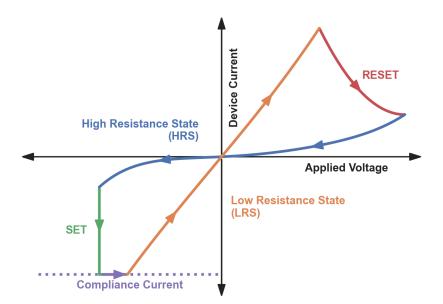

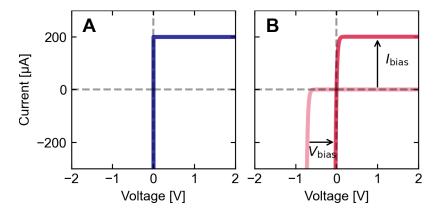

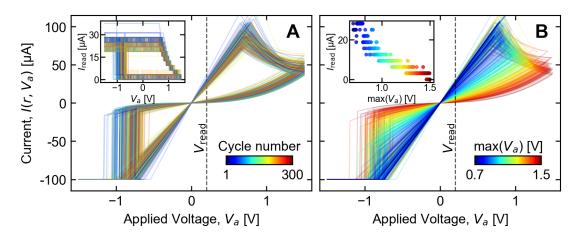

Quasistatic (I, V) loops are a measurement where resistance switching is induced by an applied voltage that is continuously ramped at low speed  $(\sim 1 \text{ V/s})$  between positive and negative values. The device current at each point of the sweep is sampled, and can be plotted against the applied voltage as shown schematically in Fig. 1.5. Such (I, V) loops are rich in information, and important features such as the (I, V) non-linearity, voltage and current switching thresholds, and details of the transition behavior can be extracted from each cycle. With very few exceptions [100, 101], sweeping (I, V)measurements are performed using commercial source measure units (SMUs), which can be contained inside instruments called semiconductor parameter analyzers (SPAs). These instruments, while offering extremely high resolution and dynamic range, rely on signal averaging on the scale of the power line frequency (50 Hz or 60 Hz) and are therefore limited to very slow measurement sweep and sample rates. In addition to making experiments involving more than a few hundred switching cycles impractical, this long timescale is 6 to 9 orders of magnitude larger than those relevant for applications, which puts excessive electrical stress on these highly time-dependent devices [102].

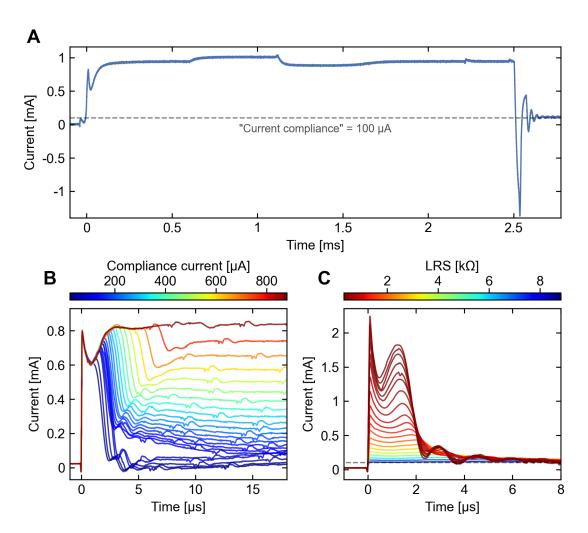

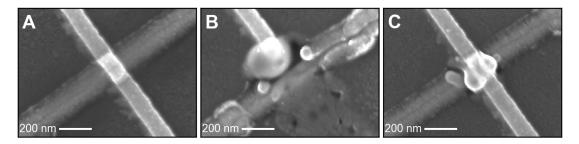

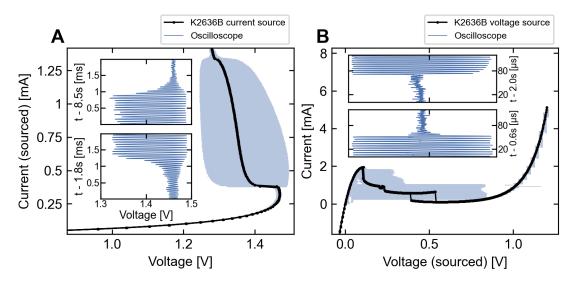

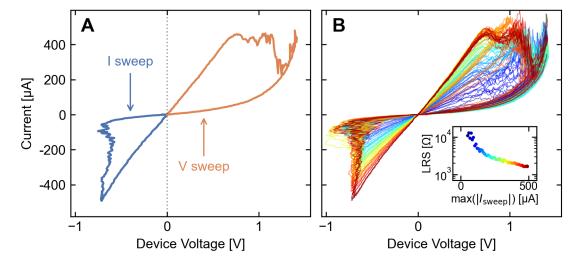

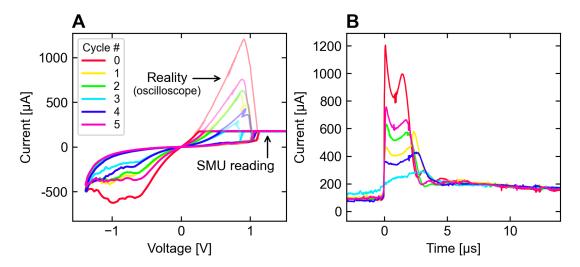

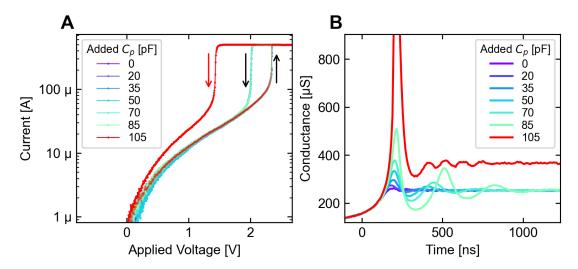

Sweeping (*I*, *V*) loop measurements are only generally possible with the use of a feedback mechanism to prevent runaway destruction of the RS device. However, externally implemented current limiting such as the current compliance (CC) function of commercial SMUs and SPAs are known to permit large current overshoots during resistance transitions in the time before CC is eventually enforced (shown in the test measurements of Fig. 1.6). These overshoots can lead to catastrophic damage to cells [103, 104] (see Fig. 1.7) and can otherwise strongly influence the measurements [105, 106]. At the same time, overshooting transients can not be recorded by the instrument itself because of its low bandwidth and sampling rate, and resistance cycling may procede while leaving no direct evidence of poor control in the experimental data.

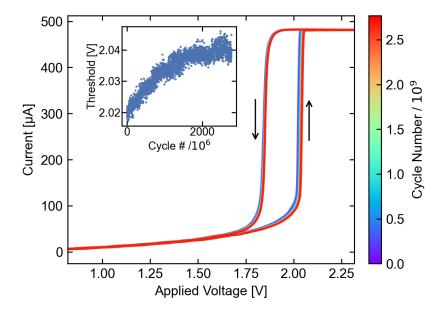

Overshoots are only one manifestation of the deficiency of SMUs when applied to switching devices, as the instrument designs do not anticipate fast changes in a two-terminal conductance which is driven by the measurement voltage itself. Even using the appropriate (voltage/current) sourcing mode, the instrument can return spurious data as it induces oscillations in NDR

**Figure 1.5:** Schematic diagram of a single bipolar ReRAM (I,V) loop cycle. A voltage applied to the active electrode is swept in order to induce resistance switching while simultaneously measuring the device current. A feedback system interrupts runaway breakdown during the SET transition by attempting to enforce a current limitation (compliance). Important switching parameters such as threshold voltages and nonlinear resistance states can be extracted from (I,V) loop measurements, which show significant statistical variation both between devices and between cycles.

devices that it does not have the measurement bandwidth to resolve, as demonstrated in Fig. 1.8. This stability issue can arise when cells are driven by an ideal source with too high output capacitance, following the general mechanism to be described in Section 1.4.3, and also pointed out recently by Brown et al. [99]. However, the actual situation is far more fraught. To measure RS with an SMU is to investigate incompletely understood switching mechanisms by driving the cells with a slow, proprietary feedback circuit with an unpredictable dynamical response; conditions quite unlike any that would be produced in any integrated system of interest. Even in the subset of cases where instability is thought not to play an important role, the sheer uncertainty introduced by the misapplication of these machines makes them counter-productive to use for switching experiments, and doing so can cause long lasting damage to the understanding of RS effects.

Patterning RS devices directly on MOS transistors can provide superior current limiting and stability, but the required integration limits the materials available and necessitates long fabrication cycle times [105, 107, 108]. A simpler approach from the point of view of fabrication is to integrate fixed resistors on the chip in series with the devices [90, 100, 109, 110, 260]. However, the large linear feedback introduced by this relatively inflexible method significantly affects the switching behavior [111, 112], and can push the operating

voltage outside of a practical range. On the other hand, attempts to control RS using external current-limiting components such as resistors [90, 103–105, 110, 113–121] or transistors [91, 92, 122–125] struggle with issues related to the parasitic capacitance, among other shortcomings. In Chapter 2, we address these measurement challenges with two new experimental setups, which use external circuitry to measure (I, V) traces at high frequency using arbitrary waveforms while minimizing unwanted overshoots.

Figure 1.6: Current overshoot transients delivered to surface mount resistors by Keithley SMUs, set to source 1 V, as measured by an oscilloscope. At time t=0 the DUT resistance was suddenly switched from an initially high resistance (HRS) to a lower resistance (LRS) via a low capacitance relay. (A) Model 2410 with CC level set to  $I_{cc} = 100 \mu A$  while switching from 1 M $\Omega$  to 1 k $\Omega$ . The current limiting feedback is unresponsive for 2.5 ms after switching; a very long duration relative to ReRAM switching times. The test resistor is also subjected to a large oscillatory current that includes reverse polarities. Model 2636B SMU shows an improved but still inadequate response when switching from an HRS of 43 k $\Omega$ , (B) with the LRS fixed to 1 k $\Omega$  and varying  $I_{cc}$ , and (C) with  $I_{cc}$  fixed to 100  $\mu$ A while varying the LRS. These overshoots are invisible in the data returned by the SMUs, because their duration is far lower than the averaging period for a single measurement sample. No matter the CC setting, the transients are identical for at least 1 µs because the initial spikes are delivered directly by the coaxial cable.

Figure 1.7: Damage induced by current overshoots in 100 nm crossbar structures with 30 nm Pt top and bottom electrodes and a 100 nm VOx switching layer. The initial structure before measurement is shown in (A). Device (B) was subjected to a voltage sweep by an SMU with a 15 μA current compliance setting. Device (C), protected by a 10 kΩ external series resistor, was swept similarly, but was still damaged by the capacitive discharge of an interconnecting 20 cm coaxial cable. Although the cells are visibly destroyed, both nevertheless continued to show measurable RS behavior as a conducting path still existed through what remained of the oxide material.

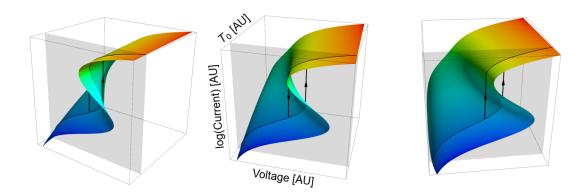

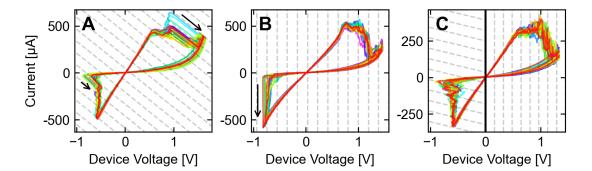

**Figure 1.8:** Source measure units (SMUs) cannot reliably measure NDR of either S- or N-type, as demonstrated in **(A)** an S-type  $(V_{0.85}Cr_{0.15})_2O_3$  nanodevice  $(500\times500\times30~\text{nm}^3)$  and **(B)** an N-type 3I306E Ga-As tunnel diode. In both cases, oscillations are induced and the averaged curves returned by the SMU are inaccurate and potentially misleading.

#### 1.4 The electro-thermal switching mechanism

When electrical current flows through a resistive medium, Joule heating always results; this is a basic consequence of work done on the charge distribution by the Lorentz force. At the same time, it is also common for a material's conductivity to be strongly affected by heating. For semiconductors, the conductivity usually increases through thermal activation of charge carriers over a band gap or over trap barriers [126, 127]. Surprisingly, these two properties alone can lead to highly unintuitive behavior in circuits built with electro-thermal components [128, 129]. Even in relatively simple circuits, the dynamics are coupled such that under different conditions they can exhibit bifurcations, oscillation, and chaos [99, 130, 131].

Due to its general ubiquity in nanodevices, it is important to first consider the effect of thermal feedback in isolation. Therefore, this section gives a conceptual framework for understanding electrical measurements of two-terminal devices that have a large temperature dependence of their conductance. Using suitable simplifications, a relatively tractable analysis serves as a good prototype for surveying the variety of dynamics that can occur. This straightforward example also provides an essential base layer for understanding the behavior of more complex devices, for which such thermal effects are often strongly involved [132, 133]. In particular, this section provides the context in which the various results of Chapter 4 can be best interpreted.

#### 1.4.1 Thermistor dynamics

To introduce a deliberately minimal example, suppose two metallic electrodes make contact with a uniform cuboid of semiconducting material on opposing faces. Assume uniform electric field lines perpendicular to the electrode planes and that the temperature T inside the cell volume is always uniformly distributed. Suppose the medium has thermally activated charge carriers such that the total device conductance follows a voltage-independent Arrhenius equation,

$$G = \frac{I}{V} = A \exp\left(\frac{-E_{\rm b}}{k_{\rm B}T}\right),\tag{1.1}$$

where I and V are the device current and voltage drop, A is a pre-exponential current constant,  $E_b$  is the activation energy barrier,  $k_B$  is the Boltzmann constant.

The device heating rate can be calculated as a balance between the power generated by Joule heating and that lost to the cell surroundings by conductive heat transfer. Assuming a constant lumped heat capacity  $C_{th}$  of the cell, we have

$$C_{\rm th} \frac{dT}{dt} = P_{\rm in} - P_{\rm out}. \tag{1.2}$$

The Joule heating term is a product of the instantaneous device current and voltage difference across its electrodes,

$$P_{\rm in} = IV, \tag{1.3}$$

and Newton's law of cooling can be applied to approximate the rate of heat conduction out of the cell boundaries as

$$P_{\text{out}} = \frac{T - T_0}{R_{\text{th}}}. ag{1.4}$$

Here, the cooling rate is simply proportional to the difference between the cell temperature and the ambient level  $T_0$ . The thermal resistance  $R_{th}$  quantifies the thermal contact with the cell environment and depends on the cell size as well as the surrounding materials.

A convenient property of the conduction Eq. 1.1 is that any possible non-zero (I, V) condition unambiguously identifies the temperature state of the cell. This allows equations 1.1–1.4 to be combined in order to express the temperature dynamics as a single ordinary differential equation (ODE) in terms of only the electrically observable variables I and V,

$$\frac{dT}{dt} = \frac{1}{C_{\text{th}}} \left[ IV + \frac{1}{R_{\text{th}}} \left( \frac{E_{\text{b}}}{k_{\text{B}} \log \left( \frac{I}{AV} \right)} + T_0 \right) \right]. \tag{1.5}$$

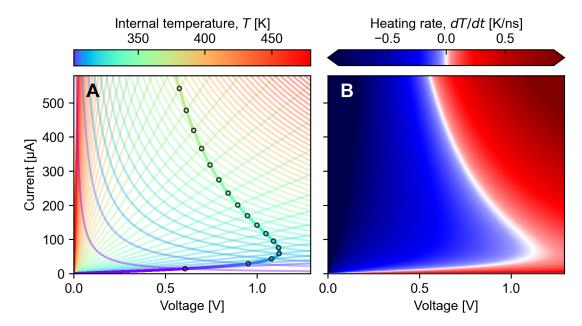

A visualization of this unwieldy equation (Fig. 1.9) is a useful step toward a qualitative understanding of its dynamical behavior. For the sake of concreteness, values for a hypothetical nano-scaled cell are assigned to the model parameters, following the reasoning in Appendix A.

The first task in analyzing any dynamical system is to identify the conditions under which the state variables do not change in time. In the case of this first-order system, parameter and variable values consistent with the condition  $dT/dt = 0 \, \text{K/s}$  are called the fixed points of the model. Referring to Fig. 1.9, we see that for a given set of parameters, a projection of dT/dt on the (I, V)-plane shows a smooth continuous curve of fixed points that separate two regions of net heating  $(dT/dt > 0 \, \text{K/s})$  to the right and cooling  $(dT/dt < 0 \, \text{K/s})$  to the left. This curve can be understood as the set of (I, V) points for which the input power equals the power lost to the cell surroundings, such that its temperature remains stationary. As the distance of an (I, V) point from the curve increases, the disparity between the input and output power grows, which leads to larger rates of heating or cooling. Along the curve, the steady-state temperature is continuously elevated above the ambient level in proportion to the total input power, with

$$T_{\text{fixed}} = T_0 + R_{\text{th}}IV. \tag{1.6}$$

The fixed point curve is an important characteristic of the thermistor whose shape depends on a balance of electrical and thermal factors. A particularly

**Figure 1.9:** A projection of thermistor fixed points  $(dT/dt=0~{\rm K/s})$  on an (I,V)-plane show a continuous curve with S-type NDR. **(A)** Solutions are visualized as the intersections of likecolored lines. Lines radiating from the origin represent the conduction Eq. 1.1 and lines of constant power show the corresponding conditions for thermal equilibrium  $P_{\rm in}=P_{\rm out}(T)$ . **(B)** The rate of change of the thermistor temperature depends on the instantaneous voltage and current through the device with respect to the NDR curve. On the left of the curve there is net cooling, on the right there is net heating, and the cooling/heating rate increases rapidly with the distance to the curve.

consequential feature that can arise here is NDR, or a negative value of dV/dI somewhere along the curve. In this case, the set of (I, V) fixed points can also be called the NDR curve of the cell. Unfortunately, substitution of  $T_{\rm fixed}$  into a conduction equation with an Arrhenius-like temperature dependence (e.g. Eq. 1.1), tends not to have an analytical solution for V(I), but NDR curves can still be treated numerically and graphically. Regions of NDR can appear and disappear as the model parameters vary. The general topology of this can be seen by extending fixed point projection into a third dimension in the vicinity of an (I, V)-plane with NDR. For example, as the ambient temperature  $T_0$  varies, the fixed points lie on a continuous, multivalued surface reminiscent of the cusp geometry studied in catastrophe theory (Fig. 1.10) [134].

Although its temperature and therefore its conductivity can change significantly under external bias, the thermistor returns to its original temperature state ( $T = T_0$ ) after a period of time without bias. Therefore, in a memory context it can be referred to as a *volatile* switching device; resistance state changes are temporary and the device does not retain any memory of past states after power is removed for a sufficient amount of time.

Figure 1.10: Projection of the thermistor fixed point manifold  $(dT/dt=0~{\rm K/s})$  in the 3D space of voltage, current, and ambient temperature  $T_0$ , shown from three separate points of view. The surface color corresponds to the internal cell temperature T. The black path shows transitions in the stable points of the system when the voltage is viewed as a swept control variable at room temperature. For high enough values of  $T_0$ , the NDR disappears.

#### 1.4.2 The geometry of volatile switching

The discussion leading up to the differential equation Eq. 1.5 considers only the internal properties of a thermistor device. However, the NDR curve alone does not tell us what happens in a measurement of the device, nor whether any of the NDR points will necessarily be observed. In order to talk about a measurement, we first need to specify the external circuit that drives it. Mathematically, this may require adding extra equations to the system that act as constraints or add additional dynamical state variables. An analysis of measurable behavior and types of control then centers around an understanding of stability of the overall circuit.

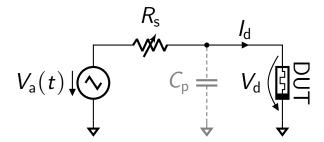

For the purposes of this discussion, we confine our attention to an external measurement circuit containing an external series resistance and a (parasitic) parallel capacitance. We will also consider the effect of internal resistances, which are often an unintentional side effect of fabrication, coming from the electrode leads for instance, but can also be a deliberate part of the cell design. The connection of the considered circuit components is shown in the schematic of Fig. 1.11. Variations of the component values in this circuit encompass many common measurement configurations, both ideal and practical. For example, when  $C_p = 0$  pF, limiting cases include ideal voltage sourcing ( $R_{\rm s,ext} \to 0$   $\Omega$ ) and current sourcing ( $R_{\rm s,ext} \to \infty$   $\Omega$ ). In practice, a non-negligible value of  $C_p$  is present, and its consequences will also be discussed. Although capacitances between the internal nodes of the circuit may also be present, they are typically much smaller in suitably designed nano-scale test structures than the external value due to the probing interconnect (femtofarads vs. picofarads), and will be neglected here for simplicity.

# External circuit $R_{s,ext}$ $V_d$ $V_d$ $V_{a(t)}$ $V_{a(t)}$

**Figure 1.11:** Generic form of the measurement circuit under consideration, split into sections that are external and internal to the test chip. Internal resistances may be present in series and in parallel with an electro-thermally active volume. A time varying voltage source drives the measurement and an ideal ammeter samples the current on the return path.

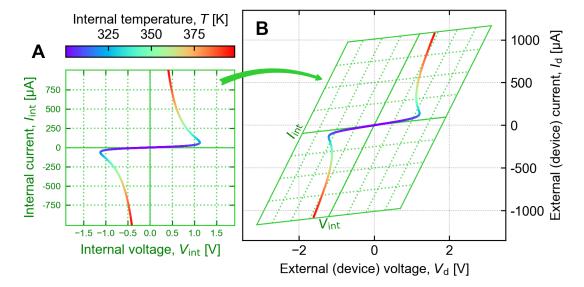

Two-dimensional plots of data are arguably the most important tool in the scientific arsenal for augmenting human intelligence. As such, electrical measurement data are commonly represented on plots of important variable pairs such as current vs. voltage. However, there are several different voltages and currents that appear in a measurement circuit which could be potentially measured and plotted, and the form of the (I, V) curves are meaningfully different depending on which I and V are selected, as well as on the methods used for their measurement. Furthermore, it is not always practical to make a direct measurement of the most relevant voltage/current for a given analysis, which affects the way the data should be interpreted. Therefore, to avoid ambiguity, (I, V) plots always need to be given in context of a circuit diagram that clearly identifies the locations of the measured signals. In the present case, for non-negligible internal resistance values, the measurable device voltage  $V_{\rm d}$ and current  $I_d$  are different from the variables V and I in the equations of the preceding discussion, which are replaced in the circuit schematic by  $V \to V_{\rm int}$ and  $I \rightarrow I_{\text{int}}$ . These internal values are those across the active volume of the cell which drive possible resistance transitions, but are not measured directly.

In this simplified case where there are no internal reactive components, the voltages and currents in question are related by the linear transformation

$$\begin{bmatrix} V_{\rm d} \\ I_{\rm d} \end{bmatrix} = \begin{bmatrix} 1 & R_{\rm s,int} \\ \frac{1}{R_{\rm p,int}} & \left(1 + \frac{R_{\rm s,int}}{R_{\rm p,int}}\right) \end{bmatrix} \begin{bmatrix} V_{\rm int} \\ I_{\rm int} \end{bmatrix}. \tag{1.7}$$

Importantly, this transformation affects the shape of NDR curves from the

point of view of the external measurement circuit, as shown in Fig. 1.12. Therefore, the values of the internal resistances can determine whether and in which range NDR appears, and is also one of several ways for the curve to return to positive differential resistance (PDR) after an intermediate region of NDR.

Figure 1.12: (A) Internal  $(I_{\rm int},V_{\rm int})$  characteristics are linearly transformed into (B) external  $(I_{\rm d},V_{\rm d})$  characteristics by measurement through internal resistances. This has important implications for the stability of the overall circuit because it distorts the external view of NDR curves. The plotted NDR data is the simulated steady-state of a thermistor volume with  $R_{\rm s,int}=1.2~{\rm k}\Omega,~R_{\rm p,int}=20~{\rm k}\Omega.$

As for the influence of  $R_{s,ext}$ , consider first the case where  $C_p$ =0 pF. Here, any measurable switching trajectory ( $I_d$ ,  $V_d$  vs. t) is constrained by a one dimensional "load line", fixed by the values of  $R_{s,ext}$  and the applied voltage  $V_a$ :

$$V_{\rm d} = V_{\rm a} - I_{\rm d} R_{\rm s,ext}. \tag{1.8}$$

The space representing each possible state of a dynamical system is called its phase space. Although the cell temperature T is the sole physical state variable of this system, a segment of the load line can also be viewed as a proxy phase space, due to a one-to-one correspondence with T. The load line can have up to three intersections with the  $(I_{\rm d},V_{\rm d})$  NDR curve, which define the remaining, discrete fixed points of the overall circuit  $(dI_{\rm d}/dt=0~{\rm A/s}$  and  $dV_{\rm d}/dt=0~{\rm V/s})$ . In the autonomous case  $(V_{\rm a}$  constant in time),  $(I_{\rm d},V_{\rm d})$  will move along the load line from the initial condition toward one of the stable fixed points, corresponding to a final steady-state cell temperature. However, in loose analogy with the Newtonion situation of a ball on a hilly landscape, not all of the NDR intersections are *stable* fixed points (see Fig. 1.13). Near any fixed point, the heating and cooling rates are relatively slow, and stability is determined by whether or not the circuit restores the temperature to the fixed point level after an inevitable perturbation.

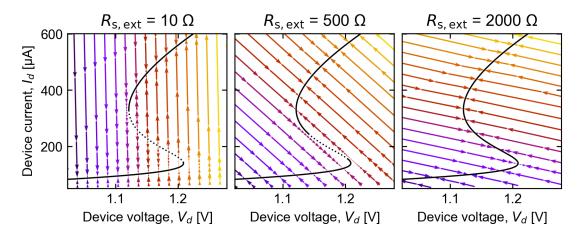

Figure 1.13: A visualization of the load-line dynamics in a thermistor measurement with negligible capacitance,  $C_{\rm p}$ . Each arrow represents a duration of 0.8 ns, following the load lines colored according to different applied voltages  $V_{\rm a}$ , for three different values of external series resistance  $R_{\rm s,ext}$ . Depending on  $R_{\rm s,ext}$ , the NDR curve is divided into monostable and bistable ranges with respect to  $V_{\rm a}$ . For low  $R_{\rm s,ext}$ , the dotted portion of the NDR curve is unstable, and for high  $R_{\rm s,ext}$ , the entire NDR curve is stable.

Translating this to a specific measurement context, suppose a room temperature cell is characterized by applying a square voltage waveform (Heaviside function) to its electrodes. The corresponding measurement trajectory begins at the intersection of the load line with the isothermal device  $(I_d, V_d)$ curve evaluated at  $T_0 = 300$  K, and moves along the load line toward the first intersection with the NDR curve, where it eventually settles (see Fig. 1.14). Different speeds along this path are possible, which can be understood with reference to the NDR curve and the external load characteristic. For  $(I_d, V_d)$ values lying nearby the stationary points, particularly near the "knee" of NDR onset, the rate of change of the temperature is low because a large fraction of the input power is dissipated to the external environment. Therefore, if the load line travels nearby the thermal equilibrium points of the NDR curve, the result will be a long delay as the applied power does not lead to rapid temperature increase of the cell. On the other hand, a larger series resistance combined with a larger applied voltage allows the switching trajectory to avoid these near-equilibrium values, and reach the same final state in a shorter time and potentially with lower total input energy [45].

There is a temptation to associate a time constant with heating processes, as the familiar scenario of heating a lumped-capacitance object with a constant power source admits exponential solutions for the temperature vs. time. However, this is very untrue in the case where the rate of heating is coupled to the temperature through the thermally activated conduction mechanism. According to the model, all heating rates are proportional to the cell heat capacity, but orders of magnitude different switching timescales can be induced in the same

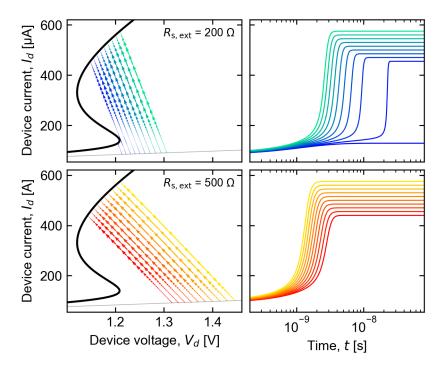

**Figure 1.14:** Time-dependent  $(I_{\rm d},V_{\rm d})$  trajectories following ideal voltage pulses with different amplitudes (color), with the cell initially at ambient temperature  $(T=T_0)$ . Using two slightly different series resistances  $(R_{\rm s,ext}=200~\Omega$  above, and  $R_{\rm s,ext}=500~\Omega$  below), the trajectories eventually reach the same final points of the NDR curve, but at different speeds. The farther the load line lies from the NDR curve, the faster the heating process. Delay-before-transition behavior is caused by load lines that first pass nearby, and then away from the NDR curve.

cell even in a narrow range of applied voltage. The thermistor temperature vs. time is not exponential in general and can show a long initial delay before eventual transition to the final high temperature state. These delays are caused by inefficient heating due to a switching trajectory passing nearby a condition of thermal equilibrium, where the cell is forced to spend long periods of time at elevated temperature while losing energy to its surroundings. Therefore, the delay is not an inescapable fact of the device heating process, but is due to a constraint imposed by the external driving circuit.

Measurements using a continuously swept voltage source are also common and important to consider. Again assuming negligible  $C_p$ , using high enough  $R_{\rm s,ext}$  means that every point of intersection of the (time dependent) load line and NDR curve is a stable fixed point and therefore the NDR curve can be entirely measured using a slow enough sweep. The condition for a complete, stable characterization of the NDR curve is that the external resistance is equal to or larger than the maximum amount of NDR along the curve,

$$R_{\rm s,ext} \ge \max\left(-\frac{dV_{\rm d}}{dI_{\rm d}}\right),$$

(1.9)

or equivalently that NDR does not appear when plotted on the  $(I_d, V_a)$ -plane.

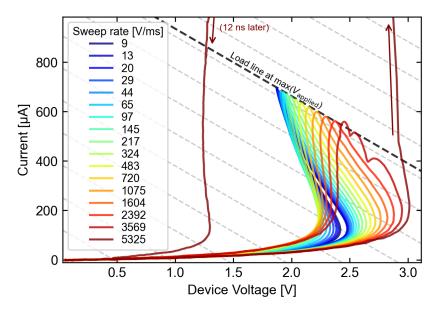

Using lower series resistance than the condition of Eq. 1.9 leads to a different type of behavior in a sweeping measurement (see Fig. 1.15). At two separate points during the sweep, where the NDR slope crosses the value of  $-R_{\rm s,ext}$ , there are abrupt changes in the stability of the system (bistable  $\rightarrow$  monostable). As  $V_{\rm a}$  is swept, a previously stable fixed point is annihilated (along with an unstable one) as the load line suddenly ceases to intercept the NDR curve at those points. If the annihilated fixed point was the previous operating point, the system transitions along the load line, forced into regions of relatively high heating/cooling rates. In dynamical systems theory, this well-known behavior is called a saddle-node bifurcation [135]. Following the bifurcation, the system may settle at a new and potentially distant operating point; but if there are no remaining fixed points, runaway heating can lead to a cascade of increasingly destructive effects, eventually causing an irreversible breakdown of the cell [90, 120].

In a measurement, a saddle-node bifurcation effectively means that at a certain threshold level of  $V_{\rm a}$ , a rapid and sometimes dramatic jump in  $I_{\rm d}$  and/or  $V_{\rm d}$  (with  $dV_{\rm d}/dI_{\rm d}=-R_{\rm s,ext}$ ) will be recorded as the stability landscape of the system suddenly changes with the biasing level. The common name given to measurements of these reversible jumps during slow voltage sweeps is threshold switching (TS). This term is usually used in context of memory selector devices, which are needed to avoid sneak paths in resistive crossbar arrays [136–139].

Although thermistors are not internally bistable devices, bistability appears as a property of certain circuit configurations. Nevertheless, the terminology "threshold switch" is commonly applied to such devices, even though the device alone is not truly a switch [40, 140–142]. A typical mental abstraction is that the TS device has two distinct resistance states; starting in its high resistance state (HRS), it transitions at a certain speed into its low resistance state (LRS) after it sees its "threshold" voltage, and when the voltage is reduced below its "hold" voltage it transitions back to its original HRS. However, in light of the present discussion, we recognize that this is not a complete picture for a thermistor-type switch. In fact, the device temperature continuously increases along its NDR curve, which can potentially be divided into stable and unstable regions depending on the load presented by the external measurement/driving circuit. The "HRS" and "LRS" here are not static device states but are two stable segments of the continuous NDR curve, and the so-called threshold and hold  $(I_d, V_d)$  points occur due to saddle-node bifurcations during sweeping. In each case, the locations of these thresholds can be predicted from the shape of the device NDR curve and the load characteristic, but neither switching speeds nor the threshold current densities and electric fields can be directly interpreted as a property of the device materials alone [143].

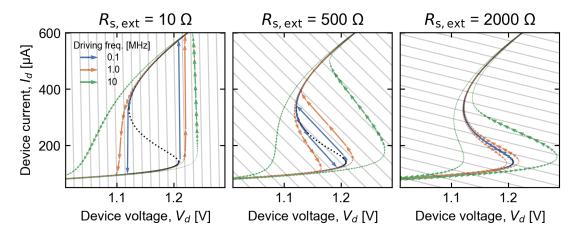

**Figure 1.15:** Simulated  $(I_{\rm d},V_{\rm d})$  trajectories for a thermistor driven by a sine waveform  $V_{\rm a}(t)$  with different frequencies and using three different external series resistances  $R_{\rm s,ext}$ . For low  $R_{\rm s,ext}$  and low driving frequency, the system suddenly transitions along the respective load lines at the saddle-node bifurcation points. For high  $R_{\rm s,ext}$ , the entire NDR curve can be traced out at low frequency. Higher frequencies push the cell further out of equilibrium due to thermal inertia, which widens a rate-dependent hysteresis in the trajectories. Load line slopes (gray) are plotted in the background for reference.

## 1.4.3 Oscillations and excitability

Finally, consider the case where  $C_p > 0$  pF and is large enough to significantly affect the dynamics of the system. The load line constraint of Eq. 1.8 in this case is replaced by a differential equation that describes the charging of the capacitive  $V_d$  node,

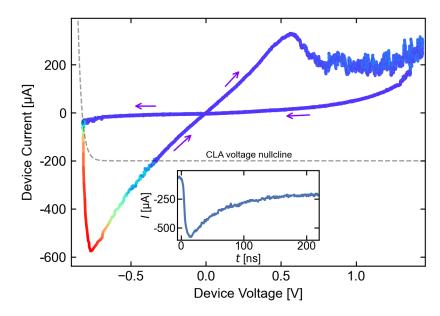

$$C_{\rm p} \frac{dV_{\rm d}}{dt} = \frac{V_{\rm a} - V_{\rm d}}{R_{\rm s,ext}} - I_{\rm d}. \tag{1.10}$$

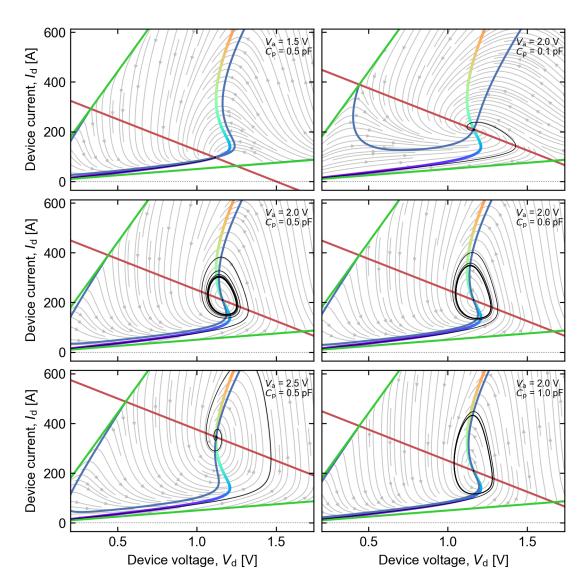

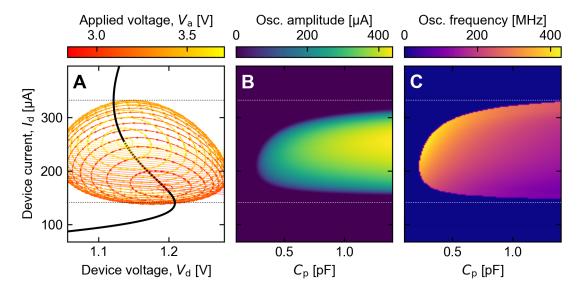

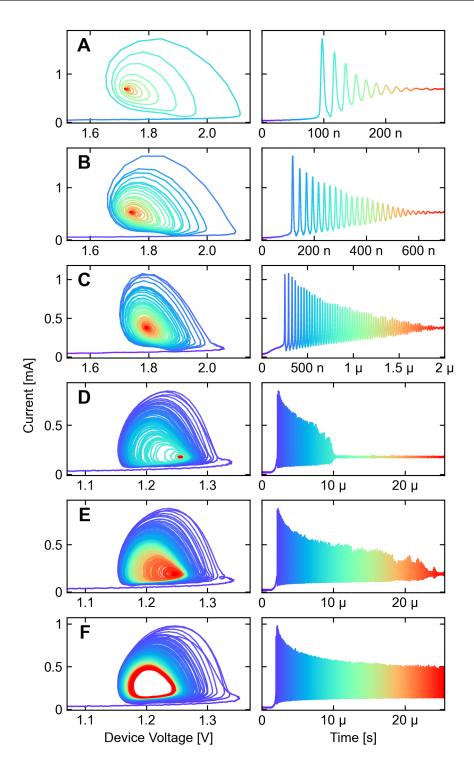

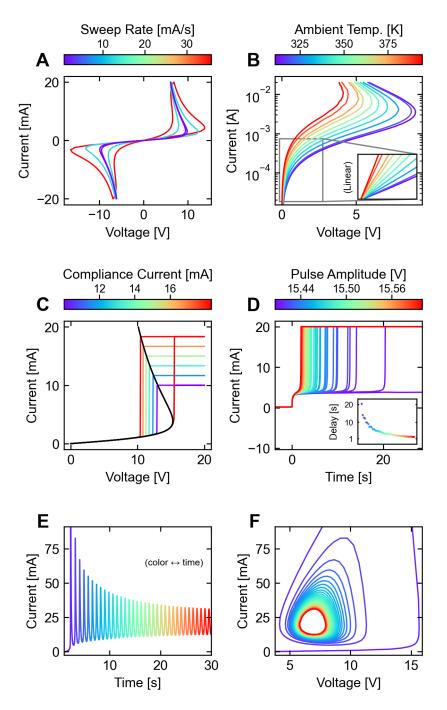

With the introduction of this equation, we now have a second-order (or planar) dynamical system, and we can consider the  $(I_{\rm d},V_{\rm d})$ -plane as a proxy phase space, because  $(I_{\rm d},V_{\rm d})$  identifies both the charge on the capacitor and the cell temperature state. The load line is still relevant as it becomes the condition where  $dV_{\rm d}/dt=0$  V/s, which can also be called the  $V_{\rm d}$ -nullcline. Therefore, the fixed points of the system  $(dI_{\rm d}/dt=0$  A/s and  $dV_{\rm d}/dt=0$  V/s) are not modified by the presence of  $C_{\rm p}$ . However, the increased dimensionality introduces further possibilities for stability/instability of these fixed points [135, 144]. In particular, excitable and oscillatory modes exist depending on the particular biasing conditions and the value of  $C_{\rm p}$ , as shown in Fig. 1.16. Operating in the oscillatory mode, the circuit is classified as a Pearson-Anson relaxation oscillator [145].

The oscillation behavior in this system can be understood as the alternating movement of energy between the reservoirs of cell temperature and the capacitor charge. After the bias  $V_a$  is initially turned on, the parallel capacitance

starts charging through the external series resistance. Eventually the device current and voltage are large enough to cross a spiking threshold and initiate thermal runaway in the thermistor material. As the device resistance rapidly drops, the capacitor discharges and delivers additional energy to the cell, raising its temperature well above the fixed-point level. Following the discharge, the elevated temperature cannot be maintained because of the current limiting feedback of the series resistance. By the time the temperature reduces back to the fixed-point level, the capacitor has lost too much charge to sustain it, so the device continues to cool down before the cycle repeats and approaches a limit cycle.

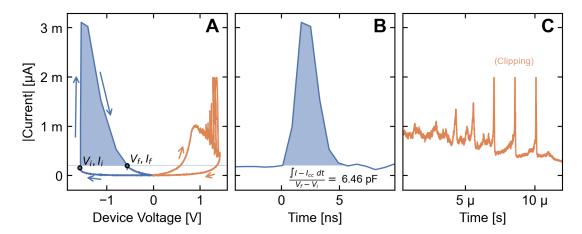

Sustained oscillation can only occur when the system is biased inside of  $(I_{\rm d},V_{\rm d})$  range with NDR [146, 147]. Another necessary condition for oscillation is that the electrical capacitance must be large enough relative to the thermal capacitance, in order for its discharge to elevate the device temperature to a level high enough above the steady-state temperature set by the series resistance and applied voltage. The exact biasing range where oscillations arise depends on the value of  $C_{\rm p}$ , as shown in Fig. 1.17. There are at least two important timescales involved in the oscillations that affect the frequency. The relaxation time or refractory period is determined by electrical RC charging  $(R = R_{\rm d}||R_{\rm s}, C = C_{\rm p})$ , and the duration of the falling edge of the spike is limited by the thermal discharge time  $R_{\rm th}C_{\rm th}$  of the device.

In computational neuroscience, simple dynamical models are used to mimic the evolution of the neuron membrane potential, with the Hodgkin-Huxley model being the most famous example [148, 149]. Excitability in these systems is associated with quiescent points lying near bifurcations, with different types of bifurcations giving rise to various types of spiking and bursting patterns thought to be connected to the computational properties of neurons [150–152]. Simple circuits including a thermistor-like component, such as the one considered here, can be shown to be topologically equivalent to simplified planar neuron models such as the FitzHugh-Nagumo model [153, 154], and are thus capable of generating same set of spiking bursting patterns when biased in specific ways. This correspondence is responsible for the interest in using thermal feedback circuits as artifical neurons in NC.

Figure 1.16: Phase portraits for a thermistor in a circuit with parallel capacitanc and external series resistance  $R_{\rm s,ext}=4~{\rm k}\Omega$ , under six different biasing conditions. Left and right columns show the effect of increasing  $V_{\rm a}$  and  $C_{\rm p}$ , respectively. The red and blue lines are the  $V_{\rm d}$ - and  $I_{\rm d}$ -nullclines, respectively, and the multicolored (according to T) line is the NDR curve, or  $T_{\rm nullcline}$ . Lime-green lines bound the phase space (due to the internal resistances), and the black curve shows the trajectory with initial condition  $T=300~{\rm K}$  and  $V_{\rm d}=0~{\rm V}$ . For a range of conditions, the trajectories are oscillatory.

**Figure 1.17:** Simulated oscillatory limit cycles in dependence of the biasing level  $V_a$  and the parallel capacitance  $C_p$ , with  $R_{\rm s,ext}=10~{\rm k}\Omega$ . (A) NDR curve with limit cycles occuring in a subrange of operating points when  $C_p=0.35~{\rm pF}$ . Peak-to-peak current amplitude (B) and frequency (C) vary with  $C_p$  and the fixed-point current. Crossing the discernable boundary between non-oscillation and oscillation is called a Hopf-bifurcation.

#### 1.4.4 Field effects

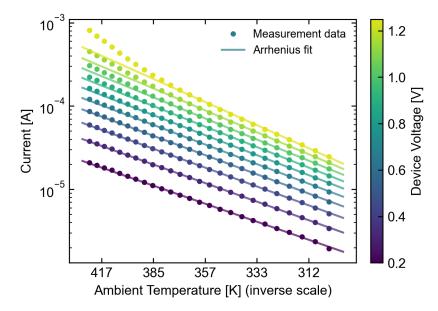

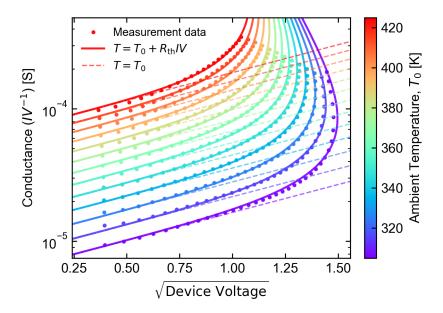

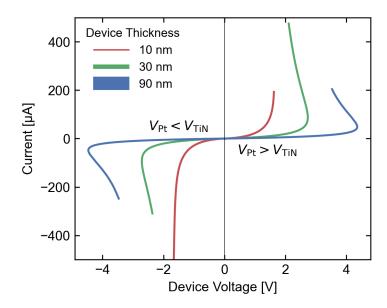

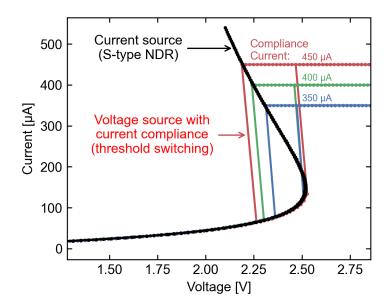

This section has explained a range of volatile switching phenomena in devices with temperature dependent conductivity while assuming linear voltage dependence of the current. The exponential temperature term in the conduction mechanism is all that is necessary to see these effects, which can also be observed in commercial temperature sensing devices (see Appendix B). In this case, the device is called a thermistor and any observed ( $I_d$ ,  $V_d$ ) non-linearity must be caused by device heating. However, most if not all scaled cells show a non-linear voltage dependence due to various other impacts of the high electric fields produced across the short insulating gaps.