# Test Suite Generation and Augmentation for Reconfigurable Industrial Control Software in the Internet of Production

Marco Lutz geb. Grochowski

Department of Computer Science

**Technical Report**

The publications of the Department of Computer Science of RWTH Aachen *University* are in general accessible through the World Wide Web. http://aib.informatik.rwth-aachen.de/

# Test Suite Generation and Augmentation for Reconfigurable Industrial Control Software in the Internet of Production

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

Marco Lutz geb. Grochowski, M. Sc. RWTH aus Hilden

Berichter: Universitätsprofessor Dr.-Ing. Stefan Kowalewski Universitätsprofessor Dr. Paula Herber

Tag der mündlichen Prüfung: 10. September 2024

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

Marco Lutz geb. Grochowski Lehrstuhl Informatik 11 grochowski@embedded.rwth-aachen.de

Aachener Informatik Bericht AIB-2024-09

Herausgeber: Fachgruppe Informatik

RWTH Aachen University

Ahornstr. 55 52074 Aachen GERMANY

ISSN 0935-3232

#### **Abstract**

With the advent of Industry 4.0 and the digitally networked factory, cyber-physical production systems (CPPSs) are reconfigured frequently along their life cycle to adapt to changing customer requirements or market demands. Such reconfigurations are not limited to the hardware but also affect the software of the programmable logic controllers (PLCs) driving these plants. While verification and testing are two techniques capable of alleviating the risk of introducing errors in production code, it is no longer sufficient to rely only on the results obtained by these methods during the commissioning of the CPPS. Even minor incremental reconfigurations to the PLC's software during the operational phase of the life cycle may introduce regressions that can be quickly overlooked by a developer and therefore need to be reverified.

The goal of this thesis is to provide a "push button" analysis for generating test cases after a static reconfiguration. The generated test cases can be injected and monitored during maintenance or virtual commissioning to observe the impact of reconfiguration on the CPPS by the developer.

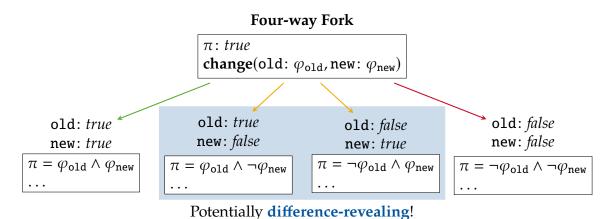

In order to reduce redundancy in test suite generation (TSG) after a structural reconfiguration to the PLC software, symbolic summaries of specific parts of the program should be cached and reused to benefit subsequent analysis. While automatic TSG is an established technique used to generate test suites adhering to structural coverage metrics of PLC software, the generated test suite might not anymore be adequate enough with regards to the coverage metric to ensure the absence of regressions. An indispensable part of regression testing (RT) is test suite augmentation (TSA), which guides the TSG toward the reconfigured behavior and increases the chances of deriving difference-revealing test cases which expose behavioral differences between the program and its reconfigured version. The derivation of new test cases is required to uncover potential regressions after a reconfiguration.

To this end, the contributions of this thesis include

- heuristics for the scalability of the existing TSG for PLC software,

- the reuse of symbolic summaries during TSG of reconfigured PLC software,

- and the concept of executing the old and new version of a reconfigured PLC software in one unified program version during TSA.

These contributions are evaluated on selected domain-specific benchmarks of varying difficulty from the PLCopen Safety suite and the Pick and Place Unit (PPU).

### Zusammenfassung

Mit dem Aufkommen von Industrie 4.0 und der digital vernetzten Fabrik werden cyber-physische Produktionssysteme (CPPS) während ihres Lebenszyklus häufig neu konfiguriert, um sich an veränderte Kunden- oder Marktbedürfnisse anzupassen. Solche Rekonfigurationen sind nicht nur auf die Hardware beschränkt, sondern betreffen auch die Software der speicherprogrammierbaren Steuerungen (SPSen), die diese Anlagen steuern. Während die Verifizierung und das Testen zwei Techniken sind, die das Risiko von Fehlern des in der Produktion eingesetzten Quellcodes vermindern, reicht es heutzutage nicht mehr aus, sich nur auf die aus der Inbetriebnahme resultierenden Ergebnisse zu verlassen. Selbst kleine inkrementelle Rekonfigurationen an der SPS-Software während der Betriebsphase entlang des Lebenszykluses können Regressionen einführen, die von einem Entwickler schnell übersehen werden können und daher erneut sichergestellt werden müssen.

Das Ziel dieser Arbeit ist es, eine "Push-Button"-Analyse für die Generierung von Testfällen nach einer Rekonfiguration zu entwerfen. Die generierten Testfälle können während der Wartung oder der virtuellen Inbetriebnahme eingespeist und überwacht werden, um die Auswirkungen der Rekonfiguration auf das CPPS durch den Entwickler zu beobachten. Um die Redundanz bei der Generierung von Testsuiten (TSG) nach solchen Rekonfigurationen zu verringern, sollen symbolische Zusammenfassungen von bestimmten Teilen des Programms zwischengespeichert und wiederverwendet werden. Die Testsuite-Erweiterung (TSA) stellt einen unverzichtbaren Teil des Regressionstestens (RT) dar, da die Abwesenheit von Regressionen nach einer Rekonfiguration nicht ausschließlich durch die alte Testsuite gewährleistet werden kann. Die TSA lenkt die TSG in Richtung des rekonfigurierten Verhaltens und erhöht so die Chancen Testfälle abzuleiten, die die Verhaltensunterschiede zwischen beiden Programmversionen aufdecken. Zu diesem Zweck beinhaltet der Beitrag dieser Arbeit

- ▶ Heuristiken für die Skalierbarkeit der bestehenden TSG für SPS-Software,

- die Wiederverwendung von symbolischen Zusammenfassungen während der TSG von rekonfigurierter SPS-Software,

- und das Konzept der Ausführung der alten und der neuen Version einer rekonfigurierten SPS-Software in einer Programmversion für die TSA.

Diese Ansätze werden anhand ausgewählter domänenspezifischer Benchmarks mit unterschiedlichem Schwierigkeitsgrad aus der PLCopen Safety Suite und der Pick and Place Unit (PPU) bewertet.

## **Contents**

| 1 | Intro        | ductio   | n                                                           | 1 |

|---|--------------|----------|-------------------------------------------------------------|---|

|   | 1.1          | Intern   | et of Production                                            | 1 |

|   |              | 1.1.1    | Vision, Objective, and Impact                               | 2 |

|   |              | 1.1.2    |                                                             | 3 |

|   | 1.2          | Transf   | formable Production Systems                                 | 3 |

|   |              | 1.2.1    |                                                             | 4 |

|   |              | 1.2.2    |                                                             | 6 |

|   | 1.3          | Softw    | are Maintenance Process                                     | 0 |

|   |              | 1.3.1    | Regression Testing                                          | 1 |

|   |              | 1.3.2    | Implications of Reconfigurations on the Trace Semantics 1   | 5 |

|   | 1.4          | Contr    | ibution                                                     | 7 |

|   |              | 1.4.1    | Publications                                                | 7 |

|   |              | 1.4.2    | Limitations and Assumptions                                 | 9 |

|   |              | 1.4.3    | Outline                                                     | 0 |

|   |              |          |                                                             |   |

| 2 | Prel         |          | es                                                          | 3 |

|   | 2.1          | Progra   | ammable Logic Controllers                                   | 3 |

|   |              | 2.1.1    | Program Organization Units                                  | 4 |

|   |              | 2.1.2    | Programming Languages                                       | 5 |

|   | 2.2          | Intern   | nediate Representation                                      | 7 |

|   | 2.3          |          | olic Program Analysis                                       | 9 |

|   | 2.4          | Desig    | n Principles of Symbolic Execution                          | 3 |

|   |              | 2.4.1    |                                                             | 4 |

|   |              | 2.4.2    | Avoiding the Encoding of Infeasible Execution Paths 3       | 4 |

|   |              | 2.4.3    | Merging of Execution Paths                                  | 4 |

|   |              | 2.4.4    | Dealing with Compositionality                               | 7 |

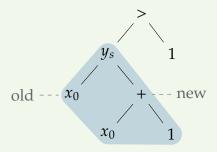

|   | 2.5          | Unify    | ing Program Versions via Change Annotations                 | 8 |

|   | 2.6          |          | al Reasoning with the SMT Solver Z3 4                       | 0 |

| 3 | Lite         | rature F | Review                                                      | 3 |

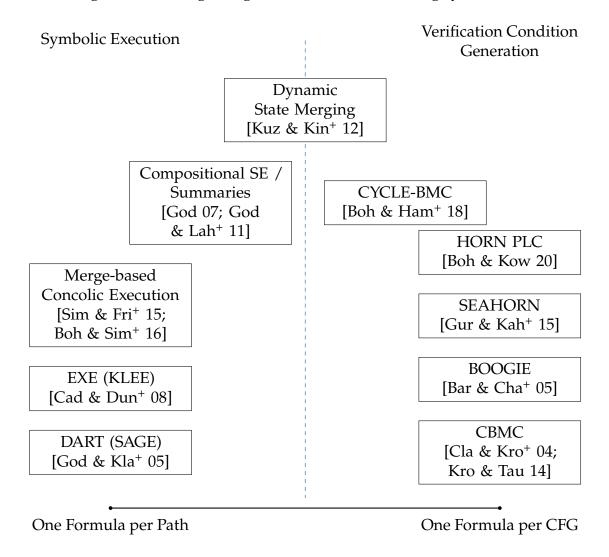

|   | 3.1          |          | uite Generation via Symbolic Execution 4                    |   |

|   |              | 3.1.1    | Compositionality and State Merging 4                        |   |

|   |              | 3.1.2    | Incremental Solving, Search Heuristics, and Memoization . 4 |   |

|   | 3.2          |          | uite Augmentation via Regression Analysis                   |   |

|   | - · <b>-</b> | 3.2.1    | Program Differencing using Summarization                    |   |

|   |              | 3.2.2    | Aiding Regression Analysis with Change Impact Analysis . 4  |   |

|   |              | 3.2.3    | Exposing Divergent Behaviors after a Reconfiguration 5      |   |

#### **Contents**

|      | 3.3     | Relate    | d Work                                                | 53         |

|------|---------|-----------|-------------------------------------------------------|------------|

|      |         | 3.3.1     | Verification of Programmable Logic Control Software 5 | 54         |

|      |         | 3.3.2     | Testing of Programmable Logic Control Software 5      | 57         |

| 4    | Test    | Suite 0   | Generation                                            | 59         |

|      | 4.1     | Comp      | ositional and Bounded Symbolic Execution 6            | <b>6</b> 0 |

|      |         | 4.1.1     |                                                       | 63         |

|      |         | 4.1.2     |                                                       | 54         |

|      |         | 4.1.3     | Assignments, Branches, and Calls 6                    | 57         |

|      |         | 4.1.4     | Detection of Unreachable Branches                     | <b>7</b> C |

|      |         | 4.1.5     | Static Single Assignment and Variable Versioning      | 72         |

|      | 4.2     | Gener     |                                                       | 73         |

|      | 4.3     | Applio    | cation of Summaries                                   | 76         |

|      | 4.4     |           |                                                       | 31         |

|      |         | 4.4.1     |                                                       | 33         |

|      |         | 4.4.2     | Predicate-Sensitive Change Impact Analysis            | 34         |

|      |         | 4.4.3     |                                                       | 36         |

| 5    | Test    | Suite A   | Augmentation                                          | 39         |

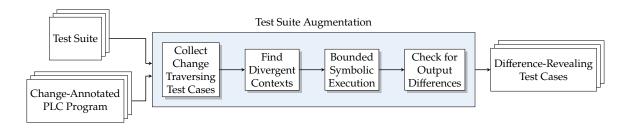

|      | 5.1     |           |                                                       | 92         |

|      | 5.2     |           |                                                       | 93         |

|      |         | 5.2.1     | Developer-centered Test Suite Augmentation Process 9  | 93         |

|      |         | 5.2.2     | 1                                                     | 96         |

|      |         | 5.2.3     |                                                       | 98         |

|      |         | 5.2.4     | Propagating Divergent Execution Contexts              | )7         |

|      |         | 5.2.5     | Checking for Output Differences                       | )8         |

| 6    | Eval    | uation    |                                                       | )9         |

|      | 6.1     | Bench     | marks                                                 |            |

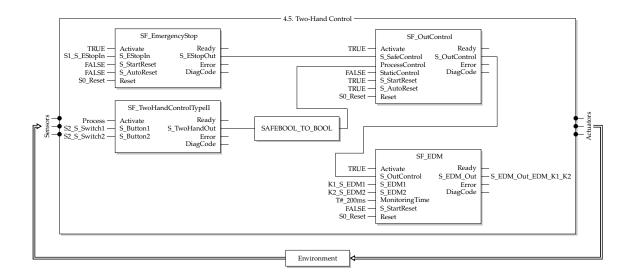

|      |         | 6.1.1     | PLCopen Safety Suite                                  | )9         |

|      |         | 6.1.2     | 1 ,                                                   |            |

|      | 6.2     | Test Sı   | uite Generation                                       | 12         |

|      | 6.3     |           | uite Augmentation                                     |            |

| 7    | Con     | clusion   |                                                       | 23         |

|      | 7.1     |           | ok                                                    |            |

| Α    | Ope     | rationa   | I Semantics                                           | 27         |

|      | •       |           |                                                       |            |

|      |         | •         |                                                       |            |

| Lis  | st of T | ables .   |                                                       | 35         |

| 1 :- | 4 of F  | )ofinitie | nno 12                                                | ٠.         |

|                  | Contents |  |

|------------------|----------|--|

| List of Examples | 141      |  |

| List of Acronyms | 143      |  |

| Ribliography     | 147      |  |

Introduction

Since the advent of the Industrial Internet of Things (IIoT), conventional manufacturing has experienced a paradigm shift toward cyber manufacturing. This shift is driven by the growing demands for individual products and emerging information and communications technologies (ICT) [Jes & Bre<sup>+</sup> 17], resulting in the fourth industrial revolution known as Industry 4.0 [Bun 16].

As conventional production systems' life cycles and value chains are too rigid regarding the increasingly demanded agility in industrial automation [Gro & Sim<sup>+</sup> 20], the trend goes toward networking and distributed computing [Bor & Tre<sup>+</sup> 21]. While these technologies are well understood, the currently applied concepts must be adapted to meet future production requirements.

Several challenges for formal and semi-formal methods arise with serviceoriented architectures (SOAs) as enablers and implementation means for multiagent systems (MASs). The increasing modularization and distributed control structures result in heterogeneity regarding ad-hoc networking and a high degree of reconfigurability, leading to emergent behavior and potential regressions after the production system is put into operation.

Therefore, the quality assurance of logic control software during the life cycle of a cyber-physical production system (CPPS) requires adaptations in the testing and verification processes known from traditional software engineering. With the use of Digital Shadows (DSs) and the insights gained from production, reconfigurations made to the logic control software need to be adequately tested and verified to ensure safe changes to the production process. The central challenge lies in the aggregation, abstraction, and analysis of heterogeneous data [Bra & Dal<sup>+</sup> 22], which the Internet of Production (IoP) tries to master.

#### 1.1 Internet of Production

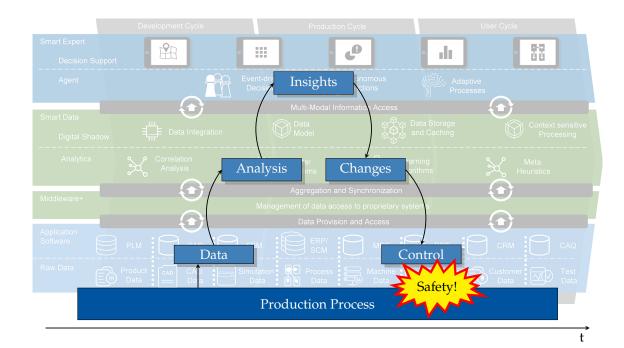

The IoP builds on the ideas of the IIoT and advocates the vision of enabling real cross-domain and inter-company collaboration by providing semantically adequate and context-aware data from production [Pen & Gle<sup>+</sup> 19]. Figure 1.1 shows the architecture and infrastructure of the IoP in the background and a high level abstraction in the foreground. During the life cycle of the production process, data emitted by CPPSs are collected and analyzed. The insights gained from the emitted data are turned into data that controls the process and forms the basis for changes, which create new services and flexible value chains [Gro & Kow<sup>+</sup> 19]. Changes translated into reconfigurations of the underlying logic control

Figure 1.1: The architecture and infrastructure of the IoP [Bre & Klo<sup>+</sup> 17]. Figure adapted from Bild 1 in [San & Xi<sup>+</sup> 21].

software of the CPPS can result in safety-critical modifications requiring additional safeguarding.

#### 1.1.1 Vision, Objective, and Impact

The vision, objective, and impact of the IoP concerning the functional perspective for the realization of the emphasized process depicted in Figure 1.1 are listed next.

#### Vision:

- ▶ Integration of machine learning and AI-based models from engineering

- Creation of IoP-specific "data to knowledge pipelines" that transform massive data into insights

- Providing meaningful, actionable knowledge to decision-makers

#### **Objective:**

- Visualizations, decision support, and human-centered interfaces

- ▶ Enable cross-learning and transfer

- Data-to-knowledge pipelines

#### Impact:

- Methods for data-driven insights and back-coupling to transform insights into actions – usable by human or machine

- ▶ Smart Decision Support for the human-in-the-loop

- Toolbox for Digital Shadows, Data-To-Knowledge Pipelines, validated, selfadaptive production systems

The key challenges for the IoP lie in building algorithms that combine machine learning with model-based analysis and control and develop human-centered interfaces to facilitate decision support.

#### 1.1.2 Digital Shadow

A key component in realizing the vision, objective, and impact of the IoP is the digital shadow (DS).

#### Definition 1.1: Digital Shadow [Bib & Dal<sup>+</sup> 20; Bec & Bib<sup>+</sup> 21]

A digital shadow (DS) is a set of temporal data traces and/or their aggregation and abstraction collected concerning a system for a specific purpose, i.e., context-based with respect to the original system.

The DS comprises task-specific data of production processes allowing the reconstruction of the entire life cycle of an industrial asset and serves as the primary technique for data aggregation and refinement within the IoP [Bre & Buc<sup>+</sup> 19]. The DS, therefore, abstracts from the underlying production process and serves as a virtual representation of the current state of the logic control software.

This gives rise to the use of event-driven architectures in which messages are exchanged as soon as a state change occurs [Bre & Buc<sup>+</sup> 19] and is further discussed in Section 1.2.1. The use of the DS for the contribution of this thesis lies in the aggregation of data during the whole analysis life cycle of test suite generation (TSG) and test suite augmentation (TSA) of a reconfigured programmable logic controller (PLC) program. In particular, the specific purpose mentioned in Definition 1.1 refers to the artifacts resulting from the process of TSG and TSA, and hence the generated test cases and function block (FB) summaries form the DSs of testing. This disruptive concept of the IoP results in transformable production systems.

#### 1.2 Transformable Production Systems

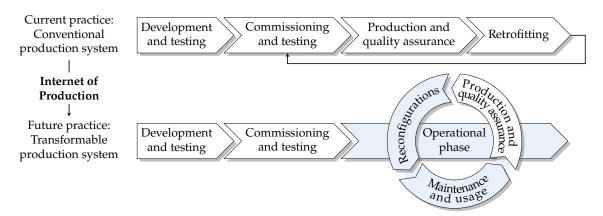

Transformability is one of the primary enablers of coping with changing intrinsic and extrinsic demands. It is a required property to guarantee competitiveness among companies and comprises the flexibility and mechanical reconfigurability of a CPPS [Jes & Bre<sup>+</sup> 17]. Flexibility describes the property of a CPPS to adapt quickly and with little effort, within the limits of a given range, to changed conditions and, together with reconfigurability, enables the CPPS to adapt to changes that were unknown during planning [Rei & Kre<sup>+</sup> 08; Wie & Rei<sup>+</sup> 14]. Figure 1.2 shows the

Figure 1.2: Juxtaposition of the production system's life cycle and value chain. *Figure adapted from Fig. 2 in* [Zel & Wey 15].

juxtaposition of conventional and transformable production systems' life cycle and value chain. This shift from conventional to transformable production systems comes with a series of challenges that the IoP tries to master.

In general, the overall complexity of the CPPS increases [Wie & Rei<sup>+</sup> 14] as the IoP blurs the distinction between the development and operational phases of the production system.

While transformability is a crucial enabler for quickly adapting to changing market requirements, it also increases the complexity due to the reconfigurability and emergent behavior [Wie & Rei<sup>+</sup> 14; Ste & Hei 17]. This leads to shorter product cycles and an increase in the number of software variants. This highly iterative development and agile manufacturing process in which the requirements are subject to continuous changes take their toll on the safety of the CPPS. To manage the increasing complexity, efficient and lightweight techniques that bridge the gap between verification and testing are required.

The following section explains the heterogeneous environments and the distributed control of a CPPS.

#### 1.2.1 Service-oriented Architecture

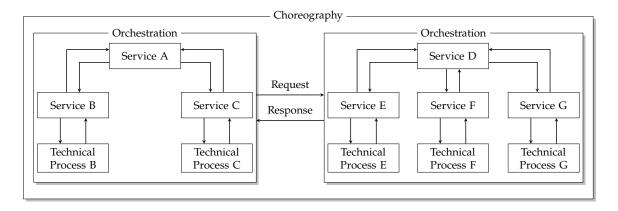

A SOA, in combination with the concept of the DS, suits the demanding requirements of reconfigurable CPPS [Bre & Buc<sup>+</sup> 19]. Figure 1.3 shows the composition of services to processes and the distinction between *orchestration* and *choreography* [Pel 03; Rie 12]. A centralized service coordinates an orchestration, e.g., "Service A" or "Service D" in Figure 1.3, which implements the business logic or the production process workflow. This centralized service describes all necessary information

for the aggregation of multiple services, their interfaces, their dependencies with regard to the flow of control, and their exchanged messages [Rie 12].

In contrast, the *choreography* does not follow some centralized coordination but instead consists of the interplay between autonomous services in which their cooperation may fulfill cross-organizational processes. It specifies the communication protocol and works on the *observable behavior* of the participating processes, commonly specified as behavioral interfaces [Rie 12]. The depicted SOA in Figure 1.3

Figure 1.3: Orchestration and choreography in a SOA. *Figure adapted from Figure 1 in* [Pel 03].

is therefore subdivided by the orchestration and choreography into two views on the system, a *local* and a *global view*, respectively [Rie 12]. The application of formal methods on the global view can thus only assure the interoperability between the processes in this choreography. As opposed to this, the application of formal methods on the local view allows for verification of the behavior of the services due to the centralized and coordinating service and the knowledge about the actual business logic [Rie 12].

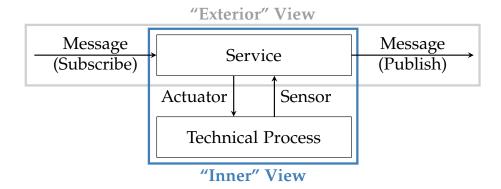

This thesis focuses on the safeguarding of the local view. To further delimit the contribution, Figure 1.4 refines the local view by further splitting it up into an *exterior* and an *inner view* [Zel & Wey 18]. The "exterior" view communicates to other components via its interface and abstracts from the technical process, whereas the "inner" view focuses on communication with the underlying technical process and is responsible for driving the technical process to behave in the desired manner. Typically, reactive systems are used to control the technical process.

In the IoP, the reactive nature of the logic control software is lifted to an event-based system with the help of the DS and exposed as a service [Gro & Kow<sup>+</sup> 19]. As both components, i.e., services, and their assemblies, i.e., composed services, can be subject to changes in an agile environment, the following section talks about reconfigurations that can occur.

Figure 1.4: Generalized views on a service with exemplary communication technologies and its interaction with a technical process.

Figure adapted from Fig. 1. a) in [Zel & Wey 18].

#### 1.2.2 Reconfigurations of Production Systems

Reconfigurations allow the CPPS to be able to change quickly and cost-effectively in terms of their capacities, their functional contents, and the technologies they make available to meet the demands of today's markets [Ste & Hei 17]. It enables quick scale-up and change management using modular structures with matching interfaces [Ste & Hei 17] and pushes the boundaries of the CPPS's flexibility corridors. In order to unify the terminology of *evolution* [Bec & Mun<sup>+</sup> 19], *changes*, and *adaptations* [Vog & Rös<sup>+</sup> 16] found in literature, the definition of *reconfiguration* is used synonymously throughout this thesis.

#### **Definition 1.2: Reconfiguration [Mat 10]**

"A reconfiguration represents the technical view of the process of modifying an already developed and operationally deployed system to adapt it to new requirements, extend functionality, eliminate errors, or improve quality characteristics."

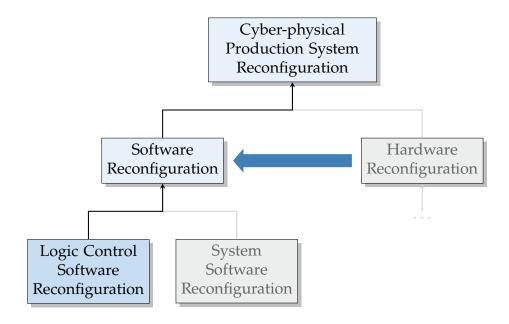

Due to this increasing agility in the development process, the shorter life cycles, and the changing customer and legislator requirements, the software maintenance process must account for reassurance of the CPPS's behavior after a reconfiguration [Gro & Sim<sup>+</sup> 20]. A reconfiguration can affect hardware as well as software, and a classification for the types of reconfiguration in accordance with the definition of [Mat 10] is illustrated in Figure 1.5.

In this thesis, reconfigurations affecting the logic control software are analyzed. These reconfigurations are often initiated by changes to the hardware components of the CPPS and form the basis for software evolution. Reconfigurations of a CPPS can either be structural (architecture-based), functional (service-related), or non-functional (quality-related) [Mat 10] and affect either the "exterior" or "inner" view. In the subsequent sections, these types of reconfigurations are explained

Figure 1.5: Application areas for reconfigurations of CPPS. *Figure adapted from Abbildung 5.1 in* [Mat 10].

with the help of the two perspectives illustrated in Figure 1.4.

#### **Reconfigurations of the Exterior View**

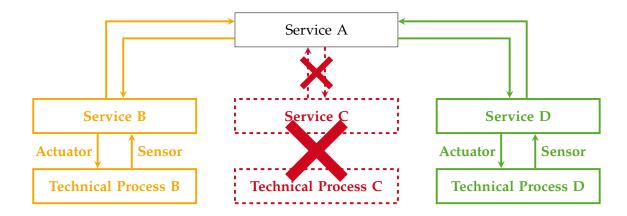

Structural reconfigurations of the exterior view are, for instance, changes in the services' interfaces or changes in the dependencies between the services or the architecture. These reconfigurations do not impact the behavior of the inner view, as the control logic is encapsulated within a service. Figure 1.6 summarizes the effect of modifications, deletions, and additions on the level of services. Modifications to the service interface do not impact the implementation that controls the technical process.

However, the converse is not true. Typically, behavioral reconfigurations of the "exterior" view are achieved by either changing the interfaces of the "exterior" view or changing the behavior, i.e., the implementation of the "inner" view. The deletion of an existing service, such as Service C, or the addition of a new service, such as Service D, depicted in Figure 1.6, only affects the business logic of Service A and its interoperability but does not affect any non-directly connected services.

In general, structural reconfigurations of the "exterior" view do not impact the behavior of the "inner" view, and verification boils down to proving interoperability using behavioral information. More interesting are reconfigurations impacting the exterior view that stem from reconfigurations of the inner view and are discussed in the following.

Figure 1.6: Reconfiguration of a SOA after modifications to an existing service, deletion of a service and/or connections, and addition of a new construction to the production system, which requires an implementation of an additional service or addition of connections.

#### **Reconfigurations of the Inner View**

Typically, with regard to logic control software, reconfigurations originate from reconfigurations occurring to the technical process, as depicted in Figure 1.5. Reconfigurations to the technical process can be categorized as the addition, modification, and removal of new or existing hardware components [Vog & Fol<sup>+</sup> 14].

- 1. Addition of a new hardware component:

- ▶ Implementation of a new function block

- Adaptation of an existing function block with regard to its interface and implementation

- 2. Modification of the behavior of the context (hardware/mechanical):

- Modification of the internal structure of the function block

- Optimization of the behavior of the function block

- 3. Removal of a hardware component:

- ▶ Reduction of the interface and internal structure of the function block

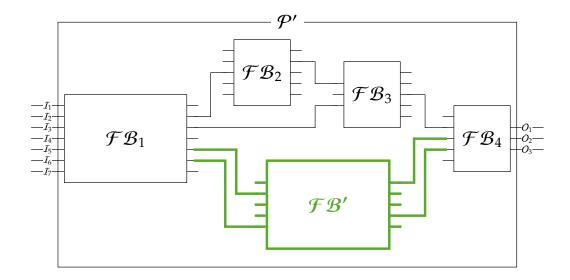

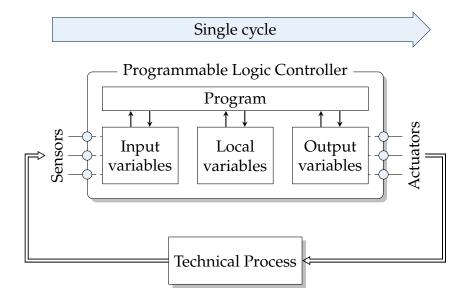

These hardware reconfigurations often induce reconfigurations in the software and are illustrated in Figures 1.7 to 1.9. For example, when a new hardware component, such as a sensor or actuator, is added, the functionality must be likewise represented in software.

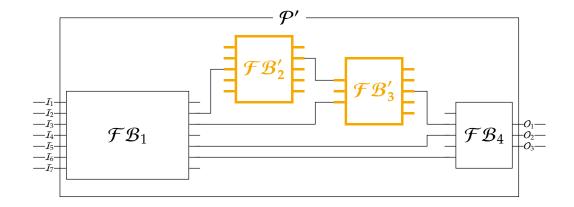

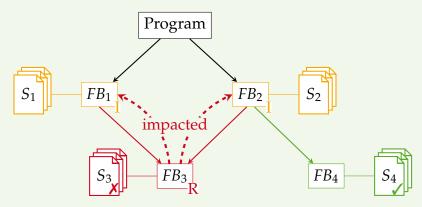

Therefore, a new FB may be implemented to account for the new functionality, as depicted in Figure 1.7, or the adaptation of an existing FB with regard to its interfaces and implementation. A modification of the behavior of the technical

Figure 1.7: Reconfiguration of a program after adding a new construction to the CPPS, which requires an implementation of an additional FB  $\mathcal{FB}'$ .

Figure adapted from Abbildung 4 (1) in [Vog & Fol<sup>+</sup> 14].

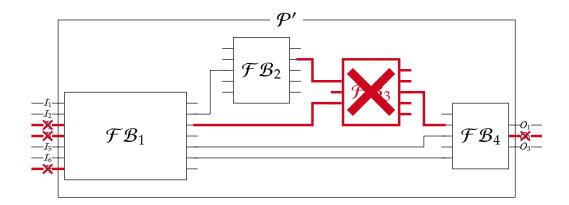

Figure 1.8: Reconfiguration of a program by modifying the behavior of the context (mechanical) to the production system, which requires the adaptation of the internal structure of the program. The interface may stay the same, e.g., when the order of two processing steps is changed.

Figure adapted from Abbildung 4 (3) in [Vog & Fol+ 14].

Figure 1.9: Removal of a hardware component can lead to the removal of FBs and modifications to the interface.

Figure adapted from Abbildung 4 (5) in [Vog & Fol+ 14].

process may lead to a change in the structure of the underlying software. Figure 1.8 reflects the reconfiguration of the technical process in software. Last, removing a hardware component can reduce the interface and the internal structure of the FB, as depicted in Figure 1.9.

Depending on the intended hardware changes, complex software reconfigurations can arise. However, they can be reduced to a combination of small incremental reconfigurations, as illustrated by the types of reconfigurations in Figures 1.7 to 1.9. In the next section, the impact of such planned and unplanned reconfigurations is categorized and integrated into the software maintenance process.

#### 1.3 Software Maintenance Process

The quality assurance of logic control software during the life cycle of a CPPS requires adaptations in the testing and verification processes known from traditional software engineering. With the use of the DS and the insights gained from production, reconfigurations made to the control software need to be adequately tested and verified to ensure safe modifications to the production process. In the context of software maintenance, the data of the DS does not only encompass the data passed in communication between services but also artifacts resulting from the maintenance process. CPPSs are reconfigured frequently during their life cycle, and hence it must be ensured that a revision does not introduce any regressions while achieving the intended effect [Bec & Mun<sup>+</sup> 19].

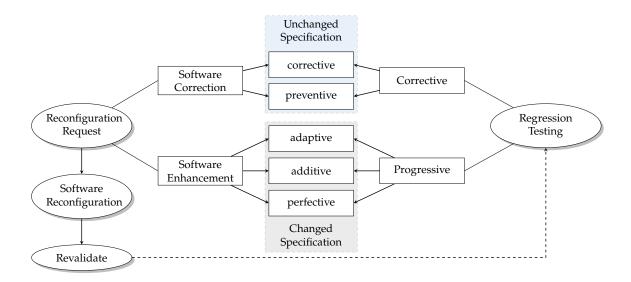

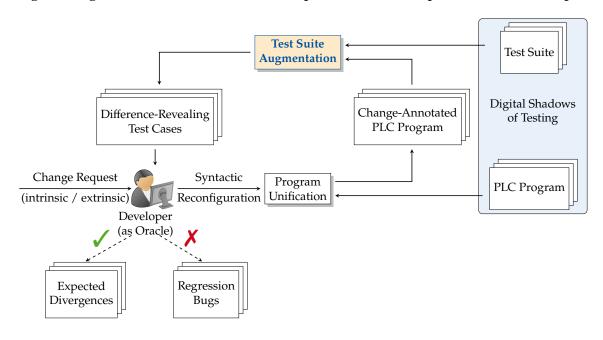

Figure 1.10 gives an overview of the software maintenance process. A reconfiguration request starts the software maintenance process. Reasons for reconfigurations consist of minimizing efforts, defects, or cost. It is not relevant whether the reconfiguration request is intrinsic or extrinsic, i.e., either triggered internally by the developing company or induced externally by another company or the market.

Figure 1.10: Overview of the software maintenance process and integration of regression testing as a method for revalidation.

Figure adapted from Fig. 19 in [Gal & Lyl 91].

More important is the distinction between the type of reconfiguration request, either software correction or software enhancement. Depending on the type of reconfiguration, the specification is either changed or unchanged. Changes to the specification are classified as adaptive, additive, or perfective reconfigurations [ISO 22].

The class of software corrections can either be corrective, i.e., a bug was fixed, or preventive, i.e., to correct faults in the software before they occur in the system [ISO 22]. After the reconfiguration request has been stated, the action follows. The software is reconfigured, and the effect of the reconfiguration needs to be revalidated to confirm no unintended changes have occurred. An in general undecidable but very sought-after question (cf. [Pod & Cla 90]) during software maintenance is how a change in the semantics of a program statement affects the execution behavior of other statements in the program.

The goal is to find reasonable approximate solutions for the following two problems: (1) determining the set of affected components and (2) determining the set of tests that exercise these components. A technique that tries to answer this question is regression testing, which can either be corrective or progressive and is further discussed in the next section.

#### 1.3.1 Regression Testing

The naive approach, after a reconfiguration, uses an existing test suite and reruns it on the reconfigured PLC program. While this works in theory, it tends to yield two practical problems:

- 1. If the test suite is too large, executing all test cases might not be feasible. Therefore, some form of prioritization or minimization has to be performed [Yoo & Har 12].

- 2. The existing test suite might not test the changed behavior and therefore requires TSA [Xu & Kim<sup>+</sup> 15]

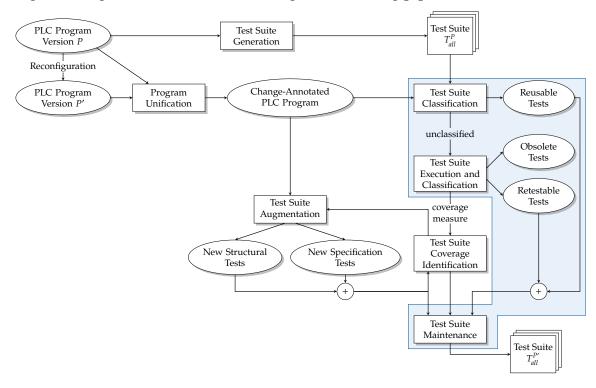

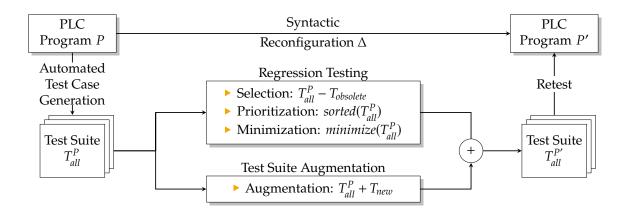

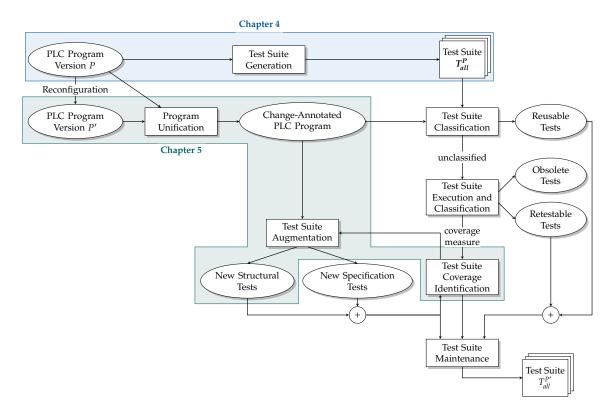

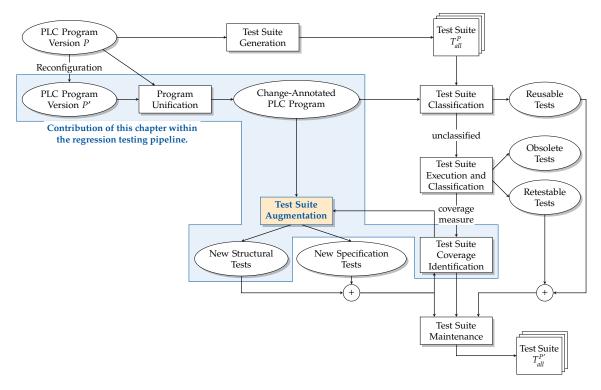

Regression testing typically consists of four major problems: (1) test suite classification, (2) test suite execution, (3) test suite coverage identification, and (4) test suite maintenance [Leu & Whi 89; Rot & Har 96]. The problem of test suite classification deals with the selection of test cases  $T' \subseteq T$  such that specific criteria such as required time to test are minimized, and other criteria like coverage are maximized. Figure 1.11 gives an overview of the regression testing pipeline and the software

Figure 1.11: Overview of the regression testing pipeline and maintenance. *Figure adapted from Figure 3 in* [Leu & Whi 89].

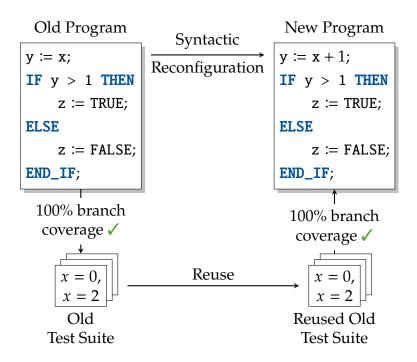

maintenance process and is referenced throughout this section. Figure 1.12 illustrates the three main techniques: test (1) *selection*, (2) *prioritization*, and (3) *minimization* [Yoo & Har 12].

Test case selection aims to remove all test cases that are not part of the retest set. The resulting set of test cases can still be "too big" to test because it would, for example, require more time than available after a reconfiguration. Test case prioritization can use the execution history and is a widely utilized technique for regression testing [Eng & Run<sup>+</sup> 10] to prioritize new-structural and new-specification

Figure 1.12: Application of regression testing techniques and test suite augmentation after a syntactic reconfiguration.

test cases. Last, test suite minimization tries to reduce the number of test cases required to cover as many faults as possible and corresponds to the minimal set cover problem, which is NP-complete [Yoo & Har 12] and, therefore, rarely used. There are, however, some heuristics but most regression testing pipelines rely on selection techniques that are modification-aware [Rot & Har 96]. A complementary technique to regression testing poses TSA [Xu & Kim<sup>+</sup> 15].

The technique presented in Chapter 4 can be categorized as some form of regression algorithm, as already done work tries to be lifted to the reconfigured program version. The test suite execution problem tries to establish the correctness of the reconfigured program version P' with respect to the T'. The test suite coverage identification problem is the subject of Chapter 5. The goal is to identify whether the previous test suite T is still sufficient to cover the reconfigured program version P' and, if necessary, create a set of new functional or structural tests. Last but not least, the test suite maintenance problem deals with creating a new test suite and test history for the reconfigured program P' by consolidating the results from the prior steps [Leu & Whi 89].

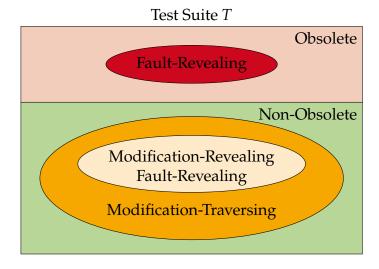

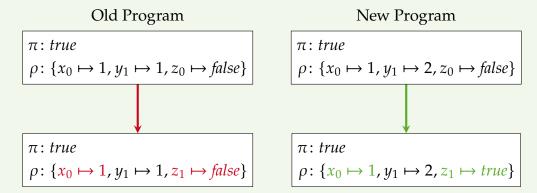

Test cases can be classified into the following three categories: (1) *reusable*, (2) *retestable*, and (3) *obsolete* test cases [Leu & Whi 89]. Reusable test cases are not modification-traversing as they execute the parts of the program that remain unchanged between the two versions. They should produce the same result in both program versions and need not be rerun. During test suite classification, reusable tests can be derived statically by analyzing the control-flow graphs (CFGs) of the change-annotated program (CAP), as depicted in Figure 1.11. Retestable test cases, however, are modification-traversing and must be rerun as they execute the parts of the program that have been changed. This class of test cases is especially interesting, as they may be difference-revealing. A test case is said to be difference-revealing if executed on both program versions, the base version *P* and the reconfigured program *P'*, produce different outputs. Both the reusable and retestable test cases belong to the class of non-obsolete test cases, as depicted

Figure 1.13: Relationship between test classes. *Figure adapted from Fig. 1 in* [Rot & Har 96].

in Figure 1.13. Last, the class of obsolete test cases includes test cases that can no longer be used because they were either specified over a different input/output relation or do not contribute to the structural coverage [Leu & Whi 89].

As shown in Figure 1.11, the test suite must be executed to determine whether a test case is retestable or obsolete. For the sake of completeness, the test classes, their relation to the software maintenance process from Figure 1.10, and their target construct are illustrated in Table 1.1. The generation of new-structural and

| Table 1.1: Classification of  | of test cases.  |

|-------------------------------|-----------------|

| Table adapted from Table 2 in | [Leu & Whi 89]. |

| <b>Test Class</b>                   | Specification                | <b>Target Construct</b>     | Test Type                   |

|-------------------------------------|------------------------------|-----------------------------|-----------------------------|

| Reusable                            | Unchanged                    | Unchanged                   | Structural, Specification   |

| Retestable                          | Unchanged                    | Changed                     | Structural, Specification   |

| Obsolete                            | Unchanged<br>Changed         | Changed Unchanged / Changed | Structural Specification    |

| New-Structural<br>New-Specification | Unchanged/Changed<br>Changed | New<br>New                  | Structural<br>Specification |

new-specification test cases are part of TSA and hence not discussed here. The test suite coverage identification depicted in Figure 1.11 is discussed and explained in Chapter 5. Last but not least, after the classification of the old test suite and the generation of new test cases, the process of test suite maintenance (TSM) is performed.

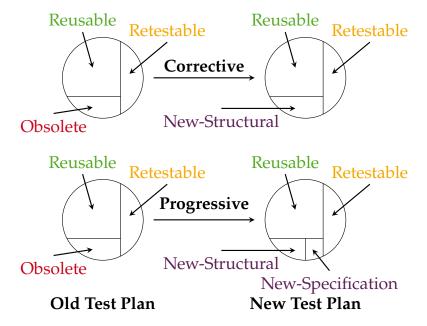

Figure 1.14 gives an overview of how the newly derived test plan relates to the old test plan under consideration for corrective and progressive changes, as

Figure 1.14: Evolution of the test plan during TSM. *Figure adapted from Figure 1 in* [Leu & Whi 89].

illustrated in Figure 1.10. In both cases, the TSM amounts to updating the test suite with the newly generated test cases while removing obsolete ones yielding a test suite suitable for testing the reconfigured program version.

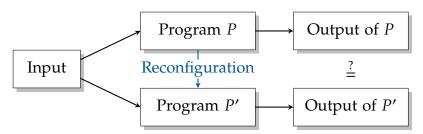

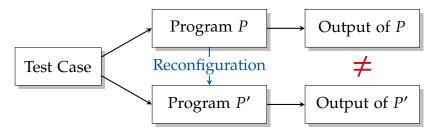

#### 1.3.2 Implications of Reconfigurations on the Trace Semantics

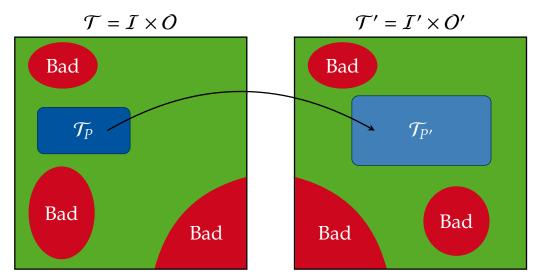

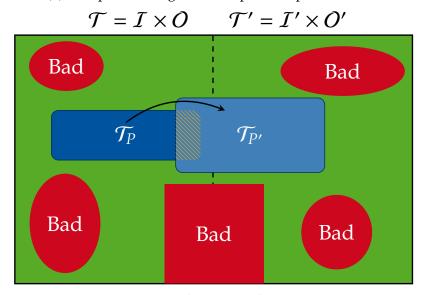

The implications of reconfigurations on the trace semantics are illustrated in Figure 1.15. They either lead to a change of the input/output relation or no change of the input/output relation. The behavior of the base version P and of the reconfigured program P' are expressed by their trace semantics, where  $\mathcal{T}$  represents the set of all traces of possible combinations of inputs and outputs, and  $\mathcal{T}_P$  the possible traces of P [Cha & Ulb<sup>+</sup> 19]. The green area depicts the set of all possible traces that do not violate requirements, whereas the red areas depict traces that exhibit bad behavior in some form or another.

Figure 1.15a shows a complete change of the input/output relation denoted by the non-overlapping domains. Both a complete and a partial change of the input/output relation require new test cases, as all prior generated test cases are obsolete. In these scenarios, techniques other than TSA are required to establish transferrable knowledge. For example, regression verification can establish an equivalence relation between the two versions even though their interfaces have changed [Cha & Ulb<sup>+</sup> 19]. However, this change must be captured explicitly by specifying the semantic difference in a logical formula as input for the regression

(a) Complete Change of the Input/Output-Relation.

(b) Partial Change of the Input/Output Relation.

(c) No Change of the Input/Output Relation.

Figure 1.15: Implications of reconfigurations on the trace semantics of PLC programs.

Figure adapted from Fig. 4 in [Cha & Ulb+ 19].

verification algorithm.

The contributions of this thesis consider no changes in the input/output relation of the reconfigured PLC program and hence deal with the class of implications depicted in Figure 1.15c. This is a typical scenario where code is refactored, the technical process is reconfigured without affecting the controller's interface, or additional behavior is implemented [Cha & Ulb<sup>+</sup> 19].

#### 1.4 Contribution

The contribution of this thesis is aligned in the following with regard to the vision, objective, and impact of the IoP, as presented in Section 1.1.1. The overarching goal is to ensure safety for rapidly changing CPPS in the IoP in an efficient way. The central research question concerns how traditional software verification and testing methods can apply to emerging technologies in the context of the IoP while fulfilling standard industrial requirements.

The *vision* is to build a data-to-knowledge pipeline to provide meaningful, actionable knowledge, where the data represents the source code of a PLC program and the actionable knowledge of whether a PLC program is safe or unsafe after a reconfiguration.

The *objective* is to provide decision support, i.e., to provide insights into the quality of the development process by evaluating the adequacy of a test suite for structural coverage of a reconfigured PLC program.

The *impact* are the formal methods that provide data-driven insights into the impact of the reconfiguration on the PLC software and a toolbox for DS of testing in the form of a program analysis framework (PAF) as a "push-button" analysis to generate test cases and augment test suites after a reconfiguration.

#### 1.4.1 Publications

The main contributions found in Chapter 4 and Chapter 5 have been published in prior work. This section presents the publications relevant to this thesis and the corresponding contributions.

#### **Relevant Publications**

[Gro & Sim<sup>+</sup> 20]

M. Grochowski, H. Simon, D. Bohlender, S. Kowalewski, A. Löcklin, T. Müller, N. Jazdi, A. Zeller, and M. Weyrich, "Formale Methoden für rekonfigurierbare cyber-physische Systeme in der Produktion", *Autom.*, vol. 68, no. 1, pp. 3–14, 2020. DOI: 10.1515/auto-2019-0115. [Online]. Available: https://doi.org/10.1515/auto-2019-0115.

[Gro & Völ<sup>+</sup> 22a]

M. Grochowski, M. Völker, and S. Kowalewski, "Automatic Test Suite Generation for PLC Software in the Internet of Production", in 2022 IEEE 27th International Conference on Emerging Technologies and Factory Automation (ETFA), 2022, pp. 1–8. DOI: 10.1109/ETFA52439.2022.9921726.

[Gro & Völ<sup>+</sup> 22b]

M. Grochowski, M. Völker, and S. Kowalewski, "Test Suite Augmentation for Reconfigurable PLC Software in the Internet of Production", in *Formal Methods for Industrial Critical Systems - 27th International Conference, FMICS 2022, Warsaw, Poland, September 14-15, 2022, Proceedings,* J. F. Groote and M. Huisman, Eds., ser. Lecture Notes in Computer Science, vol. 13487, Springer, 2022, pp. 137–154. doi: 10.1007/978-3-031-15008-1\\_10. [Online]. Available: https://doi.org/10.1007/978-3-031-15008-1%5C\_10.

#### **Further Publications**

[Gro & Kow<sup>+</sup> 19]

M. Grochowski, S. Kowalewski, M. Buchsbaum, and C. Brecher, "Applying Runtime Monitoring to the Industrial Internet of Things", in 24th IEEE International Conference on Emerging Technologies and Factory Automation, ETFA 2019, Zaragoza, Spain, September 10-13, 2019, IEEE, 2019, pp. 348–355. DOI: 10.1109/ETFA.2019.8869447. [Online]. Available: https://doi.org/10.1109/ETFA.2019.8869447.

#### **Bibliographic Notes and Contributions**

The core idea of the TSG algorithm presented in Chapter 4 is based on prior work by Dimitri Bohlender and Hendrik Simon [Sim & Fri<sup>+</sup> 15; Boh & Sim<sup>+</sup> 16]. While a framework for the analysis of PLC software already existed in the form of the tool Arcade.Plc [Bia & Bra<sup>+</sup> 12], the compilation and translation pipeline from Structured Text (ST) to the intermediate representation (IR) of Sebastian Biallas has been reimplemented by me. All other contributions of this thesis have been implemented in a standalone project by myself. The used benchmarks of the PLCopen Safety suite were implemented by Sebastian Biallas and Hendrik Simon, while I extended it by user-defined program examples.

For compliance with the doctoral regulations, I delimit my contributions from the contributions of my co-authors of the relevant publications. The overview paper [Gro & Sim<sup>+</sup> 20] was a joint collaboration with researchers from the University of Stuttgart. Dimitri Bohlender and I worked in close collaboration writing about the work of Hendrik Simon and added our own perspectives in the respective sections 2, 4, and 5.

The paper [Gro & Völ<sup>+</sup> 22a] formed the basis of Chapter 4 and benefited from the discussions with Marcus Völker and the valuable feedback provided by Stefan

Kowalewski. The core idea and the underlying implementation of the methodologies were researched and implemented by me.

Chapter 5 is based on [Gro & Völ<sup>+</sup> 22b], to which I contributed all original concepts and methodologies. After identifying the need for TSA after a reconfiguration, I supervised Johannes Neuhaus in developing a prototypical implementation in his Master's thesis. While his work gave a good first impression of how TSA could be applied, several improvements and additional features had to be implemented by me. The publication [Gro & Völ<sup>+</sup> 22b] thus represents my own work incorporating the discussions and feedback of Marcus Völker and Stefan Kowalewski.

#### 1.4.2 Limitations and Assumptions

This dissertation does not deal with the whole safety life cycle of a CPPS but instead places particular emphasis on analyzing the impact of reconfigurations. While formal verification methods are suitable for safeguarding safety-critical functions, they require a high modeling effort [Gro & Sim<sup>+</sup> 20]. This may inhibit the use of formal verification methods in practice, giving rise to more lightweight techniques such as regression testing and TSA. A necessary prerequisite for the algorithms presented in this thesis is the existence of a syntactically change-annotated PLC program given as input to the PAF. Furthermore, the techniques adhere to the limitations imposed by the underlying PLC's architecture and standard.

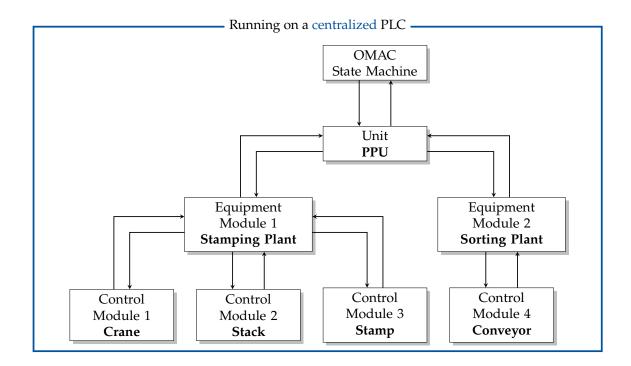

In particular, PLC programs are subject to cyclic execution resulting in non-termination. Still, every execution through one cycle terminates and hence can be analyzed. Moreover, the standard forbids the implementation of recursive calls [Gro & Völ+ 22b]. In its current state, the PAF does not support all available language features of the [Int 14]. For instance, using arrays or pointers is not yet supported but could be extended. Statically allocated memory, however, can be modeled by flattening the arrays. While the PAF is able to analyze loops other than the naturally occurring execution cycle of the PLC program [Gro & Völ+ 22b], no additional heuristics such as loop invariant generation have been implemented, hence may rendering the analysis of loops in specific examples as intractable. Some of the benchmarks use the timer capabilities of the [Int 14], which are modeled non-deterministically using an over-approximating representation of timers from [Adi & Dar+ 14].

Last but not least, control tasks are usually distributed in the context of Industry 4.0, yet most often still coordinated centrally [Bre & Buc<sup>+</sup> 19]. While multiple PLCs for each control task exist, they are coordinated centrally by one overarching controlling PLC. Despite that, the distributed control task is modeled as one compositional, classic PLC program, in which the other control tasks are incorporated as FBs and executed on a single PLC controller in the benchmarks [Gro & Völ<sup>+</sup> 22b]. This neglects the influences of different times and latencies introduced due to the communication between each controlling PLC [Gro & Völ<sup>+</sup> 22b]. It is assumed that the sequential modeling using a single PLC is a feasible abstraction of several

distributed PLCs running in parallel, realizing the same control task, because the business logic is implemented by a single, coordinating PLC, which processes the messages of the other distributed PLCs sequentially in all circumstances [Gro & Völ<sup>+</sup> 22b].

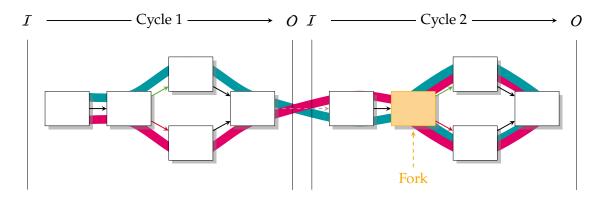

To this end, the contributions of this thesis include

- heuristics for the scalability of the existing TSG for PLC software,

- ▶ the reuse of symbolic summaries during TSG of reconfigured PLC software with the goal of reducing analysis time,

- and the concept of four-way forking for TSA of reconfigured PLC software

and are evaluated on selected domain-specific benchmarks of varying difficulty, such as the PLCopen Safety suite and the Pick and Place Unit (PPU).

#### 1.4.3 Outline

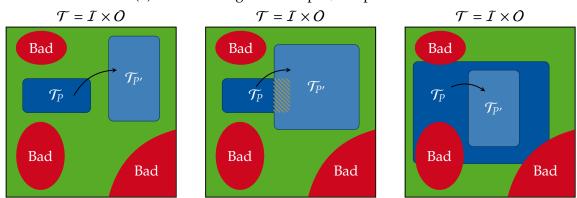

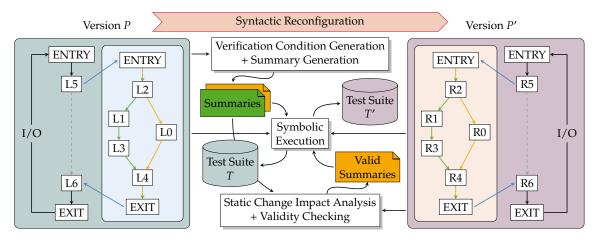

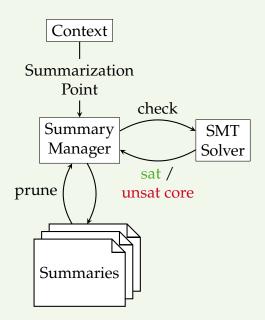

Figure 1.16 gives a graphical overview of the implementation contribution of this thesis and their interplay and aligns them with the subsequent chapters. The input

Figure 1.16: Overview of the implementation contribution of this thesis.

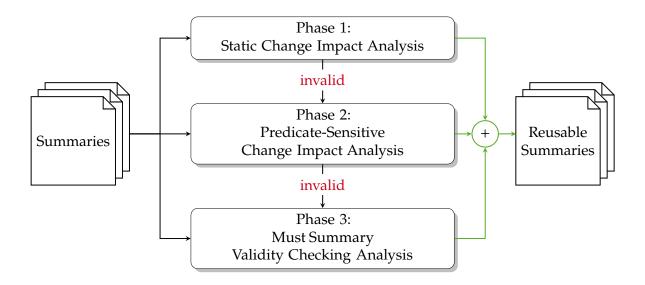

of the developed PAF is a change-annotated PLC program, which is parsed and compiled into a textual IR and represented as a CFG. Chapter 2 gives an introduction to PLCs and their peculiarities, presents the IR, gives a short digression to symbolic program analysis and their design space, discusses the unification of program versions in a CAP, and motivates how satisfiability modulo theories (SMT) formulas can be solved efficiently. The subsequent Chapter 3 gives insights into the field of TSG and TSA in regression analysis and discusses related work in

the field of PLC verification and testing. Chapter 4 deals with the background on TSG, the realization of summarization of FBs, and the applicability of summaries. It is represented by the blocks static analysis (SA), verification condition generation (VCG), symbolic execution (SE), and the summaries of Figure 1.16. Chapter 5 focuses on the TSA and extends the SE from Chapter 4. This chapter explains the underlying theory behind the test suite coverage identification depicted in Figure 1.16 and proposes shadow symbolic execution (SSE) as a solution to TSA. In Chapter 6, the two techniques proposed in this thesis are evaluated on benchmarks of varying sizes under different heuristics. Last, Chapter 7 concludes this thesis and gives suggestions for future work.

Preliminaries 2

This chapter gives an introduction to PLCs, their execution model, and an IR for ST. Following this, the design principles of SE and relevant concepts for the methods in Chapter 4 and Chapter 5 are presented.

# 2.1 Programmable Logic Controllers

PLCs are specially designed control hardware used in industrial automation [Tie & Joh 09] to control, operate, supervise, and monitor highly complex automation processes [Bia 16].

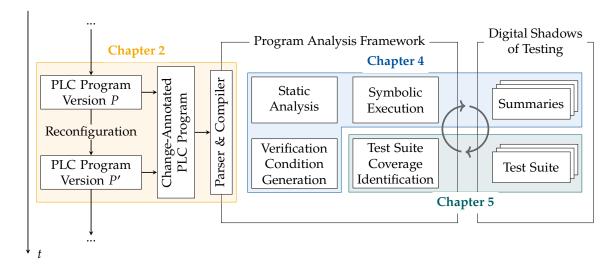

As PLCs are still ubiquitous in today's industrial control applications [Boh 21], they are subject to the IEC 61131 standard [Int 14]. The standard defines requirements toward both hardware and software aspects of the PLCs [Boh 21] for the prevention of personal injury caused by machines in the production process [Tie & Joh 09]. Figure 2.1 shows a schematic view of the execution model of the PLC and its interaction with its environment. PLCs adhere to a cyclic execution model.

Figure 2.1: Schematic view of a PLC interacting with its environment. *Figure adapted from Figure 2.1 in* [Boh 21].

At the beginning of an execution cycle, the inputs from the environment provided

by the sensors of the technical process are read and stored in the designated input variables of the PLC. For the duration of the execution cycle, the PLC will work on this copy of input variables and ignore any new values provided by the sensors until the beginning of the next cycle.

Next, the execution of the logic control program takes place. To update its execution state, the program may use local variables serving as internal memory, whose valuations persist across subsequent execution cycles. An execution cycle ends when the program terminates. Upon termination, the computed valuations of the output variables are used to update the outgoing connections to the actuators in order to invoke the desired behavior of the controlled plant. Between updates, the outputs retain their valuations throughout the subsequent cycles [Boh 21].

# 2.1.1 Program Organization Units

A PLC program can consist of several program organization units (POUs), which provide an interface definition of the input, local, and output variables and a body containing the actual instruction that operates on this interface [Tie & Joh 09]. The IEC 61131 standard [Int 14] distinguishes between three types of POUs, namely functions, function blocks, and programs.

**Function** Functions are parameterizable POUs without local variables or FB instances. They are, therefore, "stateless" and always provide the same result for the same input parameters. Since there is no internal state, it is impossible to instantiate functions [Bia 16] as part of a POU's interface declaration, and an invocation requires passing all parameters directly to the function.

**Function Block** FBs are parameterizable POUs with local variables and FB instances. Instances of FBs are created as local variables of POUs. FBs retain the valuations of their internal and external variables between invocations and are, thus, "stateful". The passing of arguments is optional when invoking FBs [Boh 21].

Unlike functions, an instance of an FB is part of the parent POUs' local variables, and initialization only takes place for the first call of an instance. As internal and external variable valuations are retained between invocations, calling an FB without assigning new arguments to its input parameters will use the currently assigned values.

Typically, timer FBs are configured this way by passing arguments for all parameters and only partially assigning values to input parameters in subsequent calls [Boh 21].

**Program** This POU type represents the main entry point in each cycle and adheres to the schematic view of Figure 2.1. In addition to the local variables of FBs, programs have hardware inputs and outputs [Bia 16]. All variables of the overall program to which physical addresses, i.e., inputs and outputs of the PLC, are

assigned must be memory-mapped in this POU or the respective configuration [Tie & Joh 09].

# 2.1.2 Programming Languages

As PLCs are widely used in industrial automation, the IEC 61131 standard defines five distinct programming languages for implementing the functionality of a POU to account for the various programming paradigms [Bia 16]: Instruction List (IL), Structured Text (ST), Ladder Diagram (LD), Function Block Diagram (FBD), and Sequential Function Chart (SFC) [Tie & Joh 09].

The choice of language depends on the tasks and areas of applications at hand and differs significantly [Tie & Joh 09]. Usually, lower-level and algorithmic functionality are implemented in textual languages, whereas the overall project structure is implemented in a graphical language [Boh 21].

As all of the IEC 61131 programming languages can be translated into each other [Boh 21], verification workflows make use of an IR [Dar & Maj<sup>+</sup> 16]. The high-level textual language ST is introduced and used throughout this thesis for illustration purposes [Tie & Joh 09].

#### **Structured Text**

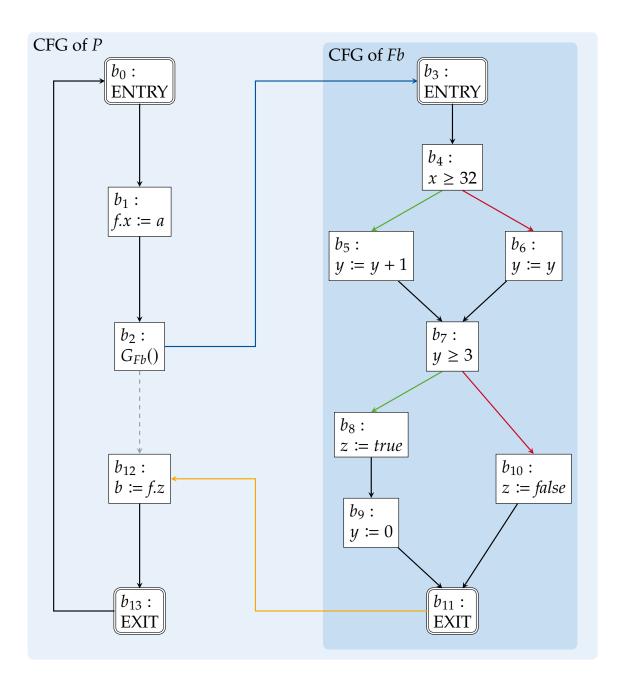

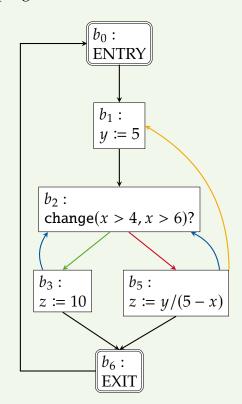

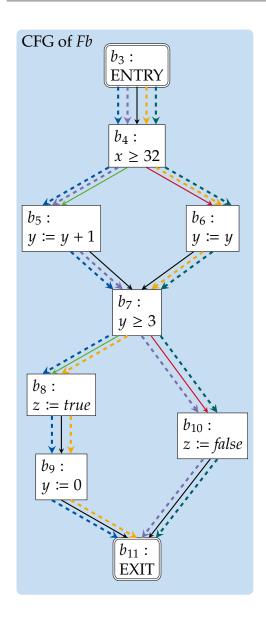

ST is a high-level textual language for imperative, procedural PLC programming [Boh 21] which resembles PASCAL [Tie & Joh 09]. A compositional example program consisting of two POUs, a program *P* and an FB *Fb*, is shown in Figure 2.2.

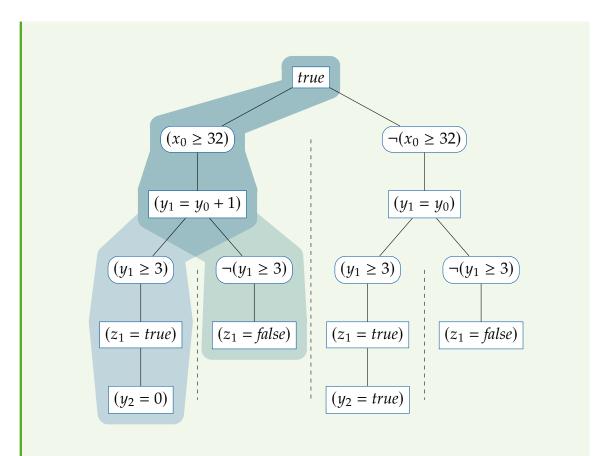

### Example 2.1: Explanation of Figure 2.2

The main program, P, instantiates an FB of type Fb and invokes it in the body. The input variable is passed as an argument via assigning x := a, and the output is written via z => b. The callee f computes its output z depending on the valuation of the input of x and the internal state of y. It uses y as an internal counter variable and returns z := TRUE if the valuation reaches the value f. The value of the local variable f of the callee f is initialized with f0. User-defined initialization is achieved by using the allocation operator such as f1.

### **Default Initialization of Variables**

At the start of the program, all variables are assigned initial values. These valuations depend on the specification by the developer made in the corresponding declaration parts of the POUs [Tie & Joh 09]. The IEC 61131 ensures that all elementary data types have predefined initial values [Int 14]. Elementary data types, for instance, are initialized with 0 for numeric values and *false* for Boolean values. This is also

```

1 FUNCTION_BLOCK Fb

2 VAR_INPUT

x : INT;

4 END_VAR

5 VAR

1 PROGRAM P

y : INT;

7 END_VAR

2 VAR_INPUT

a : INT;

8 VAR_OUTPUT

4 END_VAR

z : BOOL;

10 END_VAR;

5 VAR

11

IF x >= 32 THEN

f : Fb;

7 END_VAR

12

y := y + 1;

8 VAR_OUTPUT

13

ELSE

9

b : BOOL;

14

y := y;

10 END_VAR

15

END_IF;

f(x:=a,z=>b);

16

IF y >= 3 THEN

17

z := TRUE;

12 END_PROGRAM

18

y := 0;

19

ELSE

20

z := FALSE;

END_IF;

22 END_FUNCTION_BLOCK

```

Figure 2.2: A program POU and an FB POU.

termed 0-default initialization throughout this thesis. For example in Figure 2.2, the value of the local variable y of the callee f is initialized with 0. User-defined initialization is achieved by using the allocation operator such as y : INT := 1;.

# 2.2 Intermediate Representation

Each POU is compiled into a type-representative module representing the program semantics in a goto-based textual IR. The supported expressions by these semantics are due to [Nie & Nie 92; Nie & Nie 20] and presented in Definition 2.1.

### Definition 2.1: Expression [Nie & Nie 92; Nie & Nie 20]

An expression  $e \in E$  is either an arithmetic expression  $a \in E_A \subseteq E$  or a Boolean expression  $b \in E_B \subseteq E$ .

$$e := a \mid b$$

$$a := i \mid v_a \mid -a \mid a_1 op_a a_2$$

$$b := t \mid v_b \mid \neg b \mid a_1 op_r a_2 \mid b_1 op_b b_2$$

The meta-variable  $i \in \mathbb{I}$  represents integers and ranges over the implementation-specific integer data type  $\mathbb{I}$  of the programming language used for Z3 [dMou & Bjø 08], as it is used as implementation backend for expressions within this thesis. The meta-variable  $t \in \mathbb{B}$  represents the Boolean truth values true and false. The arithmetic and Boolean variables are denoted through the meta-variable  $v_a \in V_A \subseteq V$  or  $v_b \in V_B \subseteq V$ , respectively. The supported subset of operators with their corresponding semantics from ST [Int 14] are  $op_a \in \{**, *, /, MOD, +, -\}$  for arithmetic expressions and  $op_r \in \{<, >, \le, \ge, =, <>\}$  and  $op_b \in \{AND, XOR, OR\}$  for Boolean expressions [Tie & Joh 09]. Parentheses, "(" and ")", are resolved during compilation from ST to the IR via the precedence of operators.

The ST statements are compiled into instructions of the IR using the expressions defined in Definition 2.1.

#### **Definition 2.2: Instruction**

An instruction has one of the following forms:

```

I := \mathbf{goto} \ b_{\ell} \mid \mathbf{sequence}(I_1, I_2) \mid \mathbf{assign}(v, e) \mid \mathbf{ite}(b, \mathbf{goto} \ b_{\ell_1}, \mathbf{goto} \ b_{\ell_2}) \mid v_1, \dots, v_n := \mathbf{call} \ G(e_1, \dots, e_m) \ .

```

Throughout this thesis, the call instruction  $v_1, \ldots, v_n := \operatorname{call} G'(e_1, \ldots, e_m)$  is lowered to a sequence of pre- and post-assignments without the loss of general-

ity [Cla & Hen<sup>+</sup> 18]. During compilation calls are completed, i.e., additional preand post-assignments are introduced such that all variables are always initialized. It is determined which inputs and outputs are read and written and the respective assignments are augmented, enforcing the same order as in the underlying interface of the compiled, type-representative module. The cyclic execution semantic of a PLC program is not explicitly captured via an instruction. Instead, it is implicitly captured by Definition 2.3. Possible execution paths through this IR are of interest to analyze a program. Therefore, the IR representing the program structure can be formalized as a flow graph. Here, the instructions are labeled and assigned to vertices. In principle, assigning the instructions to the edges is equivalent, and the appropriate choice of formalization depends on the particular analysis [Ste 93]. The edges between the vertices represent the intra- and interprocedural flow of control.

### **Definition 2.3: Control-Flow Graph [All 70]**

A control-flow graph (CFG) is a tuple  $G = (V, V_{input}, (B, E), b_{\ell_e}, b_{\ell_x})$ , where

- V is an ordered finite set of variables,

- ▶  $V_{input} \subseteq V$  is an ordered finite set of input variables,

- ▶ (*B*, *E*) is a directed graph with

- vertices *B* representing labeled blocks  $b_{\ell}$  ∈ *B*,

- edges  $E \subseteq B \times B$  modeling the potential transfer of control from the end of the block to the beginning of the next block,

- ▶  $b_{\ell_e} \in B$  is a unique entry block,

- ▶  $b_{\ell_x} \in B$  is a unique exit block, and without loss of generality  $b_{\ell_e} \neq b_{\ell_x}$ .

The finite set of variables  $V = V_{input} \uplus V_{local} \uplus V_{output}$  results from the disjoint set union of the input, local, and output variables of all referenced type-representative CFGs that are connected to this CFG. Each labeled block  $b_{\ell} \in B$  can contain zero or more instructions. A single block encoding of the control flow is enforced for the SE in the subsequent Chapters 4 to 5, therefore disallowing sequence of instructions as commonly referred to as basic block encoding without the loss of generality. This implies that an instruction within a vertex  $b_{\ell}$  of G is uniquely identifiable by its label  $\ell$ .

### **Definition 2.4: Program**

A *program* is a pair  $\mathcal{P} = (G, \mathcal{G})$ , where

▶  $G \in \mathcal{G}$  is the CFG representing the program POU,

▶ *G* is a set of CFGs representing POUs referenced by the PLC's program POU.

We model the PLC program as a pair  $P = (G, \mathcal{G})$ , where  $G \in \mathcal{G}$  is the CFG of the program POU, and  $\mathcal{G}$  is a set of CFGs representing nested FBs occurring in the program.

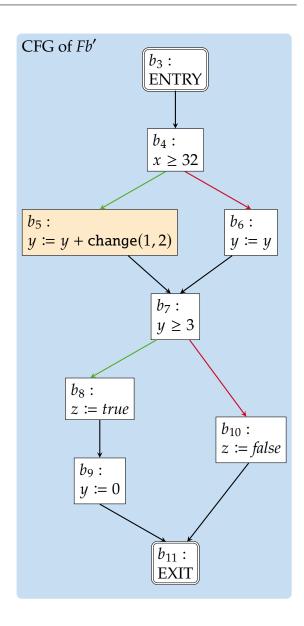

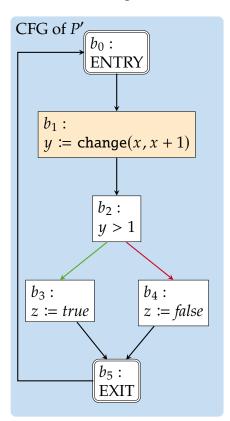

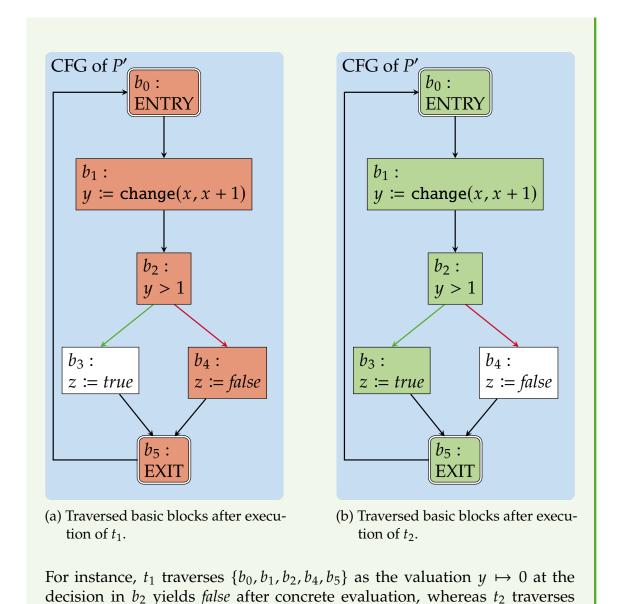

### **Example 2.2: Control-Flow Graph**

Figure 2.3 shows the compiled running example.  $\mathcal{P} = (P, \{P, Fb\})$ , where  $P = (\{a, b, f.x, f.y, f.z\}, \{a\}, (B, E), b_0, b_{13})$ . Do note that variables such as f.x do not represent qualified names anymore but are instead flattened as the internal memory of FBs are lowered during the compilation to regular procedures which operate on references to the blocks' variables [Boh 21]. Hence the qualified names [Aho & Set<sup>+</sup> 86] such as f.x, where f and x are identifiers, are lowered to a single identifier f.x and therefore represent a single flattened variable.

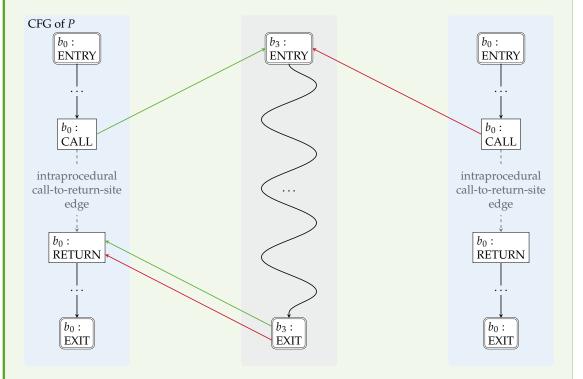

# Representation of Callees

Several ways of modeling callees exist, enabling different precisions for the analyses [Nie & Nie<sup>+</sup> 99]. A callee is a function that is called by another function, the caller. The algorithms of this thesis were designed with function cloning in mind. Cloning provides some form of context sensitivity through the use of scopes but avoids redundancy as introduced by function inlining.

A benefit of cloning is the avoidance of interprocedural invalid paths. Nevertheless, high nesting depths may lead to an exponential blow-up. A downside of function cloning is that it does not work on (mutually) recursive functions. However, the PLC standard [Int 14] restricts the programmer from implementing recursion. While avoiding interprocedural invalid paths under-approximates the program's behavior, the analysis is still compositional in a broader sense as, for instance, the summarization from Chapter 4 abstracts from the actual context.

# 2.3 Symbolic Program Analysis

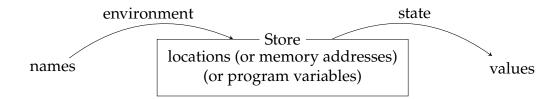

Next, some common concepts from the symbolic program analysis's perspective are explained to resolve ambiguity [Aho & Set<sup>+</sup> 86]. Figure 2.4 illustrates the relationship between these concepts. Variables refer to particular locations within the memory, called the *store*. A state is a mapping from locations in the store to values, i.e., a state maps "l-values" to their corresponding "r-values". An l-value always has a defined location within the memory and thus can be referenced. However, an r-value is an expression that is not an l-value. In the context of symbolic

Figure 2.3: Graphical representation of the compiled running example.

Figure 2.4: Relationship between the environment, store, and state [Aho & Set<sup>+</sup> 86].

*Figure adapted from Figure 1.8 in* [Aho & Set<sup>+</sup> 86].

program analysis [Bal & Cop<sup>+</sup> 18], the state refers to an execution state, whereas the store describes this mapping. Usually, the semantics use two mappings, one for the environment  $\epsilon \colon V \to \operatorname{Loc}$ , which maps names describing variables to locations  $\operatorname{Loc} := \mathbb{N}$ , and one for the state  $\iota \colon \operatorname{Loc} \to D$ , which maps locations to values of the respective domain  $d \in D$ , i.e., integers  $i \in \mathbb{I}$  and Boolean truth values  $t \in \mathbb{B}$  in this thesis, as depicted in Figure 2.4. This thesis abstracts from this concept of composition and directly maps names to their values which is common in symbolic program analysis [Nie & Nie<sup>+</sup> 99]. This facilitates the notation as compile-time names are equivalent to run-time locations, i.e., variables [Aho & Set<sup>+</sup> 86], and also coincides with how POUs are compiled in the IR of this thesis (see Example 2.2). The definitions of the concrete and symbolic store used in symbolic program analysis with regard to this thesis are given in Definition 2.5.

### **Definition 2.5: Concrete and Symbolic Store**

A concrete store  $\rho: V \to D$  is a mapping from variables  $v \in V$  to concrete values  $d \in D$ . A symbolic store  $\sigma: V \to \Sigma$  is a mapping from variables  $v \in V$  to symbolic expressions  $\gamma \in \Sigma$ .

A symbolic expression  $\gamma \in \Sigma$  is essentially just an expression  $e \in E$  defined over additional names not defined in the IR of the analyzed PLC program. Variables can be read and written to the respective stores, and manipulation is denoted by either accessing, i.e., reading from the store, or substitution, i.e., writing to the store.

#### **Definition 2.6: Substitution**

Substitution of a variable  $u, v, x, y \in V$  with a concrete value  $d \in D$  or a symbolic expression  $\gamma \in \Sigma$  is defined over the concrete and symbolic store as follows

$$\rho[d/v](u) \coloneqq \begin{cases} d & \text{if } u = v, \\ \rho(u) & \text{otherwise} \end{cases} \qquad \sigma[\gamma/y](x) \coloneqq \begin{cases} \gamma & \text{if } x = y, \\ \sigma(x) & \text{otherwise}, \end{cases}$$

where all occurrences of v and y are substituted in the concrete and symbolic store by d and  $\gamma$ , respectively.

Throughout this thesis, the substitution operation of Definition 2.6 is generalized to the short-hand update functions  $\rho[v \mapsto d]$  and  $\sigma[y \mapsto \gamma]$ .

Furthermore, the notations  $\operatorname{eval}_{\rho}(e)$  and  $\operatorname{eval}_{\sigma}(e)$  are used to denote the evaluation of the expression  $e \in E$  with regards to the evaluation relation  $\langle e, \rho \rangle \to d$  for the concrete store and  $\langle e, \sigma \rangle \to \gamma$  for the symbolic store defined in Appendix A, respectively. The definitions for the concrete and symbolic evaluation functions are given in the Definitions 2.7 to 2.8.

#### **Definition 2.7: Concrete Evaluation Function**

Given a concrete store  $\rho$ , the evaluation function  $\operatorname{eval}_{\rho} \colon E \to D$  is defined recursively and assigns to each expression  $e \in E$  a value from the respective domain  $d \in D$ , integer or Boolean.

### **Definition 2.8: Symbolic Evaluation Function**

Given a symbolic store  $\sigma$ , the evaluation function  $\operatorname{eval}_{\sigma} \colon E \to \Sigma$  is defined recursively and assigns to each expression  $e \in E$  a symbolic value from the respective domain  $\gamma \in \Sigma$ , integer or Boolean.

# Static and Dynamic Symbolic Execution

A branch of symbolic program analysis deals with static and dynamic symbolic execution (SE) [Bal & Cop<sup>+</sup> 18]. Before looking at the differences between static and dynamic SE, a high-level description of how SE works is given.

SE automatically explores program paths by executing the underlying CFG of the IR for the respective PLC program using symbolic values for the input variables. In case concrete valuations are also considered, SE is called concolic execution (CE), a portmanteau of concrete and symbolic execution.

### **Definition 2.9: Path**

A path through a CFG is a sequence of m > 0 edges  $e_1, \ldots, e_m$  such that given basic blocks  $b_i, b_j, b_k, b_l \in B$  and 0 < n < m then  $e_n := (b_i, b_j)$  and  $e_{n+1} := (b_k, b_l)$ , then  $b_j \equiv b_k$ .

A path is feasible if there exists an input to the program that "covers" the path, i.e., when the program with that input is executed, the corresponding path is taken. A path is infeasible if there exists no input that covers the path.

The execution strategy of SE can adhere to two different strategies [Kuz & Kin<sup>+</sup> 12]. Either a path is completely executed from the entry to the exit of the CFG

in a depth-first exploration ("DART-style" [God & Kla<sup>+</sup> 05]), or the execution is more shallow and performed in a breadth-first exploration ("EXE-style" [Cad & Gan<sup>+</sup> 08]). This thesis uses the "EXE-style" execution over the "DART-style" execution as it gives more fine-grained control over the execution. SE begins from an *initial* execution state and unfolds the set of reachable execution states in a certain number of "steps". This unfolding leads to a partition of the input space resulting in an enumeration of all feasible paths. In general, a CFG over-approximates the executable behavior.

### Definition 2.10: Execution State [Bal & Cop+ 18]

An execution state  $s = (b_{\ell}, \rho, \sigma, \pi)$ , where

- ▶  $b_{\ell}$  ∈ B is next vertex of the CFG to execute,

- ho is a *concrete store* that maps variables  $v \in V$  to expressions over concrete values,

- $ightharpoonup \sigma$  is a *symbolic store* that maps variables  $v \in V$  to expressions over concrete and symbolic values,

- ▶  $\pi$  denotes the *path constraint* representing a set of conditional expressions taken on the execution path up to vertex  $b_{\ell}$ .

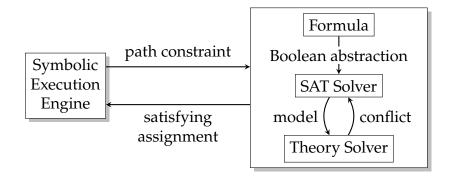

The path constraint  $\pi$  characterizes a set of input parameters for which the program executes along the path [God 07]. The branching conditions are recorded in the path constraint  $\pi$  whenever the execution "forks" at a branch. In the domain of PLC software, the path constraint  $\pi$  also carries constraints on local variables resulting from decisions at branches. A constraint solver is used to decide the feasibility of the recorded paths and can generate a satisfying assignment that can be used as a witness or test case for the particular path.

While in static SE, the whole program source code is represented as a formula by computing the strongest post-conditions beginning from the entry of the CFG, dynamic SE actually executes the program using concrete valuations while maintaining symbolic valuations for input-dependent choices of paths at branches. Consequently, an advantage of dynamic SE is that no false positives are derived, and one can always obtain useful partial results [Bal & Cop<sup>+</sup> 18].

Still, in order to guarantee the absence of bugs, all paths must be enumerated. As execution goes on, the number of enumerated paths can become too large to handle efficiently, resulting in the path explosion problem.

# 2.4 Design Principles of Symbolic Execution

Path explosion is a problem occurring during SE [Bal & Cop<sup>+</sup> 18]. There are four major ways to tackle the problem of path explosion in SE [Bey & Lem 16]:

- 1. Search heuristics for achieving a high level of branch or path coverage as fast as possible

- 2. Compositional symbolic execution, creating summaries of functions or paths and reusing them instead of recomputing already explored states

- 3. Handling of unbounded loops

- 4. Using interpolants for tracking reasons why a particular path is infeasible

These solutions are tightly coupled with how the underlying SE engine and algorithms are designed [Kuz & Kin<sup>+</sup> 12; Kuz & Kin<sup>+</sup> 14].

# 2.4.1 Handling of Loops and Recursion

Standard techniques which allow the analysis of loops and recursion are unrolling and function call inlining [Kuz & Kin<sup>+</sup> 14; Bec & Ulb<sup>+</sup> 15]. A peculiarity of PLC programs is that recursive call chains are forbidden by design as defined in the standard [Int 14]. Static unrolling of loops in PLC programs is usually done up to a specific bound by statically rewriting the underlying IR [Bec & Ulb<sup>+</sup> 15].

In this thesis, no techniques or heuristics have been investigated that deal with the problem of handling loops and recursions efficiently. In fact, the assumption is made that the programs under analysis do not contain any unbounded or "problematic" loops. As PLC programs are employed to solve time-critical tasks, and the standard requires the programs to finish within a specified cycle time [Int 14], it is, therefore, reasonable to assume that programs usually do not contain loops with an unbounded number of iterations [Bec & Ulb<sup>+</sup> 15].

The algorithms of Chapter 4 and Chapter 5 explore loops as long as they cannot prove the infeasibility of the condition.

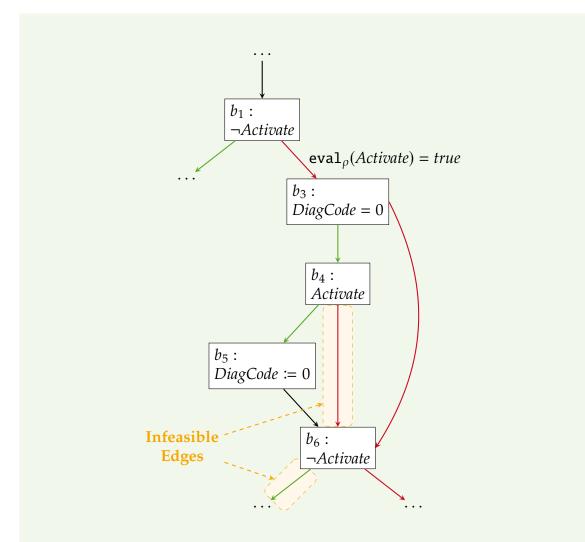

# 2.4.2 Avoiding the Encoding of Infeasible Execution Paths

In general, symbolic program analysis avoids encoding infeasible execution paths by checking for satisfiability at points in the program where the control flow branches. By not considering execution states that represent infeasible paths, the problem of path explosion is combatted by investing solving time earlier in the execution [Kuz & Kin<sup>+</sup> 14]. In this thesis, feasibility checking is also performed when "forking" and is explained in detail in Chapter 4.

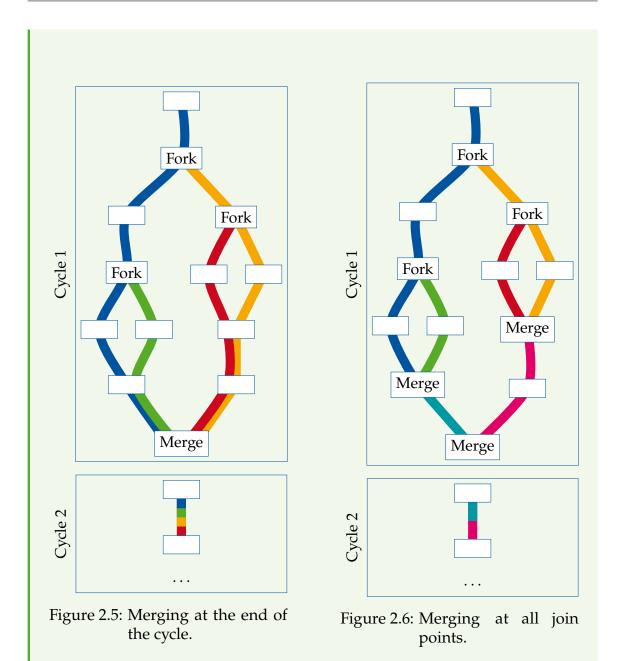

# 2.4.3 Merging of Execution Paths

State merging combines paths into a state [Bal & Cop<sup>+</sup> 18] and is a suitable technique to combat the path explosion problem [Kuz & Kin<sup>+</sup> 14]. Unlike in SA, where it is acceptable that the resulting merged state over-approximates the individual states that were merged, SE for TSG requires more precise information [Kuz & Kin<sup>+</sup> 14].

A possible way to merge all execution paths without any over-approximation reaching a particular vertex is using the path constraint  $\pi$  to determine from which path the information reached this specific vertex.

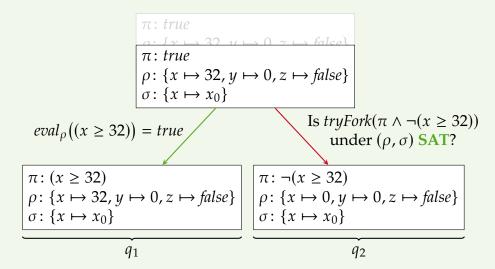

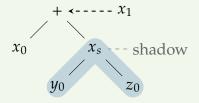

### **Example 2.3: State Merging**

Merging execution states in each cycle of a PLC program yields a linear path growth and is a desired technique to combat the path explosion problem. The tradeoff, however, is that state merging generates more complex execution states. Consider merging the following two execution states described by a path constraint and their concrete and symbolic valuations: