# Test Case Generation from Natural Language Requirements for Embedded Systems with Semantic Role Labeling

Alexander Kugler

Department of Computer Science

**Technical Report**

The publications of the Department of Computer Science of  $RWTH\ Aachen$  ${\it University}$  are in general accessible through the World Wide Web. http://aib.informatik.rwth-aachen.de/

# Test Case Generation from Natural Language Requirements for Embedded Systems with Semantic Role Labeling

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

M. Sc. RWTH Alexander Kugler

aus Aachen

Berichter: Prof. Dr.-Ing. Stefan Kowalewski

Prof. Dr. rer. nat. Bernhard Rumpe

Tag der mündlichen Prüfung: 7. Januar 2025

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar.

Alexander Kugler Lehrstuhl Informatik 11 alexander.kugler@rwth-aachen.de

Aachener Informatik Bericht AIB-2025-04

Herausgeber: Fachgruppe Informatik

RWTH Aachen University

Ahornstr. 55 52074 Aachen GERMANY

ISSN 0935-3232

# **Abstract**

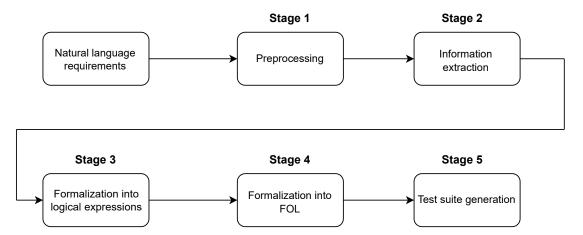

The work presented in this thesis explores the application of Semantic Role Labeling (SRL) for the generation of test cases from natural language requirements for embedded systems. The approach, labelled Test Generation with Semantic Role Labeling (TG-SRL), is composed of five stages and combines machine learning with a rule-based approach. Information extracted via Semantic Role Labeling (SRL) is initially aggregated into logical expressions before being translated into First-Order Logic (FOL) formulae. Test case generation is achieved using Satisfiability Modulo Theory (SMT) solving. By modifying the SMT instance according to defined tactics, a test suite is generated.

The thesis concludes with an evaluation of TG-SRL using a mutant-based strength analysis, and a comparison with the *Nat2Test* approach from Carvalho et al. TG-SRL performs favorably and provides valuable insights into employing Natural Language Processing (NLP) methods, and in particular SRL, in the field of test case generation. The methods and concepts presented in this thesis have been implemented in a publicly available research framework.

# Zusammenfassung

Die in dieser Dissertation vorgestellte Arbeit untersucht den Einsatz von "Semantic Role Labeling (SRL)" zur Generierung von Testfällen aus natürlichsprachlichen Anforderungen für eingebettete Systeme. Der Ansatz, der als "Test Generation with Semantic Role Labeling (TG-SRL)" bezeichnet wird, besteht aus fünf Phasen und kombiniert maschinelles Lernen mit einem regelbasierten Ansatz. Die mittels SRL extrahierten Informationen werden zunächst zu logischen Ausdrücken aggregiert, bevor sie in Formeln der Prädikatenlogik erster Ordnung (FOL) übersetzt werden. Die Generierung von Testfällen erfolgt durch die Lösung von Erfüllbarkeits-Modulo-Theorie (SMT) Instanzen. Durch die Modifikation der SMT-Instanzen gemäß definierten Taktiken wird eine Testsuite erzeugt.

Die Dissertation schließt mit einer Evaluierung von TG-SRL mittels einer auf Mutanten basierenden Stärkeanalyse und einem Vergleich mit dem Ansatz Nat2Test von Carvalho et al. ab. TG-SRL zeigt eine vorteilhafte Performance und liefert wertvolle Einblicke in den Einsatz von Methoden des Natural Language Processing (NLP), insbesondere von SRL, im Bereich der Testfallgenerierung. Die in dieser Arbeit vorgestellten Methoden und Konzepte wurden in einem öffentlich zugänglichen Forschungsframework implementiert.

# Vorwort

Die vorliegende Dissertation ist während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl für Informatik 11 - Embedded Software der Rheinisch-Westfälischen Technischen Hochschule Aachen entstanden.

Herrn Prof. Dr.-Ing. Stefan Kowalewski, Leiter des Lehrstuhls Informatik 11 der RWTH Aachen, danke ich für die intensive Förderung und Betreuung meiner Arbeit, den interessanten technischen Austausch über die letzten Jahre hinweg, und für seine Tätigkeit als Berichter im Rahmen der Promotionsprüfung. Ebenfalls danke ich Herrn Prof. Dr. rer. nat. Bernhard Rumpe für die Übernahme des Korreferats, Frau Prof. Dr.-Ing. Ulrike Meyer für die Übernahme der Fachprüfung und Herrn Prof. Dr. rer. nat. Matthias Müller für den Vorsitz in der Prüfungskommission.

Desweiteren gilt mein Dank meinen Kollegen am Lehrstuhl für Informatik 11, die stets zu einem konstruktiven und freundlichen Arbeitsklima beigetragen haben und immer offen für einen fachlichen Austausch waren. Weiterhin danke ich all denjenigen, die bei der Korrektur dieser Arbeit engagierte Unterstützung geleistet haben.

Abschließend gilt mein besonderer Dank meiner Familie und meinem näheren persönlichen Umfeld für die fortwährende moralische Unterstützung und das entgegengebrachte Verständnis während jeder Phase der Erstellung dieser Arbeit. Meinen Eltern danke ich vor allem für Ihre Förderung und bedingungslose Unterstützung während meiner gesamten akademischen Laufbahn.

Aachen, 06. April 2025

Alexander Kugler

# **Contents**

| 1 | Intro | oductio | n                                                                  | 1  |

|---|-------|---------|--------------------------------------------------------------------|----|

|   | 1.1   | Scope,  | Challenges and Objectives                                          | 2  |

|   | 1.2   | Solutio | on Approach & Contributions                                        | 3  |

|   | 1.3   | Bibliog | graphic Notes                                                      | 4  |

|   | 1.4   | Outlin  | e                                                                  | 5  |

| 2 | Fund  | dament  | cals                                                               | 7  |

|   | 2.1   | Develo  | opment of Embedded Software in the Automotive Industry             | 7  |

|   |       | 2.1.1   | A-SPICE & Autosar Classic                                          | 7  |

|   |       | 2.1.2   | Verification & Validation Activities                               | 10 |

|   | 2.2   | Test C  | Generation from Requirements                                       | 11 |

|   |       | 2.2.1   | Model-Based Test Generation                                        | 12 |

|   |       | 2.2.2   | Mutant-Based Strength Analysis                                     | 14 |

|   | 2.3   | Natura  | al Language Processing                                             | 14 |

|   |       | 2.3.1   | NLP Methods and Common Tasks                                       | 15 |

|   |       | 2.3.2   | Semantic Role Labeling with Proposition Bank Annotations           | 17 |

|   |       | 2.3.3   | Frame Semantic Parsing                                             | 20 |

|   |       | 2.3.4   | NLP Frameworks                                                     | 22 |

| 3 | Rela  | ted We  | ork                                                                | 25 |

|   | 3.1   | Natura  | al Language as the Input Domain                                    | 25 |

|   |       | 3.1.1   | Solimva                                                            | 25 |

|   |       | 3.1.2   | Litmus                                                             | 26 |

|   |       | 3.1.3   | Retna                                                              | 27 |

|   | 3.2   | Use C   | ases as the Input Domain                                           | 28 |

|   |       | 3.2.1   | UMTS                                                               | 28 |

|   |       | 3.2.2   | Text2Test                                                          | 29 |

|   |       | 3.2.3   | Test Case Generation, Selection and Coverage from Natural Language |    |

|   | 3.3   | Contro  | olled Natural Language as the Input Domain                         | 30 |

|   |       | 3.3.1   | Generating Test Cases for Timed Systems from CNL Specifications    | 30 |

|   |       | 3.3.2   | Nat2Test                                                           | 31 |

| 4 | Test  | Gener   | ation with Semantic Role Labeling                                  | 35 |

|   | 4.1   | Overv   | iew                                                                | 35 |

|   | 4.2   | Stage   | 1: Signal Attributes & Preprocessing of Requirements               | 38 |

|   | 4.2   | Diage   | 1. Dignar Herribates & Freprocessing of Requirements               | 0  |

|   | 4.3   | _       | 2: Information Extraction via NLP                                  |    |

# Contents

|     | 4.4  | Stage 3: Processing and Aggregation of Extracted Information into Logical |     |

|-----|------|---------------------------------------------------------------------------|-----|

|     |      | Expressions                                                               | 46  |

|     |      | 4.4.1 Enriching Predicate Frames                                          | 47  |

|     |      | 4.4.2 Formalization into Logical Expressions                              | 49  |

|     |      | 4.4.3 Atomic Expressions for Conditions and Actions                       | 55  |

|     | 4.5  | Stage 4: Formalization into First-Order Logic                             | 58  |

|     |      | 4.5.1 Test Case Generation                                                | 59  |

|     | 4.6  | Stage 5: Test Suite Generation                                            | 64  |

|     | 4.7  | Implementation                                                            | 67  |

|     |      | 4.7.1 Frameworks and Tools                                                | 69  |

|     |      | 4.7.2 Preprocessing of Requirements                                       | 70  |

| 5   | Eval | uation                                                                    | 75  |

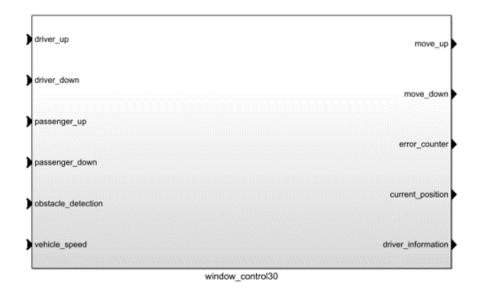

|     | 5.1  | Window Control System                                                     | 76  |

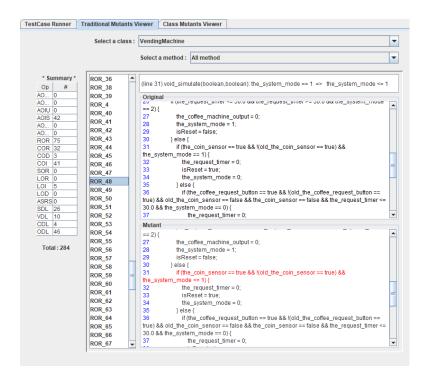

|     |      | 5.1.1 Mutant-Based Strength Analysis                                      | 77  |

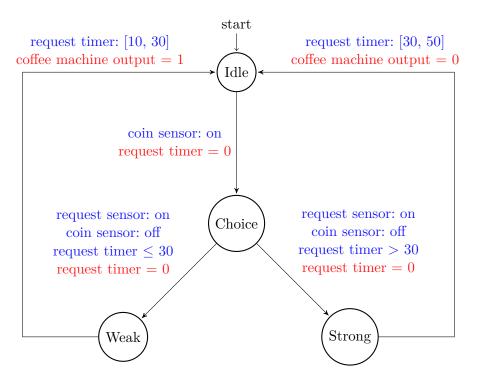

|     | 5.2  | Vending Machine System                                                    | 81  |

|     |      | 5.2.1 Mutant-Based Strength Analysis                                      | 85  |

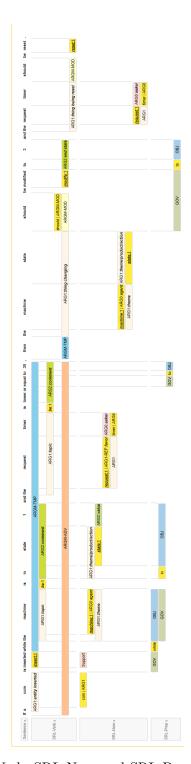

|     | 5.3  | Daimler Turn Indicator System                                             | 91  |

|     |      | 5.3.1 Mutant-Based Strength Analysis                                      | 93  |

|     | 5.4  | Evaluation of Objectives                                                  | 94  |

|     | 5.5  | Limitations & Future Work                                                 | 95  |

|     |      | 5.5.1 Large Language Models                                               | 96  |

| 6   | Con  | clusion                                                                   | 101 |

| 7   | Арр  | endix                                                                     | 103 |

| Bil |      |                                                                           | 136 |

# **List of Tables**

| 2.1         | Exemplary signal specified as time-value pairs. Step size of 0.1                                                                                                      | 13 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2         | Overview of core Proposition Bank (ProbBank) semantic roles                                                                                                           | 19 |

| 2.3         | Semantic roles of commas according to [42]                                                                                                                            | 21 |

| 2.4         | ProbBank Framesets for "to buy" and "to sell"                                                                                                                         | 22 |

| 3.1         | Exemplary requirement, taken from [68], conforming to the grammar from                                                                                                |    |

| 3.2         | Listing 3.1                                                                                                                                                           | 31 |

|             | random testing                                                                                                                                                        | 33 |

| 4.1         | Content of a requirement frame                                                                                                                                        | 41 |

| 4.2         | Content of a predicate frame                                                                                                                                          | 42 |

| 4.3         | Exemplary predicate frame based on SRL output in Figure 4.1                                                                                                           | 44 |

| 4.4         | Possible rephrasings for the given sentence                                                                                                                           | 44 |

| 4.5         | Exemplary requirement frame with identified conditional parts                                                                                                         | 45 |

| 4.6         | Overview of inspected tags and examples for associated regular expressions.                                                                                           | 48 |

| 4.7         | Exemplary predicate frames                                                                                                                                            | 49 |

| 4.8         | Exemplary predicate frames                                                                                                                                            | 50 |

| 4.9<br>4.10 | Expressions produced by the "extended" tactic for the disjunction $x \lor y \lor z \lor u$ . Overview of disjunctions generated with the "normal" comparison operator | 67 |

|             | tactic.                                                                                                                                                               | 67 |

| 5.1         | Input and output signals from the Window Control system                                                                                                               | 79 |

| 5.2         | Mutation testing results for the Window Control system                                                                                                                | 80 |

| 5.3         | Input and output signals from the Vending Machine system                                                                                                              | 83 |

| 5.4         | Enumeration to integer mapping for the <i>Vending Machine</i> system                                                                                                  | 83 |

| 5.5         | Enumeration in integer mapping for the <i>Vending Machine</i> system                                                                                                  | 84 |

| 5.6         | Exemplary test case from Nat2Test for the Vending Machine system                                                                                                      | 84 |

| 5.7         | Excerpt of an exemplary test case from TG-SRL for the Vending Machine                                                                                                 |    |

|             | system                                                                                                                                                                | 85 |

| 5.8         | Mutation testing results for the <i>Vending Machine</i> system                                                                                                        | 85 |

| 5.9         | Illustration why the condition "timer $>= 10 \&\&$ timer $<= 30 \&\&$ mode $== 3$ " will always be triggered with a timer value of 10                                 | 88 |

| E 10        |                                                                                                                                                                       | 00 |

| J.10        | Mutation testing results for the <i>Vending Machine</i> system after accounting for semantically equivalent mutants                                                   | 89 |

| E 11        | v 1                                                                                                                                                                   | 09 |

| ე.11        | Mutation testing results for the <i>Vending Machine</i> system after enforcing                                                                                        | 00 |

| F 10        | changes of the initial value for a signal                                                                                                                             | 90 |

| 5.12        | Mutation testing results for the <i>Vending Machine</i> system                                                                                                        | 91 |

# List of Tables

| 5.13 | Input and output signals from the Turn Indicator system 92                        |

|------|-----------------------------------------------------------------------------------|

| 5.14 | Mutation testing results for the <i>Turn Indicator</i> system 93                  |

|      | V                                                                                 |

| 7.1  | List of requirements for the Window Control system                                |

| 7.2  | Mutations of the Window Control system                                            |

| 7.3  | Preprocessed list of requirements for the $Vending\ Machine\ system.$ 106         |

| 7.4  | List of requirements for the <i>Vending Machine</i> system in the SysReq-CNL. 107 |

| 7.5  | Preprocessed list of requirements for the <i>Turn Indicator</i> system 113        |

| 7.7  | Exemplary test case from TG-SRL for the $Vending\ Machine\ system.$ 126           |

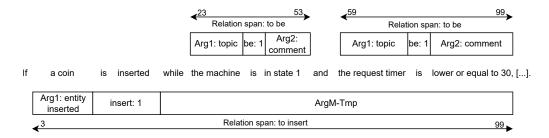

| 7.6  | Output from [46] on the sentence "If a coin is inserted while the machine is      |

|      | in state 1 and the request timer is lower or equal to 30, then the machine        |

|      | state should be modified to 3 and the request timer should be reset." $128$       |

# List of Figures

| 1.1                                                         | Overview of the TG-SRL approach presented in this thesis                                                                                                                                                                                   | 4                                                |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Overview of Automotive SPICE (A-SPICE), adapted from [5] Autosar Classic architecture and communication between layers [13] Application software structure according to Autosar Classic Simplified overview of model-based test generation | 8<br>9<br>10<br>12<br>17<br>18<br>18<br>20<br>21 |

| 3.1<br>3.2<br>3.3                                           | Overview of Solimva based on a figure in [60]                                                                                                                                                                                              | 26<br>27<br>32                                   |

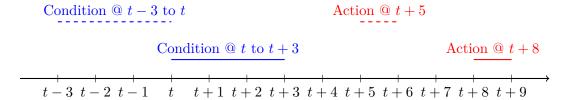

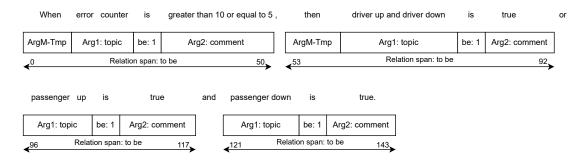

| 4.1<br>4.2                                                  | Exemplary SRL tags created with the <i>AllenNLP</i> online demo [41] Possible interpretations of the temporal behavior for the requirement "If <i>signal a</i> is 2 for 3 seconds, then add 10 to <i>signal b</i> after 5 seconds."        | 43<br>52                                         |

| 4.3<br>4.4                                                  | SRL output from $CogComp$ - $NLP$ [76] showcasing valid relation spans SRL output from $CogComp$ - $NLP$ [76] showcasing overlapping and thus invalid relation spans                                                                       | 53<br>53                                         |

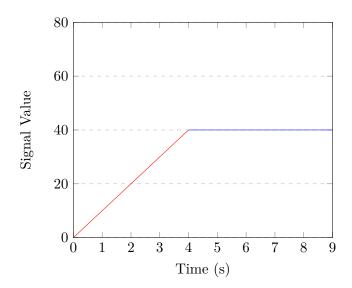

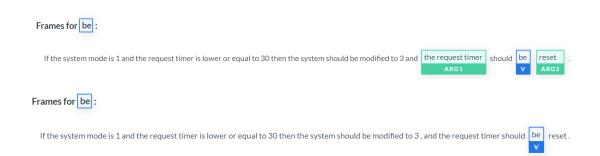

| 4.5<br>4.6                                                  | Exemplary output signal with linear and constant behavior                                                                                                                                                                                  | 55<br>61<br>72                                   |

| 4.7<br>4.8                                                  | Exemplary output from Cogcomp-NLI [70]                                                                                                                                                                                                     | 73<br>74                                         |

| 5.1                                                         | MuJava method-level mutation example                                                                                                                                                                                                       | 76                                               |

| 5.2                                                         | Black-box view on the Window Control system                                                                                                                                                                                                | 77                                               |

| 5.3                                                         | Detailed view on the Window Control system                                                                                                                                                                                                 | 78                                               |

| 5.4                                                         | Variant subsystems for the <i>Window Control</i> system to facilitate mutation testing.                                                                                                                                                    | 80                                               |

| 5.5                                                         | State machine for the <i>Vending Machine</i> system. Conditions are colored in                                                                                                                                                             | 30                                               |

| 5.0                                                         | blue while actions are colored in red                                                                                                                                                                                                      | 82                                               |

| 5.6                                                         | SRL-Verb, SRL-Nom and SRL-Prep output from [76]                                                                                                                                                                                            | 98                                               |

| 5.7                                                         | Generated test cases from GPT-40 [89] on the given input requirement                                                                                                                                                                       | 99                                               |

| 5.8 | Example that illustrates how GPT-40 | [89] | ] can | be | utilized | to | resolve |       |

|-----|-------------------------------------|------|-------|----|----------|----|---------|-------|

|     | ambiguity in a given requirement    |      |       |    |          |    |         | . 100 |

# List of Acronyms

A-SPICE Automotive SPICE

BERT Bidirectional Encoder Representations from Trans-

formers

CAN Controller Area Network

CASE Connected, Autonomous, Shared and Electric

CNL Controlled Natural Language

CoNLL Conference on Computational Natural Language

Learning

CSP Communicating Sequential Processes

DFRS Data-Flow Reactive Systems

DRS Discourse Representation Structures

FOL First-Order Logic

FSP Frame Semantic Parsing

IMR Internal Model Representation

LIN Local Interconnect Network

LLM Large Language Models

LLM Large Language Model

MBD Model-based Development

MBSE Model-based System Engineering

NER Named Entity Recognition NLP Natural Language Processing NLU Natural Language Understanding

OCL Object Constraint Language

POS Part of Speech ProbBank Proposition Bank

RTE Runtime Environment

# List of Acronyms

RUCM Restricted Use Case Modeling

RWTH Aachen Rheinisch-Westfälische Technische Hochschule Aachen

SCR Software Cost Reduction

SDV Software Defined Vehicle

SMT Satisfiability Modulo Theory

SRL Semantic Role Labeling

SuT System under Test

SW-C Software Component

TG-SRL Test Generation with Semantic Role Labeling

UML Unified Modeling Language

V&V Validation & Verification

WSD Word Sense Disambiguation

# 1 Introduction

In the automotive industry there is a paradigm change towards Software Defined Vehicles (SDVs). Connected, Autonomous, Shared and Electric (CASE) mobility is disrupting the automotive value chain, and software is emerging as the principal driver of innovation [1]. Comparable to today's smartphone, a SDV needs to be seamlessly integrated into a large software ecosystem. This necessitates regular software deployments via over-the-air updates to close security vulnerabilities, improve existing features, or simply deliver new ones. However, in contrast to software for smartphones, software in a vehicle needs to adhere to strict quality standards and safety regulations, such as the ISO26262 [2]. Thus, rigorous testing is critical to guarantee software quality and adherence to regulations. Nowadays, testing efforts can contribute between 40-70 percent of the overall project costs [3]. Without countermeasures, this share can be expected to increase significantly in the context of SDVs.

A core strategy to tackle the challenge of increasing update frequency and rising testing efforts is automation. Efforts for testing software can be split into effort for test planning, design, implementation, execution and evaluation. The focus in this thesis is on the design and implementation phase, i.e., it is assumed that a test strategy has been derived and requirements-based testing has been identified as a required activity. In today's automotive industry, the design and implementation of requirements-based test cases is either partially automated or a manual activity. In cases of partial automation, most approaches entail significant manual effort [4]. Thus, the automation of test generation has significant potential to improve efficiency in software development and reduce associated costs. While there exist a few approaches which enable test case generation based on formal models, the effort to create such formal models out of requirements can be considerable. In many cases, effort for specifying test cases directly from natural language requirements simply shifts to the formalization of these requirements. In contrast, generating requirements-based tests directly from natural language requirements has proven difficult due to the ambiguity, incompleteness, and sometimes inconsistency of such requirements.

This thesis proposes an approach that tries to tackle these challenges with the help of Natural Language Processing (NLP) methods. In particular, a framework for test generation based on natural language requirements using Semantic Role Labeling (SRL) is presented. In addition, the feasibility and performance of the proposed approach is investigated. As an acronym for the proposed method, TG-SRL (Test Generation with Semantic Role Labeling) is employed throughout this thesis.

The remainder of this chapter is structured as follows. First, the scope, problem statement, and objectives of this thesis are defined. Next, the chosen solution approach is summarized, and major contributions are highlighted. At the end of the chapter, an outline for the remaining thesis is presented.

# 1.1 Scope, Challenges and Objectives

This thesis focuses on automatic test generation based on natural language requirements for embedded systems. It is assumed that the requirements intended for test generation have a sufficient level of detail for the generation of executable test cases. The requirements are also assumed to describe a System under Test (SuT) as a black-box by specifying system behavior based on observable in- and output signals. Applied to the automotive context, where software is often developed according to the A-SPICE standard [5], the presented approach is applicable to requirements that are used in the process areas SWE.1 to SWE.3 (see Section 2.1.1).

Furthermore, the thesis is scoped to functional testing, also referred to as requirements-based or specification-based testing. In general, it is possible to distinguish between structural and functional testing (see Section 2.1.2). While structural tests can be generated automatically based on the structure of the System under Test (SuT), they do not necessarily reveal errors in the functional behavior of software. Functional testing instead directly tests the behavior of the SuT against the expected behavior that has previously been specified in the requirements. Regulations in the automotive domain, such as the ISO26262-6 [2], mandate functional testing for safety critical software. Generally, this test category is crucial for delivering a reliable product with a satisfactory and dependable user experience.

While solutions exist to generate functional test cases based on formalized requirements, requirements are usually specified in natural language [6]: according to surveys, 79 % of requirements are documented in free-flow natural language [3] and only 7 % use a formal specification [7]. Although natural language is inherently ambiguous, it is used for ease in comprehension and ease in sharing between the different stakeholders [7]. Existing approaches in literature to generate test cases based on natural language requirements face several major challenges:

## Challenges

- Input domain restrictions: The input domain is restricted in many approaches to reduce or eliminate challenges that come with natural language. For example, some methods enforce the adherence to a specific template, while others employ a Controlled Natural Language (CNL) defined by a grammar. Restrictions on the input domain can significantly simplify information extraction, and the formalization into a representation that enables automatic test generation. The trade-off, however, is the need to partially formalize the requirements, albeit in a subset of natural language.

- Automation degree & abstraction gap of generated test cases: Another challenge is the automation degree that can be achieved. Many methods require manual interaction of a user, e.g., for the creation of a domain-specific dictionary. A trade-off between generalizability and automation degree can be observed in existing literature (refer to Chapter 3): approaches that operate on a less constrained input domain usually require more manual intervention to resolve ambiguity or to deal

with incomplete domain knowledge.

Furthermore, generated test cases are not always executable. Depending on the abstraction level of the requirements, but also on the employed approach, the manual effort to translate abstract test cases into executable ones can be significant.

• Test suite strength & size: Generated test suites need to be strong in order to provide value. Strength in this context is defined as a test suite's capability to detect erroneous behavior of an SuT. If a generated test suite performs worse than a manually created test suite in detecting faults, regulations and standards will continue to enforce the manual creation of test suites. On the other side of the spectrum, generated test suites might be very strong but also very large, potentially consisting of millions of test cases. Prohibitively large test suites inhibit the applicability to software development as the time and resource usage for test execution can be a limiting factor, especially for tests that involve real hardware.

The approach presented in this thesis tries to tackle the mentioned challenges. The objectives of TG-SRL are enumerated in the following:

# **Objectives**

- Provide a proof of concept for a test generation framework that operates directly

on natural language requirements. The input domain should be as unconstrained

as possible, i.e. restrictions on the input language should be kept to a minimum.

- Achieve the highest automation degree possible: avoid the manual creation of dictionaries or domain knowledge, and avoid manual steps within the automation process. The generated test cases should be executable without manual refinement.

- Optimize the strength of the test suite while accounting for test suite size: maximize the test suite's capability to detect system behavior that deviates from the specification, and keep its size within reasonable boundaries.

# 1.2 Solution Approach & Contributions

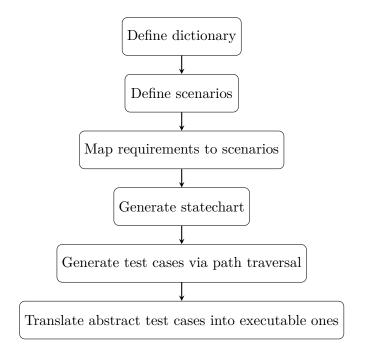

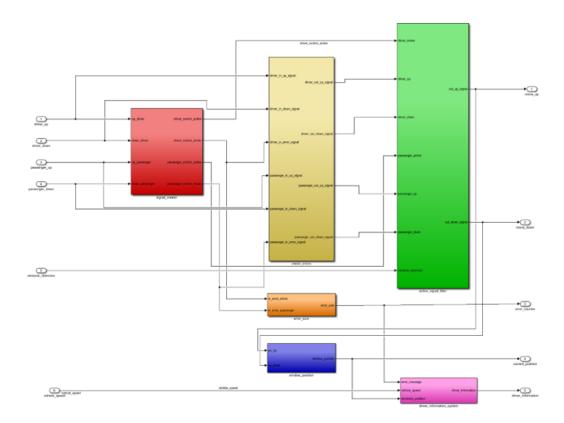

The method for automated test generation adopted in this thesis operates on unrestricted natural language and combines machine learning with a rule-based approach. To extract syntactic and semantic information from the natural language requirements, Semantic Role Labeling (SRL) and other Natural Language Processing (NLP) techniques are applied. Based on the extracted information, a ruleset is applied to create a formal representation of the requirements in First-Order Logic (FOL). Concrete test cases are generated via a Satisfiability Modulo Theory (SMT) solver. By modifying the FOL constraints according to defined tactics, a robust test suite with strong error detection capabilities is created. The approach is evaluated with a mutant-based strength analysis. Figure 1.1 provides an overview of TG-SRL.

Figure 1.1: Overview of the TG-SRL approach presented in this thesis.

In the following, the main contributions of this thesis are summarized:

#### **Contributions**

- Development of a method for extracting information relevant for test generation from natural language requirements based on the output of Semantic Role Labeling. Formalization of extracted information into logical expressions as an intermediate representation.

- Development of a method to formalize extracted information from the intermediate representation into First-Order Logic for the purpose of test generation. In particular, the method considers the need to bring the SuT into a specific state prior to test execution.

- Development of tactics for altering First-Order Logic constraints in order to generate a strong test suite.

- Analysis of existing state-of-the-art Semantic Role Labeling and Frame Semantic Parsing frameworks to extract semantic information from natural language software requirements.

- Evaluation of the presented test generation approach TG-SRL with a mutant-based strength analysis, and a comparison to *Nat2Test* from [8].

- Implementation of methods and concepts into a research framework. Publication of the framework as open source software [9].

# 1.3 Bibliographic Notes

While this thesis addresses test design and implementation, a framework for test execution and evaluation is required to assess the approach. The framework chosen in this thesis is Arttest [10, 11]. Arttest was developed in a joint industrial project between RWTH Aachen and the Ford Research Center in Aachen. The author of this thesis together with Norbert Wiechowski and Norman Hansen were major contributors to the tool. The approach TG-SRL has not yet been published previously and has been created by the author of this thesis after finishing his work on Arttest independently of any industry collaboration.

# 1.4 Outline

The remainder of this thesis is structured as follows. In Chapter 2, necessary terminology and fundamentals are introduced. Chapter 3 addresses related work, while Chapter 4 presents TG-SRL in detail. In Chapter 5, TG-SRL is evaluated with a mutant-based strength analysis. Chapter 6 concludes this thesis by summarizing the results.

# $1\ Introduction$

# 2 Fundamentals

This chapter is structured into three main sections. The first section provides an overview of the automotive product development process. The subsequent section presents an introduction to test generation from requirements. The final section introduces the fundamentals of Natural Language Processing (NLP).

# 2.1 Development of Embedded Software in the Automotive Industry

In this section, the development processes utilized in the automotive industry are introduced to establish the relevant terminology and define the scope of this thesis.

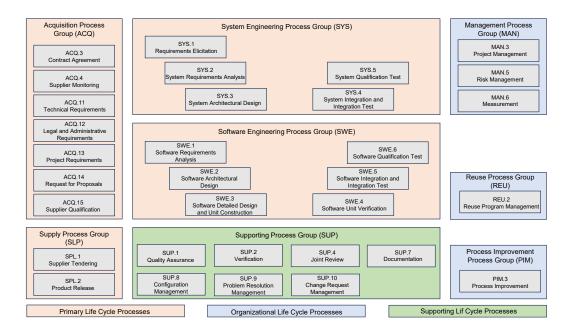

#### 2.1.1 A-SPICE & Autosar Classic

In the automotive industry, development traditionally happens according to the V-model, which breaks down product development into several phases of system and software development. During each phase, the V-model emphasizes the need for Validation & Verification (V&V) activities. Automotive SPICE (A-SPICE) [5], a domain specific variant of the international standard ISO 15504, builds on the V-model, and defines a process framework to ensure that the development process complies with defined qualitative thresholds. An overview of the A-SPICE framework is provided in Figure 2.1. A-SPICE defines several process groups that tackle different areas of product development, such as the project management process group "MAN", or the acquisition process group "ACQ". The system engineering process group "SYS" combined with the software engineering process group "SWE" represent the V-model.

System Engineering Process Group The development of a product starts with several system engineering activities, in which stakeholder requirements are elucidated and broken down into system and feature-level requirements. These requirements describe the behavior and architecture of the system in textual notation. In parallel, graphical notations such as UML or SysML diagrams can be used to specify the system's static and dynamic behavior. In the automotive industry, the term Model-based System Engineering (MBSE) describes a methodology that uses SysML [12] diagrams to model a system's architecture and behavior. The employed SysML diagrams heavily differ depending on the MBSE methodology, but use-case, sequence, activity diagrams, and statecharts are commonly used. MBSE offers the main benefit that the visualization of the architecture and behavioral interactions between system elements facilitates the discussion between stakeholders. In addition, complex dependencies between system elements can be better

Figure 2.1: Overview of A-SPICE, adapted from [5].

captured by models in comparison to text alone.

System engineering activities can be mapped to SYS.1-3 in Figure 2.1. According to A-SPICE, it is necessary to define and plan the system integration and qualification tests for SYS.4 and 5 during these development stages.

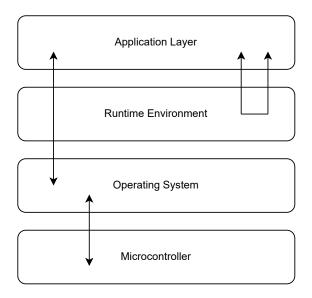

Software Architecture according to Autosar Classic After the system architecture has been designed and the system has been decomposed into hardware and software, software requirements and the software architecture need to be created. A brief introduction to the currently prevailing software architecture in the automotive industry is given to establish common terminology, and clarify the scope for this thesis. The architecture described here is defined by the Autosar Classic standard [13].

Simplified, embedded software today consists of application software communicating via a communication layer with either the operating system or other application software, as depicted in Figure 2.2.

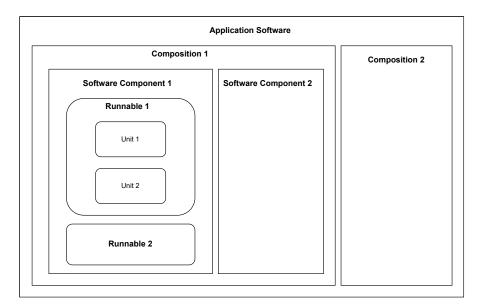

In Autosar Classic, this communication layer is called Runtime Environment (RTE). The operating system is referred to as basic software and it consists of several modules that offer services such as diagnostic event monitoring. Basic software services are heavily standardized in Autosar Classic [13]. The application software may consist of multiple levels of compositions, which in turn contain Software Components (SW-Cs). SW-Cs can contain runnables, which contain units. Figure 2.3 depicts this architecture. SW-Cs are independent of each other in Autosar Classic: an existing SW-C can be deployed on different hardware according to needs, and will communicate with other SW-Cs and the basic software via the RTE. During development of the components it is not determined

Figure 2.2: Autosar Classic architecture and communication between layers [13].

whether this communication will happen via e.g. Ethernet, CAN, LIN, or even onboard (inter-process) communication. Thus, independence of the application software from the deployment scenario is achieved. This is one major goal of Autosar Classic as it enables reuse of application software.

The requirements intended as an input to the TG-SRL approach are requirements to either application software or operating system services.

**Software Engineering Process Group** Given an Autosar Classic architecture, in SWE.1 requirements for the application software and basic software are analyzed, derived and extended. In SWE.2 and SWE.3, the design and requirements for software compositions, software components, runnables and units are derived. During the design of the software, A-SPICE foresees the creation of unit, integration, and software qualification tests which will be executed and evaluated in SWE.4, SWE.5, and SWE.6 respectively.

In the context of this thesis, as an input for the test generation, natural language requirements from either SWE.1, SWE.2, or SWE.3 are assumed. Such requirements specify application, composition, component, runnable, or unit behavior based on their input and output signals. In addition, they usually contain sufficient information to generate executable test cases. The output from the test generation approach in this thesis are thus unit or integration tests related to either SWE.4 or 5. In contrast, system requirements from SYS.1-3 are often too abstract to generate executable test cases. While there exist approaches to generate abstract test cases from system requirements, the generation of system qualification tests is not in the scope of this thesis.

Based on the requirements and architecture from SWE.1-3, the software components and units can be implemented. Implementation can be done within a Model-based Development (MBD) environment, or by directly writing code.

Figure 2.3: Application software structure according to Autosar Classic.

Model-based Development With MBD, the main development artifacts are models rather than code. Models are represented by a graphical notation with defined syntax and semantics. Based on these models, code can be generated automatically. Abstraction is a core concept of MBD. Modeling elements of a modeling language are usually domain specific and thus closer to the actual problem domain than source code of programming languages [14]. In the automotive domain, MBD enables domain experts, such as mechanical and electrical engineers, with little to no background in software development to develop automotive embedded software.

# 2.1.2 Verification & Validation Activities

Validation & Verification (V&V) activities in automotive product development encompass a variety of tasks, including static analysis, guideline checking, structural testing, and functional testing. In this thesis, the focus is on functional test cases derived from requirements.

For the scope of this thesis, test cases are defined as follows:

**Definition 2.1.1** (Test case). A set of test inputs, execution conditions, and expected results developed for a particular test objective, such as to exercise a particular program path, or to verify compliance with a specific requirement.

A test suite is defined as a collection of test cases.

Structural tests, such as coverage tests, can be generated automatically by analyzing the control and data flow of models or code, and achieving certain coverage criteria (e.g. statement, decision or branch coverage [15]). Combined with techniques from static analysis, structural test cases can, for instance, help find unreachable code or violations of

variable ranges. However, structural test cases do not check the system behavior against its specification and thus do not reveal errors in the functional behavior of code.

Typically, functional test cases are manually derived from requirements. Manual creation of such test cases has several issues. Firstly, the effort for creating test cases manually can be significant [3], thus test strategies usually consider a test end criteria to find a reasonable trade-off between test efforts and test coverage [16]. In requirements-based testing, exemplary test end criteria are requirements coverage or conformance. For example, the test strategy could specify that it is sufficient to create one test case per requirement.

A second challenge comes with changes to requirements as they necessitate an update of the derived test cases. With software changes becoming increasingly frequent in the context of SDVs, this implies growing test efforts during the post-production lifecycle of a vehicle or product.

A third challenge with both manual and automatic test generation is the quality of the requirements: natural language requirements can be ambiguous, incomplete or inconsistent. During manual specification, the tester deals with these challenges by correcting inconsistencies (if perceived), making assumptions about the behavior for incomplete requirements, and interpreting potentially ambiguous requirements. Thus, the quality of test cases is heavily dependent on the expertise and knowledge of the tester. In an automated approach, the quality of requirements themselves is critical. For instance, in the case of inconsistent requirements, a test generation framework may hint to the inconsistencies but not automatically resolve them. Chapter 4 provides details on how the proposed framework deals with ambiguity, incompleteness, or inconsistency in natural language requirements.

Black-Box, Grey-Box & White-Box Testing Testing methodologies can be categorized into three types: black-box, grey-box, and white-box testing [15]. If only the inputs and outputs of an SuT are accessible within a test case, this is called black-box testing. For functional testing, black-box testing is usually sufficient as requirements often specify the output behavior of an SuT based on its inputs. In contrast, structural testing necessitates white-box access to the models or code, i.e. it is necessary to be able to access internal signals and variables in order to determine the data and control flow. There are use-cases where selected internal variables need to be monitored or modified, e.g. for fault injection into a system. In case a testing framework supports monitoring and overriding selected internal signals, this is referred to as grey-box testing.

# 2.2 Test Generation from Requirements

This section introduces the fundamentals of generating test cases from requirements. Whereas Section 2.3 focuses on NLP techniques to extract information from natural language requirements, this section provides a broader overview.

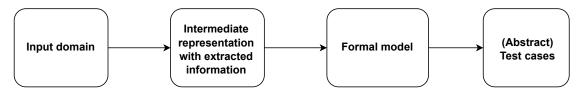

Figure 2.4: Simplified overview of model-based test generation.

#### 2.2.1 Model-Based Test Generation

An overview of the general approach for model-based test generation is provided in Figure 2.4. Initially, information must be extracted from the input domain. Some approaches directly create a formal model while others utilize an intermediate representation to first collect and aggregate extracted information. Once this information is translated into a formal model, various model-specific strategies can be employed to generate test cases. Whether resulting test cases are abstract or executable depends on the approach and the input domain.

**Input Domain** The input domain can range from informal to formal notations. As such, requirements can take the form of natural language, Controlled Natural Language (CNL), use-case diagrams, or state charts that depict the system behavior. Each notation allows for an enhanced degree of formalization by imposing additional constraints on the input domain. For instance, a use-case diagram might be constrained to include only controlled natural language. Further, the use-case diagram's structure and content may be constrained by a template. Such a template could stipulate the use of keywords or the presence of structural elements like pre- and post-conditions.

This thesis focuses on approaches that use either natural language or Controlled Natural Language (CNL) as the input domain. Approaches that rely on a fully formalized model are out of scope.

Controlled Natural Languages CNLs are subsets of natural language with a restricted grammar and vocabulary, designed to reduce or eliminate ambiguity and complexity. Two methods exist to derive a controlled language: either via restriction of natural language, or via constructing a CNL from the ground up by defining its grammar and syntax rules. The latter approach is used by the authors of [17] to generate test cases and is elaborated upon in Chapter 3. Examples of CNLs include Attempto [18], Simplified Technical English [19], Processable Language (PENG) [20], Gherkin [21], and SysReq-CNL [8]. Typically, a trade-off is observed between the naturalness and predictability of controlled languages [22]. Languages defined via a grammar from the ground up tend to be less natural but highly predictable. Generating tests with such languages is simpler compared to those formed by restricting natural language, which are more comprehensible and natural, albeit less predictable. For a more thorough analysis, the reader is directed to [22].

**Formalization** Information extraction is highly dependent on the formalization degree of the input domain. In the case of a CNL, information extraction can make use of the restrictions imposed by the CNL. In the case of natural language input, Natural Language Processing (NLP) techniques can help with extracting the necessary information for test generation.

Based on the extracted information, an intermediate model might be employed to aggregate and process the collected information. Following this, a formal model is created, either directly from the extracted information, or based on the intermediate representation. Examples of formal models utilized in the literature include hybrid automata, state charts, logic formula or process algebras.

One peculiarity for test generation is the encoding of time. Some methods do not account for time-dependent behavior in a test case. Those that do either use formal models that inherently handle time, such as hybrid automata, or logically encode time into the formalization. The consideration of time is vital when testing the behavior of automotive embedded systems, as a test case specifies the behavior of multiple variables or signals over a certain test duration. In the context of embedded systems, the sample time, also referred to as step size, refers to the rate at which a discrete system samples its inputs. Consequently, time can be treated as discrete, and signals can be thought of as time-value pairs as shown in Table 2.1. For a more comprehensive classification of formal models for test generation, the reader is referred to [23].

| Time | Signal A |

|------|----------|

| 0.0  | 1        |

| 0.1  | 2        |

| 0.2  | 5        |

| 0.3  | 0        |

Table 2.1: Exemplary signal specified as time-value pairs. Step size of 0.1.

**Test Generation** Once a formal model is created, test cases need to be derived. The algorithm for test generation highly depends on the underlying formal model. Approaches employing automata or state charts often use structural methods to generate test cases, e.g. via path or state coverage algorithms. In contrast, if the formalization is a logical formula, a solver might be used. For process algebras, refinement checking is one valid approach to generate test cases. A test generation method from the authors of [24], which employs refinement checking on a process algebra known as Communicating Sequential Processes (CSP) [25], is detailed in Chapter 3.

The generated test cases are either abstract or can be directly executed on the SuT. Methods utilizing requirements on the system level, or less detailed inputs such as use-case diagrams, will generally only generate abstract test cases. In contrast, approaches utilizing more detailed requirements, such as software requirements, are capable of generating executable test cases.

# 2.2.2 Mutant-Based Strength Analysis

One method to evaluate the performance of a test suite is so-called mutation testing or mutation-based strength analysis. With mutation testing, the idea is to artificially modify the SuT (e.g., a program) and introduce errors. The resulting system is called a mutant. To automatically and strategically mutate an SuT, so-called mutation operators can be applied. An example for a mutation operator is replacing basic binary arithmetic operators such as + or \* with other binary arithmetic operators. If the whole test suite detects the error of a mutated SuT, i.e. at least one test case of the test suite fails, the mutant is considered *killed*. If a test suite does not detect the error of a mutated system, the mutant is considered *alive*. The mutation score is calculated as the quotient of all killed mutants and the total number of mutants:

$$Mutation Score = \frac{Number of Killed Mutants}{Total Number of Mutants}$$

(2.1)

A higher mutation score indicates a better performing test suite.

A few limitations exist with mutant-based strength analysis. Firstly, frameworks utilizing mutation operators for automatically generating mutants often introduce one error per mutated program. While a test suite might be good at detecting single modifications of an SuT, it might not be suited to detect cases where multiple errors are introduced simultaneously. In general, mutant-based strength analysis only provides an indication for the effectiveness of a test suite to detect errors, but does not prove its effectiveness. Another disadvantage with automatic mutant generation comes with the undecidability of program equivalence [26]. Generated mutants can be semantically equivalent to the original SuT, so the mutation score is always a worst-case estimate for the performance of the test suite on the given mutants. For instance, Listing 2.1 shows several modifications that are semantically equivalent to the unmodified statement in the programming language Java. A test suite will not be able to detect such mutations, thus lowering the mutation score.

# 2.3 Natural Language Processing

The test generation method presented in this thesis operates on unrestricted natural language. In order to extract the necessary information from the natural language requirements, Natural Language Processing (NLP) techniques are employed. This section introduces relevant NLP techniques, provides a brief overview of methods for extracting semantic information from natural language, and presents popular NLP frameworks that facilitate some form of semantic information extraction.

NLP, an interdisciplinary subfield of linguistics, computer science, and artificial intelligence, aims to enable computers to understand natural language, including its contextual nuances. While NLP encompasses both written text and speech recognition, the scope of this thesis is limited to the application of NLP techniques to written text.

```

// original code

a = a + 1;

// mutant (introduce ++)

a = a++ + 1;

// mutant (introduce --)

a = a-- + 1;

// original code

if (a == true)

// mutant (modify condition)

if (a)

```

Listing 2.1: Code snippet with semantically equivalent mutations in Java.

# 2.3.1 NLP Methods and Common Tasks

NLP has traditionally been achieved via rule-based techniques, i.e. the hand-coding of a set of rules, also referred to as symbolic NLP [27]. In the last decades, statistical techniques [28, 29, 30, 31, 32] and large, hand-annotated training corpora [33, 34], as well as machine learning advancements have had a major impact on the field of NLP and enabled the development of sophisticated syntactical and semantic analysis [35]. While statistical techniques such as Hidden Markov Models have been very successful for certain NLP tasks, the major drawback is the reliance on elaborate feature engineering [36]. With the rise of deep neural networks and automatic / unsupervised learning methods, neural networks have become the dominant method in current NLP research [37]. Major advantages of neural networks in comparison to rule-based methods include the robustness to unfamiliar or erroneous input. In addition, a neural network's performance can be improved by simply providing additional training data while improving a system based on handwritten rules can only be achieved by increasing the complexity of the rules, thus making maintenance and extension more difficult.

The following paragraph provides a brief overview of the most common NLP tasks, as specified by [38], which are relevant to both related work and TG-SRL. The overarching goal of TG-SRL is Natural Language Understanding (NLU), also referred to as natural language interpretation. NLU involves converting chunks of text into more formal representations, such as First-Order Logic structures, to facilitate manipulation by a computer program. NLU involves the identification of the intended semantic using an array of NLP techniques. The framework presented in this thesis primarily uses Semantic Role Labeling (SRL), which relies on several other NLP tasks, including Part of Speech (POS) tagging and Named Entity Recognition (NER).

## **Text Processing**

• Word Segmentation This task involves separating a continuous text into individual words. As words are separated by spaces in English, this task is easy to achieve for the English language.

## Morphological Analysis

• Lemmatization This task involves the removal of inflectional endings and returning the base dictionary form of a word, also known as a lemma. Unlike other techniques that reduce words to their normalized form, lemmatization utilizes a dictionary to map words back to their original form. For example:

$$closed \rightarrow close$$

$$saw \rightarrow see$$

- **Stemming** Similarly to lemmatization, inflectional endings from a word are removed. In contrast to lemmatization, a set of rules is used instead of a dictionary.

- Part of Speech (POS) Tagging Given a sentence, determine the Part of Speech for each word. Some examples for POS categories include nouns, verbs, adverbs, adjectives, conjunctions, and auxiliary verbs. Words can serve as multiple parts of speech. For example, "book" can be a noun (e.g., "the book on the table") or a verb (e.g., "to book a flight"). "Set" can be a noun, a verb, or an adjective.

#### **Syntactic Analysis**

- Sentence Boundary Disambiguation Given a chunk of text, find the sentence boundaries. Punctuation marks, in e.g. abbreviations, are special cases that need to be handled.

- Parsing This task involves generating a parse tree for a given sentence. A parse tree is an ordered, rooted tree that represents the syntactic structure of a sentence according to the language's grammar. The grammar for natural languages is ambiguous and thus, sentences can have multiple, up to thousands, parse trees. There are two primary types of parsing: dependency parsing and constituency parsing [39]. Dependency parsing focuses on the relationships between words in a sentence (marking things like primary objects and predicates), whereas constituency parsing focuses on building out the parse tree using a probabilistic context-free grammar.

#### Lexical Semantics - Semantics of Individual Words in Context

- Named Entity Recognition (NER) Given a stream of text, determine which items in the text map to proper names, such as people or places, as well as the type of each such name (e.g., person, location, organization). Named entities can span several words.

- Word Sense Disambiguation (WSD) When multiple interpretations for a word are possible, the task of WSD is to select the meaning which makes the most sense in a given context. Given a specific word, a database such as WordNet [40] provides a list of associated word senses. Together with context information, WordNet is often used to infer the correct word sense.

#### Relational Semantics - Semantics of Individual Sentences

- Relationship Extraction Given a piece of text, identify the relationships among named entities, i.e. entities identified via NER.

- Semantic Role Labeling Given a single sentence, identify and disambiguate semantic predicates, then identify and classify the semantic roles. Details are provided in the next subsection.

## **Discourse Semantics - Semantics beyond Individual Sentences**

- Coreference Resolution This task involves identifying words within a text that reference the same entities. An example of this is anaphora resolution, where pronouns are mapped to the corresponding nouns or names to which they refer.

- Topic Segmentation and Recognition Given a chunk of text, separate the text into distinct segments, each centered around a specific topic, and subsequently identify the topic for each segment.

# 2.3.2 Semantic Role Labeling with Proposition Bank Annotations

As mentioned in the above overview, SRL identifies semantic predicates and their associated semantic roles. The following example showcases the need for a semantic analysis:

- "The system starts."

- "The system starts the database."

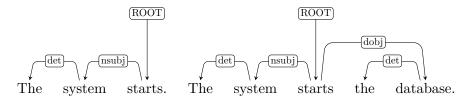

In this example, a syntactical analysis is not sufficient to answer the question "Which entity is started?". Figure 2.5 depicts a dependency parse tree for both sentences.

Figure 2.5: Dependency parse trees for two exemplary sentences.

In both sentences, the verb "to start" is used in active form and constitutes the root of the parse tree. "The system" is identified in both cases as the subject by a syntactical parser. However, only in the first sentence "the system" is the entity that is started. In the second sentence, the object of the sentence, namely "the database", is the entity that is being started. Thus, for the verb "to start", it depends on the semantic interpretation and not syntax of a sentence whether the object or the subject of the sentence contains the entity that is started.

SRL tries to assign specific semantic roles, also referred to as tags or thematic roles, to elements that are related to a predicate. The set of related elements together with the predicate itself are referred to as a predicate argument structure or predicate frame. A semantic role is assigned to each element in the predicate argument structure by the SRL task.

In the example above, SRL identifies "starts" as the predicate. "The system", as well as "the database", are identified as part of the predicate argument structure. Examples are depicted in Figures 2.6 and 2.7. A semantic role, in the given example "Arg1", indicates which entity is started. It is assigned to "the system" in the first sentence and to "the database" in the second sentence.

Figure 2.6: Semantic Role Labeling output from the AllenNLP demo [41].

Figure 2.7: Semantic Role Labeling output from the AllenNLP demo [41].

Semantic roles or tags can, for instance, indicate location, temporal attributes, or the manner in which something is done. In most SRL frameworks, semantic roles follow the ProbBank model [35], which is introduced in the following.

**Proposition Bank (ProbBank)** The ProbBank project and the corresponding model use the Penn Treebank [33] project as a base. In the Penn Treebank project, approximately 2,500 stories comprising 40,000 sentences from the Wall Street Journal were annotated with mainly syntactic information, e.g. subjects and objects of a sentence were identified. The ProbBank project added verb specific semantic annotations to the Penn Treebank corpus via a rule-based automatic tagger. The output of the tagger was manually hand-corrected [35].

Due to the difficulty of defining a universal set of semantic roles covering all types of predicates [35], ProbBank defines semantic roles on a verb-by-verb basis. The roles associated to a verb are also referred to as the verb's arguments. Arguments are numbered,

beginning with zero. In addition to the verb-specific numbered roles, ProbBank defines several general roles that can apply to any verb. These roles describe, for instance, the location or a manner in which an activity is performed. An overview of the core semantic roles defined by the ProbBank model is given in Table 2.2. A predicate together with its possible semantic roles define a so-called frameset. During the definition of the frameset, the authors of the ProbBank model tried to consistently use "Arg0" as the role that exhibits features of an agent, and "Arg1" as the role that exhibits features of a patient.

| Role                           | Description                                                |

|--------------------------------|------------------------------------------------------------|

| Arg0                           | Generally the argument that exhibits features of an agent  |

| Arg1                           | Generally the argument that exhibits features of a patient |

| Arg2 & higher                  | No consistent generalization possible across predicates    |

| ArgM-Adv                       | General adverbials or clause modifiers                     |

| ArgM-Cau                       | Cause                                                      |

| ArgM-Loc                       | Location                                                   |

| $ m ArgM	ext{-}Mnr$            | Manner                                                     |

| ArgM-Mod                       | Modals                                                     |

| ArgM-Neg                       | Negation                                                   |

| ArgM-Ext                       | Extent                                                     |

| ArgM-Dis                       | Discourse connectives                                      |

| $\overline{\mathrm{ArgM-Tmp}}$ | Temporal features                                          |

| ArgM-Prp                       | Purpose or reason                                          |

| ArgM-Dir                       | Directional features                                       |

Table 2.2: Overview of core ProbBank semantic roles.

A predicate can have multiple framesets. For instance, the predicate "to decline" can either carry the meaning of "to reject" or "to go down incrementally". The two respective framesets defined by ProbBank are shown in Figure 2.8.

**Semantic Roles of Commas** While SRL traditionally focuses on semantic roles surrounding predicates, there exists work to analyze the semantic roles surrounding commas. Commas and the surrounding sentence structure often express relations that are relevant to understanding the meaning of a sentence [42]. The following example provided by the authors of [42] illustrates this:

# Example

We invited the computer scientists, Susan and Hannah.

Depending on the interpretation, Susan and Hannah are either a substitute for computer scientists, or the three of them form a list. The authors of [42] have defined 9 relations, shown in Table 2.3, that commas participate in.

# Frameset: decline.01 "go down incrementally"

• Arg1: Entity going down

• **Arg2:** Amount gone down by

• **Arg3:** Start point

• **Arg4:** End point

# Example:

[Arg1 The net income] declined [Arg2 42%] [Arg4 to 121 million] [ArgM-Tmp in the first 9 months of 1989].

# Frameset: decline.02 "demure, reject"

• Arg0: Agent

• Arg1: Rejected thing

## Example:

[Arg0 A spokesman] declined [Arg1 to elaborate].

Figure 2.8: Framesets from ProbBank for the word "decline".

# 2.3.3 Frame Semantic Parsing

A parallel line of work to SRL seeks to extract semantic information from sentences through a process known as Frame Semantic Parsing (FSP). FSP originates from the FrameNet project [43] and is based on a theory of meaning called frame semantics. Similar to the ProbBank project, it was the goal of the FrameNet project to annotate a specific corpus with semantic roles.

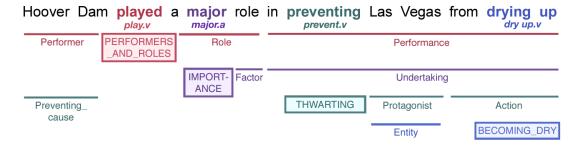

According to frame semantics, the meanings of most words can be understood on the basis of a semantic frame. A semantic frame in the context of FSP describes a type of event, relation, or entity, and the participants, also called frame elements, involved in it. As an example, the concept of cooking can be used [43]. Cooking usually involves a cook, the food that is to be cooked, a container to hold the food while cooking, and a source of heat. The notion of cooking is represented by the semantic frame "apply\_heat" in the FrameNet project. All involved participants such as the cook, food, the source of heat, and container are called frame elements. However, the semantic frame "apply\_heat" can not only be invoked by the predicate "to cook", but also verbs such as "to fry", "to bake", "to boil", or "to broil". All words that invoke a certain frame are called lexical units of the frame. An example for FSP is shown in Figure 2.9.

While in SRL with the ProbBank model, predicates act as the root of a frameset, in FrameNet also nouns, adjectives, adverbs, and prepositions are allowed as lexical units.

| Relation      | Description                                                                              |

|---------------|------------------------------------------------------------------------------------------|

| Substitute    | Indicates an apposition structure                                                        |

| Attribute     | Separates a noun from a non-restrictive/non-essential modifier                           |

| Locative      | Separates elements related to locations or places                                        |

| List          | Separates elements in a list                                                             |

| Introductory  | Separates an introductory element at the start of the sentence from the main clause      |

| Complementary | Separates a complementary element from the main clause                                   |

| Interrupter   | Delimits an interrupter (word, phrase or clause breaking the logical flow of a sentence) |

| Quotation     | Separates a quote                                                                        |

| Other         | Comma that does not fall into any of the other 8 categories                              |

Table 2.3: Semantic roles of commas according to [42].

In the depicted example, "played" invokes the semantic frame "performance\_and\_roles" with the frame elements performer, role, and performance. "Drying up" invokes the frame "becoming\_dry" with one single frame element called entity.

Figure 2.9: Frame Semantic Parsing example from Swayamdipta et al. [44].

In comparison to SRL, FSP and the FrameNet model emphasizes the semantics of a frame that entities are associated with. Subsequently, FSP is more domain dependent. It is essential that semantic frames have been identified and created for events, entities, or relations relevant to the domain of interest. In comparison, for SRL it is sufficient to have framesets defined for the predicates employed in the domain of interest.

In the following, two sentences annotated with ProbBank and FrameNet tags are given. These examples illustrate that ProbBank requires an additional level of inference to determine the meaning of parts of a sentence [35]. Both the lexical units "bought" and "sold" invoke the same frame "Commerce" in the FrameNet model. The buyer as well as the seller is directly identifiable based on the tags. With SRL, it is necessary to look at the different framesets of the predicates "to buy" and "to sell", and identify the buyer

and seller according to their arguments. The relevant ProbBank framesets are shown in Table 2.4.

#### ProbBank:

[Arg0 Chuck] bought [Arg1 a car] [Arg2 from Jerry] [Arg3 for 1000€]. [Arg0 Jerry] sold [Arg1 a car] [Arg2 to Chuck] [Arg3 for 1000€].

#### FrameNet:

[Buyer Chuck] bought [Goods a car] [Seller from Jerry] [Payment for 1000€]. [Seller Jerry] sold [Goods a car] [Buyer to Chuck] [Payment for 1000€].

| Role | buy.01 "purchase" | sell.01 "exchange goods for money" |

|------|-------------------|------------------------------------|

| Arg0 | Buyer             | Seller                             |

| Arg1 | Thing bought      | Thing sold                         |

| Arg2 | Seller            | Buyer                              |

| Arg3 | Price paid        | Money earned                       |

| Arg4 | Benefactive       | Benefactive                        |

Table 2.4: ProbBank Framesets for "to buy" and "to sell".

#### 2.3.4 NLP Frameworks

A range of frameworks and methodologies are available publicly to tackle the challenge of NLP. For the task of SRL or FSP, most recent approaches use a layered deep neural network. Frameworks utilizing the ProbBank model for SRL include CoqComp-NLP [45], AllenNLP [41], and Sling [46]. Frameworks using the FrameNet model include SEMAFOR [47] and Open-Sesame [44]. In general, the NLP community evaluates the performance of a neural network for NLP on certain published tasks or corpora. For SRL, one commonly evaluated dataset comes from the Conference on Computational Natural Language Learning (CoNLL) [48]. In 2004 and 2005, CoNLL provided a training corpus including correct outputs, a development data set to tune the parameters of the learning system, as well as an evaluation data set to test the performance of an SRL framework [49]. In addition to the CoNLL dataset, the OntoNotes [50] dataset is often used for training and evaluation of SRL approaches. The goal of the OntoNotes project was to annotate a large corpus comprising various genres of text (news, weblogs, talk shows etc.) in three languages, including English, with structural information and shallow semantics [51]. For the evaluation of frameworks using FSP and the FrameNet model, the data sets provided by SemEval from 2007 [52] are regularly used.

While results of frameworks for both datasets do have some carry-over to the potential performance for the purpose of extracting semantic information from natural language requirements for software in the automotive industry, the validity is still limited. All approaches have been, to a certain degree, optimized for the published task's datasets and thus also for the domains contained in the respective corpora. For this reason, the frameworks mentioned above have been briefly evaluated in order to make a choice for the implementation of the test generation framework TG-SRL. The evaluation can be found in Section 4.7.1 of Chapter 4.

Semantic Role Labeling with BERT models State-of-the-art SRL results are currently achieved with Bidirectional Encoder Representations from Transformers (BERT) [53]. BERT models are employed in both the CogComp-NLP and AllenNLP frameworks. While previous neural models for SRL relied on lexical and syntactic features such as POS tags or parse trees, BERT makes use of pre-training based on language modeling [54, 55]. The standard SRL task decomposes into four subtasks: first predicates need to be identified, afterwards the predicate sense needs to be identified (predicate sense disambiguation), next arguments for the predicate frame need to be identified and lastly, the arguments need to be classified according to the roles. For the latter three tasks, BERT together with other neural network layers can be utilized. For details of the neural network architecture, the reader is referred to [53].

# 2 Fundamentals

# 3 Related Work

This chapter provides an overview of relevant literature in the field of test generation. Research on model-based testing techniques is very extensive as demonstrated by a survey of Dias et al. [56], which found 219 unique approaches. This chapter primarily focuses on methods that employ some form of Natural Language Processing to extract information from sentences. Methods that solely aim to formalize requirements (e.g., [57, 58]), or those that exclusively generate a formal model from requirements without producing any test cases (e.g., [59, 58]), are outside the scope of this chapter.