Published in partnership with FCT NOVA with the support of E-MRS

https://doi.org/10.1038/s41699-025-00614-9

# Threshold switching in vertically aligned MoS<sub>2</sub>/SiO<sub>x</sub> heterostructures based on silver ion migration

Check for updates

Jimin Lee¹, Rana Walied Ahmad², Sofía Cruces¹, Dennis Braun¹, Lukas Völkel¹, Ke Ran³,4,5, Vasileios Maroufidis Andreadis⁴, Joachim Mayer⁴,5, Stephan Menzel², Alwin Daus¹,6 ⊠ & Max C. Lemme¹,3 ⊠

Threshold switching (TS) is a non-permanent change in electrical resistance controlled by voltage modulation in two-terminal devices. Silver (Ag) filament-based TS has been observed in two-dimensional transition metal dichalcogenides, which are promising due to their van der Waals gaps, facilitating ion migration and filament formation without disturbing covalent bonds. This work demonstrates the heterostructure growth of vertically aligned molybdenum disulfide (VAMoS<sub>2</sub>) with an amorphous silicon oxide (SiO<sub>x</sub>) layer after sulfurization. Ag ion migration through this material stack enables TS. Our Ag/SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au devices exhibit low switching voltages of ~0.63 V, high on-state currents over 200  $\mu$ A, and stable switching exceeding 10<sup>4</sup> cycles. A physics-based dynamical model identifies two rate-limiting steps for filament formation, and the simulated switching kinetics align with experimental results. Our devices achieve fast switching in 311 ns and spontaneous relaxation in 233 ns. These findings advance understanding of switching mechanisms and highlight their potential for memory and neuromorphic computing applications.

Threshold switching (TS), also known as volatile resistive switching (RS), is a phenomenon in which electrical resistance temporarily changes in response to an applied electrical field<sup>1</sup>. TS devices have become highly relevant for emerging technologies, e.g., to be used as memory selectors, as artificial neurons and synapses in neuromorphic computing, and as true random number generators for security applications<sup>2–10</sup>. Memristive devices, typically composed of metal-insulator-metal two terminal structures, have gained attention as promising solutions for compact and energy-efficient technologies in the semiconductor industry<sup>11–14</sup>. They show TS primarily due to filament formation<sup>15–17</sup> achieved by ionic transport<sup>18–20</sup>.

Recently, TS driven by the formation and disruption of conductive filaments from highly diffusive metal electrodes, such as silver (Ag) or copper (Cu) in two-dimensional (2D) materials, has gained considerable attention<sup>21–26</sup>. Reliable volatile RS, including high-speed switching and high endurance, is enabled by thin or weak filaments of the active metal ions in the switching layer<sup>27,28</sup>. The relaxation process, where filaments dissolve due to surface energy minimization or thermal diffusion, is influenced by the properties of the filament and the switching layer<sup>28–31</sup>. Material engineering strategies, such as a defected graphene layer at the Ag/insulator interface,

have also been reported to influence the filament formation process<sup>3,23,32,33</sup>. In addition, the active metals enable the switching dynamics to be modulated by voltage amplitude, pulse duration, and temperature<sup>5,8,23</sup>.

Ag or Cu filamentary threshold switches combined with 2D transition metal dichalcogenides (TMDs) are investigated for advanced brain-inspired neuromorphic hardware with fast switching speeds, high integration density, and low power consumption<sup>15,34–38</sup>. Among the 2D TMDs, molybdenum disulfide (MoS<sub>2</sub>) is one of the most extensively studied switching layers in memristive devices<sup>39</sup>, despite its relatively low bandgap (1.2-2.2 eV, depending on thickness)<sup>40,41</sup>. Monolayer MoS<sub>2</sub>-based memristors have been demonstrated with stable, non-volatile RS while effectively suppressing leakage current<sup>36</sup>. It should be noted that the RS in MoS<sub>2</sub> primarily occurs via field-induced ion migration along van der Waals (vdW) gaps 16,20,42-44 or through grain boundaries and defects<sup>15,18,36,45-47</sup>. These findings suggest that intrinsic structural properties play a more critical role in RS behavior than the bandgap alone. MoS<sub>2</sub> films can be synthesized on wafer scale by thermally assisted conversion (TAC) from molybdenum (Mo) thin films into lateral or vertical MoS<sub>2</sub> layers via sulfurization 42,45,48. Vertically aligned MoS<sub>2</sub> (VAMoS<sub>2</sub>) layers are particularly promising for crossbar architectures,

¹Chair of Electronic Devices, RWTH Aachen University, Aachen, Germany. ²JARA-Fit and Peter Grünberg Institute (PGI-7), Forschungszentrum Jülich GmbH, Jülich, Germany. ³AMO GmbH, Advanced Microelectronic Center Aachen, Aachen, Germany. ⁴Central Facility for Electron Microscopy, RWTH Aachen University, Aachen, Germany. ⁵Ernst Ruska-Centre for Microscopy and Spectroscopy with Electrons, Forschungszentrum Jülich GmbH, Jülich, Germany. ⁶Institute of Semiconductor Engineering, University of Stuttgart, Stuttgart, Germany. ⊠e-mail: alwin.daus@iht.uni-stuttgart.de; max.lemme@eld.rwth-aachen.de

which rely on vertical electrical connections <sup>16,17,20,49</sup>. Their vertically oriented vdW gaps facilitate ion movement between two sandwiched electrodes for RS behavior <sup>16,20,43</sup>. In fact, volatile RS devices based on VAMoS<sub>2</sub> with an Ag active electrode have shown low threshold voltages from 0.18 V to 0.35 V and a high ON-OFF ratio of 10<sup>6</sup> <sup>16,17,21,43</sup>. However, the heterostructure of VAMoS<sub>2</sub> and an oxide layer remains underexplored, particularly regarding its impact on key device parameters such as switching voltages, variabilities, and the underlying switching mechanisms. Moreover, the time-dependent behavior and switching dynamics of such heterostructure-based devices have been rarely studied. More broadly, VAMoS<sub>2</sub>-based and VAMoS<sub>2</sub>/ oxide heterostructure TS devices remain less understood than their widely investigated oxide-based counterparts <sup>3,5,8,50,51</sup>. Increased understanding of the switching dynamics in VAMoS<sub>2</sub>/oxide heterostructure-based RS devices is therefore key for unlocking their potential applications.

In this work, we present TS devices that consist of an amorphous, substoichiometric silicon oxide (SiO<sub>x</sub>) layer on VAMoS<sub>2</sub> below an active Ag electrode. The SiO<sub>x</sub> layer was formed on top of VAMoS<sub>2</sub> during the sulfurization process. We show that Ag ions can travel through the material stack by applying long and short voltage pulses, leading to volatile RS. The switching performance is improved at lower switching voltages with a thinner SiO<sub>x</sub> layer on top of the VAMoS<sub>2</sub> compared to a thicker SiO<sub>x</sub> layer. The switching dynamics are analyzed theoretically using the JART ECM simulation model  $^{52,53}$ , which considers physics-based rate-limiting ionic processes, and are correlated with experimental observations.

#### Results

# Device fabrication and material characterization of SiO<sub>x</sub>/VAMoS<sub>2</sub>-based RS devices

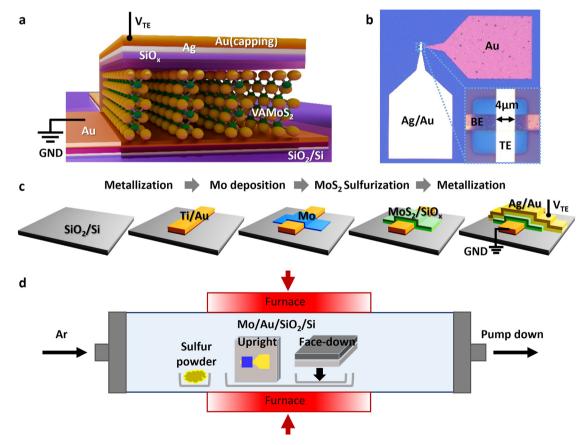

The two-terminal vertical devices studied in this work comprise a stack of SiO<sub>x</sub> and VAMoS<sub>2</sub> layers sandwiched between an active Ag top electrode

(TE) and an inert gold (Au) bottom electrode (BE). Figure 1a, b, respectively, show a schematic of the TS device and an optical microscopy image of the fabricated device with lateral dimensions of 4  $\mu$ m  $\times$  4  $\mu$ m. Figure 1c shows the fabrication process beginning with the preparation of inert Au BEs on Si substrates with 300 nm thermally grown silicon dioxide (SiO<sub>2</sub>) using photolithography, electron-beam evaporation, and lift-off techniques. 6 nm Mo thin films were deposited on the pre-patterned Au BEs and subsequently converted into VAMoS<sub>2</sub> layers by TAC in a sulfur atmosphere in a chemical vapor deposition (CVD) system<sup>20</sup>. We fabricated SiO<sub>x</sub>/VAMoS<sub>2</sub> devices with two different SiO<sub>x</sub> layer thicknesses by placing the substrate either upright against the boat wall for thicker SiO<sub>x</sub> and face-down on two overlapping boats for thinner SiO<sub>x</sub> inside the CVD quartz tube (Fig. 1d). This resulted in 60 nm and 10 nm SiO<sub>x</sub> on top of the VAMoS<sub>2</sub>, as confirmed by ellipsometry. Finally, the active Ag TEs were deposited and structured similarly to the BEs (see Methods and Supplementary Fig. 1 for further details). The growth of the MoS<sub>2</sub> layer with a process-parameter-dependent SiO<sub>x</sub> layer via sulfurization was further demonstrated using non-patterned Mo thin films deposited on SiO<sub>2</sub>/Si substrates, as confirmed by high-resolution transmission electron microscopy (HRTEM) images (Supplementary Fig. 2). The corresponding growth parameters, resulting MoS2 orientations, and SiOx thicknesses are summarized in Supplementary Table 1. The material growth via TAC directly on the device substrate helps avoid defects such as wrinkles and folds, typically introduced during the transfer process of 2D materials<sup>54</sup>. A wrinkle-free surface after the device fabrication was confirmed by atomic force microscopy (AFM), as shown in Supplementary Fig. 3.

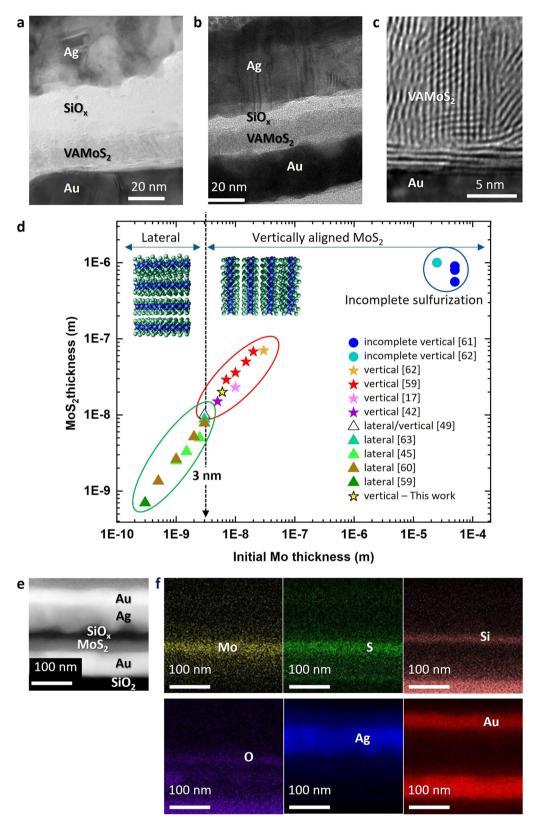

The device compositions and structures were verified using cross-sectional transmission electron microscopy (TEM), which confirmed the presence of an amorphous  ${\rm SiO_x}$  layer on VAMoS<sub>2</sub> between the Ag and Au electrodes (Fig. 2a, b). The vertical orientation of the nanocrystalline MoS<sub>2</sub> layers was further verified by HRTEM (Fig. 2c). The initial few layers formed

Fig. 1 | Ag/SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au device structure and fabrication process. a Schematic drawing of the TS device. b Top-view optical microscopy image of the fabricated device, with the inset showing a zoomed image of the 16  $\mu m^2$  area where the top (TE) and bottom (BE) electrodes intersect. c Schematic of the fabrication

process flow for a RS cross-point device. d Schematic of the sulfurization process for VAMoS<sub>2</sub> film in a horizontal tube furnace, with sulfur powder positioned upstream and sputtered Mo thin film on pre-patterned Au on SiO<sub>2</sub>/Si substrate at the center of the tube.

on the Au surface tend to be laterally oriented, followed by the dominant formation of vertically aligned layers. This transition is attributed to surface alloying, where Mo atoms diffuse near the Au surface during the early stages of sulfurization<sup>55</sup>. In contrast, MoS<sub>2</sub> layers grown directly on the SiO<sub>2</sub>/Si substrate appear predominantly vertically aligned (see Supplementary Fig. 4). Raman analysis was conducted on the as-grown MoS<sub>2</sub> film on the Au BE surface for 60 nm and 10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices (Supplementary Fig. 5). The Raman spectra of the sulfurized MoS<sub>2</sub> films show the characteristic  $E^{1}_{2\sigma}$ and A<sub>1g</sub> peaks at 382 cm<sup>-1</sup> and 407 cm<sup>-1</sup>, respectively, in both devices. The Raman peaks correspond to the in-plane  $(E_{2g}^1)$  and out-of-plane  $(A_{1g})$ vibrational modes, respectively 56,57, and confirm the synthesis of the 2H-MoS<sub>2</sub> phase. The data also provide insight into the vdW layer orientation, as their peak intensity ratio  $(E_{2g}^1/A_{1g})$  of approximately 0.4, observed in both cases, indicates the formation of vertical MoS2 layers, as reported in the literature<sup>58</sup>. The vertical MoS<sub>2</sub> growth from 6 nm Mo thin films is consistent with the literature, where vertical vdW orientation was reported for initial Mo thicknesses exceeding 3 nm (see Fig. 2d for details)<sup>17,42,45,49,59-63</sup>.

The presence of the amorphous  $\mathrm{SiO}_x$  layer was confirmed by high-angle annular dark-field (HAADF) imaging (Fig. 2e) and energy-dispersive X-ray spectroscopy (EDXS) elemental mapping (Fig. 2f) of the 10 nm  $\mathrm{SiO}_x/\mathrm{VAMoS}_2$  device (see Supplementary Fig. 6 for the 60 nm  $\mathrm{SiO}_x/\mathrm{VAMoS}_2$  device). We attribute the  $\mathrm{SiO}_x$  layer formation to atomic diffusion of Si and O from the  $\mathrm{SiO}_2/\mathrm{Si}$  substrate at high temperatures during the Mo sulfurization process  $^{49,64}$ , potentially enhanced by the vdW gaps in the VAMoS $_2$  layer.

#### DC electrical performance

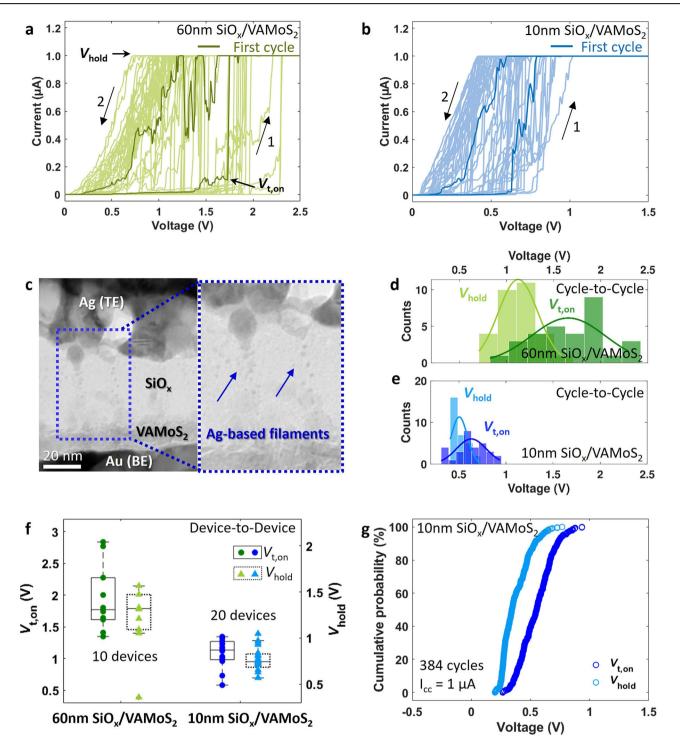

The  ${\rm SiO_x/VAMoS_2}$  devices initially exhibited a high resistance of more than 25 G $\Omega$ , which can be explained by the presence of the insulating  ${\rm SiO_x}$  in the material stack. The RS characteristics of thick (60 nm) and thin (10 nm)  ${\rm SiO_x/VAMoS_2}$  devices were measured by 30 consecutive direct-current (DC) current–voltage (I-V) sweeps with a current compliance of  $I_{\rm CC}$  = 1  $\mu$ A (Fig. 3a, b). Both devices showed abrupt switching from the high resistance state (HRS) to the low resistance state (LRS) at certain positive on-threshold voltages ( $V_{\rm t,on}$ ) applied to the Ag TEs. The LRS was maintained for a positive bias beyond  $V_{\rm t,on}$ . The transition from the LRS back to the HRS occurred during the reverse voltage sweep below the hold voltages ( $V_{\rm hold}$ ). Repeatable volatile RS was observed with an average  $V_{\rm t,on}$  of ~1.66 V for the 60 nm SiO $_x$ /VAMoS $_2$  device and ~0.63 V for the 10 nm SiO $_x$ /VAMoS $_2$  device, demonstrating that a thinner SiO $_x$  layer on VAMoS $_2$  requires a lower switching voltage.

TEM imaging revealed residual traces of Ag in the  $SiO_x$  layer in the HRS (~1 M $\Omega$ ) after 42 switching cycles (Fig. 3c). This suggests that applying a positive voltage to the TE induces Ag diffusion through the switching layer and the formation of a conductive filament bridging the top and bottom electrodes<sup>21</sup>. However, the Ag ions visible in the TEM do not form a complete filament because no external bias was applied during the measurement, and the device is in the HRS. Instead, the conductive filament required for the LRS has partly dissolved and ruptured as the voltage bias was removed due to interfacial energy minimization<sup>17,27</sup>. The volatile switching in our devices is thus governed by the formation and breakage of Ag conductive filaments within the  $SiO_x/VAMoS_2$  stack, enabled by Ag ion movement in the  $SiO_x$  layer and along the vdW gaps of vertically oriented  $MoS_2$  layers. Similar non-volatile switching with ion movement along the grain boundaries has been observed in laterally oriented  $MoS_2$  layers<sup>15,22,36,45</sup>.

We evaluated the variability of the devices based on  $\mathrm{SiO_x}$  thickness by statistically analyzing  $V_{\mathrm{t,on}}$  and  $V_{\mathrm{hold}}$  data from 30 consecutive cycles (Fig. 3d, e). The 60 nm  $\mathrm{SiO_x/VAMoS_2}$  device exhibited larger cycle-to-cycle standard deviations of 0.39 V for  $V_{\mathrm{t,on}}$  and 0.21 V for  $V_{\mathrm{hold}}$ , compared to the 10 nm  $\mathrm{SiO_x/VAMoS_2}$  device with standard deviations of 0.16 V for  $V_{\mathrm{t,on}}$  and 0.09 V for  $V_{\mathrm{hold}}$ , respectively. The thinner  $\mathrm{SiO_x}$  layer on  $\mathrm{VAMoS_2}$  reduces variability and enables lower switching voltages. In addition, we analyzed  $V_{\mathrm{t,on}}$  and  $V_{\mathrm{hold}}$  as a function of cycle number for both device types, which revealed no clear trend with increasing cycles (Supplementary Fig. 7). Additional DC I-V sweeps were performed on multiple devices to quantify

the device-to-device variation. The results are shown in Fig. 3f, which plots  $V_{\rm ton}$  and  $V_{\rm hold}$  of the initial I-V traces of ten 60 nm and twenty 10 nm SiO<sub>x</sub>/ VAMoS<sub>2</sub> devices. The individual *I-V* sweeps corresponding to these data are provided in Supplementary Fig. 8, 9. The 60 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices exhibited standard deviations of 0.53 V for  $V_{t,on}$  and 0.34 V for  $V_{hold}$ , while the 10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices showed lower deviations of 0.21 V for  $V_{\text{t.on}}$  and 0.13 V for  $V_{\text{hold}}$  respectively. The lower cycle-to-cycle and deviceto-device variability in the latter, combined with the lower switching voltages, favors thin SiO<sub>x</sub> layers on VAMoS<sub>2</sub> for applications such as artificial neuron circuits<sup>23</sup>. The cycle-to-cycle variation for the 10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> device was further evaluated using cumulative probability analysis over 384 consecutive cycles (Fig. 3g), with all I-V sweeps for the device plotted in Supplementary Fig. 10. Additionally, a yield was obtained to be 100% for the 60 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices and 95% for 10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices, as detailed in Supplementary Section 10. The yield evaluation in this work is based on the initial functional performance of the devices, and does not include endurance statistics across multiple devices, which will be an important aspect of future studies. It is also noted that our as-grown 2D material fabrication process is transfer-free, effectively avoiding common transfer-related failures such as scratched lines and localized damage<sup>65</sup>.

#### **Pulsed voltage characteristics**

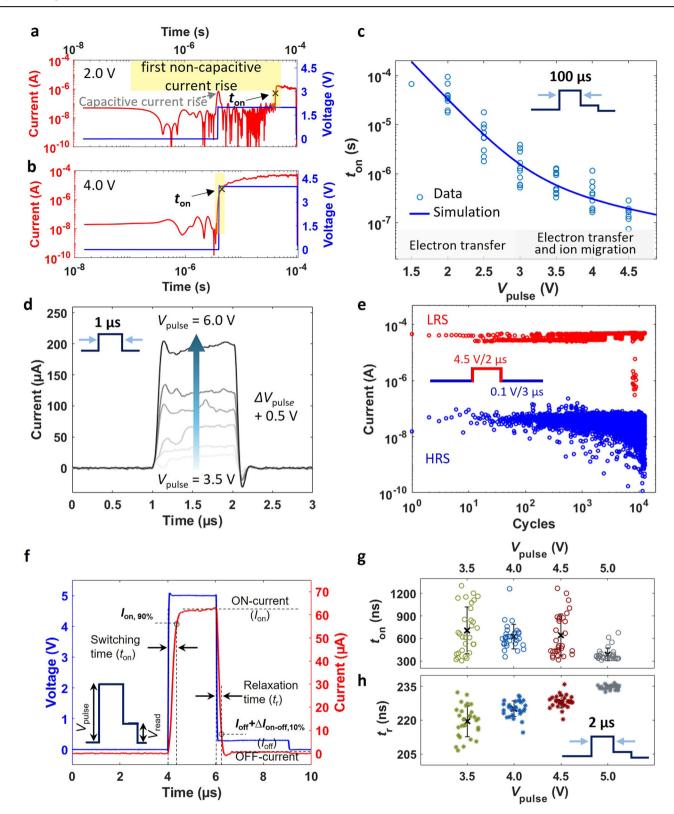

We conducted pulsed voltage measurements to further elucidate the switching dynamics of the 10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub> devices, selected for their favorable DC switching behavior. We analyzed the transient current response to 100  $\mu$ s voltage pulses with amplitudes ranging from  $V_{\text{pulse}} = 1.5 \text{ V}$  to 4.5 V. The pulse width was chosen to capture the switching kinetics and to obtain measurable switching times across this voltage range. The devices switched to the LRS after a certain time which depended on  $V_{\rm pulse}$ . After the pulse, the device returned to the HRS, and the state was read out with a read pulse of 0.3 V for 3 µs. Two typical transient current responses are shown in Fig. 4a, b, while all data is available in Supplementary Fig. 11. Supplementary Figure 12 presents enlarged views, clearly showing the transient from the LRS to the HRS. The on-switching time ( $t_{on}$ ) was determined by extracting the midpoint value of the first significant non-capacitive current rise in the double logarithmic current-time  $(\log(I)-\log(t))$  curves. This midpoint value also represents the steepest slope during this specific transient current rise. Figure 4c shows the extracted  $t_{\rm on}$  values as a function of  $V_{\rm pulse}$ , with an inset illustrating the voltage pulse waveform. As  $V_{\text{pulse}}$  increases, the  $\log(t_{\text{on}})$  decrease is mostly linear. However, at higher  $V_{\rm pulse}$  values, the rate of decrease in  $\log(t_{\rm on})$ reduces, resulting in a progressively flatter  $\log(t_{\rm on})$ - $V_{\rm pulse}$  curve, which indicates reduced sensitivity of the switching time change to further increased voltages. Similar observations were reported in volatile and non-volatile electrochemical metallization devices, where the switching kinetics are divided into three regimes based on the respective ionic rate-limiting step: (I) nucleation limited, (II) electron transfer limited, and (III) electron transfer and ion migration limited<sup>8,52</sup>. Considering these three distinct ionic processes under an applied bias enables a good prediction of switching times as a function of the electrical stimulus. The three processes become rate-limiting at three specific voltage regimes and are, therefore, responsible for the dynamic behavior of the device. Extensive experimental results have confirmed this observation8,52.

We applied a well-established simulation model developed by Menzel et al. and Ahmad et al. \$2,53 to gain a deeper understanding of the physical processes limiting the switching time in our Ag/SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au devices. The full model is explained in Supplementary Section 12. The simulation results are plotted as a solid line with the experimental data in Fig. 4c. The fitting parameters are detailed in Supplementary Table 3. Two distinct regimes are evident from the data: At voltages below 3 V, the sharp linear slope on the logarithmic scale corresponds to the electron transfer-limited regime. Above 3 V, the flatter slope indicates that the rate-limiting factor shifts to a mixed regime of electron transfer and silver ion migration. Therefore, the voltage that drops across the device determines which of the ionic processes is/are the slowest and, thus, rate-limiting. This insight is obtained by analyzing the physics-based model, which describes the transient

Fig. 2 | Cross-sectional analysis of the device structure and material characterization. a, b Cross-sectional TEM images displaying the vertical stack of  $SiO_x/VAMoS_2$  between the top and bottom electrodes for devices with 60 nm (a) and 10 nm (b)  $SiO_x$  layers. The  $VAMoS_2$  thickness is approximately 20 nm in both cases. c An enlarged HRTEM image of  $VAMoS_2$  layers grown on Au. d  $MoS_2$  orientation as a function of initial Mo layer thickness. When the initial Mo

thickness is below 3 nm, laterally aligned  $MoS_2$  layers are formed. As the Mo thickness increases, vertically aligned  $MoS_2$  layers begin to dominate. In the bulk, incomplete sulfurization occurs after a certain amount of vertical layer formation <sup>17,42,45,49,59-63</sup>. **e**, **f** Cross-sectional HAADF image of the 10 nm  $SiO_x/VAMOS_2$  device (**e**), and the corresponding EDXS elemental mapping of the device stack (**f**), showing Mo, S, Si, O, Ag, and Au.

Fig. 3 | DC current-voltage (*I-V*) characteristics of Ag/SiO $_x$ /VAMoS $_2$ /Au devices. a, b 30 *I-V* switching cycles of a 60 nm and a 10 nm SiO $_x$ /VAMoS $_2$  device, respectively. The devices exhibit TS with a positive voltage applied to the Ag top electrode.  $I_{CC}$  was set to 1  $\mu$ A, and arrows 1 and 2 denote the voltage sweep direction. c Cross-sectional TEM image of the device after RS at low HRS after several RS cycles. The dotted blue rectangle is further enlarged on the right, showing Ag traces in the

material stack. **d**, **e** Statistical distribution of switching voltages ( $V_{\rm t,on}$  and  $V_{\rm hold}$ ) for 60 nm and 10 nm  ${\rm SiO_x/VAMoS_2}$  devices, respectively. 30 RS cycles were evaluated per sample, with data extracted from (**a**, **b**). **f** Device-to-device distribution of  $V_{\rm t,on}$  and  $V_{\rm hold}$  for 10 devices with 60 nm  ${\rm SiO_x/VAMoS_2}$  and 20 devices with 10 nm  ${\rm SiO_x/VAMoS_2}$ . **g** Cumulative probability distribution of  $V_{\rm t,on}$  and  $V_{\rm hold}$  in a 10 nm  ${\rm SiO_x/VAMoS_2}$  device over 384 RS cycles.

evolution of the gap between the active electrode and the filament tip and the transient evolution of voltage drops across the various ionic processes<sup>52,53</sup>. The model also includes a nucleation limited regime, which can typically be accessed with rather low voltages applied for rather long pulse durations, but which we did not see in this work's experimental data.

Next, we explored short voltage pulses of  $1\,\mu s$  to switch the  $SiO_x/VAMoS_2$  devices. The voltage-dependent transients in Fig. 4d show a

significant increase in on-state current upon 1  $\mu s$  pulses of different voltages, up to 200  $\mu A$  for 6 V. Such short pulses lead to reduced stress, which typically enhances the device endurance, a key performance parameter for TS devices besides fast switching time and high on-state current. We tested the endurance by applying short 2  $\mu s$  voltage pulses of 4.5 V to switch a device from the HRS to the LRS, then returning it to the HRS, followed by a pulse of 0.1 V for 3  $\mu s$  to read out the off-state current. The 10 nm SiO $_x/VAMoS_2$

Fig. 4 | Pulsed voltage characteristics of Ag/10 nm SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au devices. a, b Transient current response under  $V_{\rm pulse}$  of 2.0 V (a) and 4.0 V (b) with a 100  $\mu$ s duration in double logarithmic scale.  $t_{\rm on}$  is marked with an "x", and the first non-capacitive current rise is highlighted in yellow. The initial capacitive current rise is also indicated with a grey arrow in (a). c Switching kinetics showing experimental data for  $t_{\rm on}$  as a function of  $V_{\rm pulse}$  (blue circles) and fitting data from the numerical simulation (blue solid line). The plot is divided into two regions: electron-transfer-limited and mixed control regimes. The inset displays the voltage pulse waveform.

**d** Transient current response of 1 µs voltage pulses with amplitudes ranging from 3.5 V to 6.0 V ( $\Delta V_{\rm pulse}$ : +0.5 V). e Pulsed endurance showing over  $10^4$  cycles. Inset: programming pulse consisting of 4.5 V/2 µs followed by 0.1 V/3 µs. The LRS and HRS currents were extracted as the average of the values recorded during the second half of the 4.5 V and 0.1 V pulses, respectively. **f** Current response in the time domain under a voltage pulse of 5.0 V/2 µs, followed by a read pulse 0.3 V/3 µs. The inset shows the corresponding voltage pulse waveform. **g**, **h** Statistical distributions of  $t_{\rm on}$  and  $t_{\rm r}$  as a function of  $V_{\rm pulse}$  in a short pulse of 2 µs for 30 repetitions, respectively.

device exhibits stable switching behavior after  $10^4$  cycles with an average ON-OFF ratio of  $10^3$ , as shown in Fig. 4e. Additional DC resistance measurements were taken after every 10 consecutive voltage pulses to further validate the reliability of the device's volatility. The DC resistance values are plotted together with the extracted HRS and LRS resistance values in Supplementary Fig. 13, confirming consistent returns to the HRS after each set of 10 pulses. A pulsed endurance test was also performed without the DC resistance measurements to eliminate any potential influence from them. This device also demonstrated continued robust endurance of ~5800 cycles, with average resistance values of  $166~\rm k\Omega$  for the LRS and  $5~\rm M\Omega$  for the HRS (see Supplementary Fig. 14). Additional endurance results from two other devices are also provided in Supplementary Fig. 14.

Furthermore, we measured  $t_{op}$  and the relaxation time  $(t_r)$  of a 10 nm  $SiO_x/VAMoS_2$  devices as a function of  $V_{pulse}$  for a fixed pulse time of 2 µs over 30 consecutive pulses.  $V_{\rm pulse}$  values between 3.5 V and 5.0 V were chosen, where the switching time is determined by the electron-transfer and ion migration, enabling a rapid transition to the LRS. One example of a measured time-resolved current response to a 5 V pulse is shown in Fig. 4f. Here,  $t_{\rm on}$  is defined as the time required to reach 90% of the LRS ON-current ( $I_{on}$ ).  $t_r$  is defined as the time needed to decay from  $I_{\rm on}$  to 10% of the difference between  $I_{\rm on}$  and the HRS OFF-current  $(I_{\rm off})^{66}$ . All extracted  $t_{\rm on}$  and  $t_{\rm r}$  are plotted in Fig. 4g, h, with the inset in Fig. 4h showing the voltage pulse waveform.  $t_{\rm on}$ decreases slightly with increasing  $V_{\mathrm{pulse}}$ , similar to the behavior observed with the longer voltage pulses of 100 µs. The device then returns to the HRS through a self-relaxation process while the read voltage is applied. Unlike  $t_{\rm on}$ ,  $t_{\scriptscriptstyle

m T}$  increases with higher  $V_{

m pulse}$ . We assume that the stronger electric fields cause the formation of thicker, more robust filaments, which take longer to rupture. This assumption is supported by recent studies on oxide memristive devices  $^{5,31}$ . The relaxation process thus reflects the history of the device, with  $t_r$ revealing whether the formed filament was thick or thin8.

Our  $10 \text{ nm } \text{SiO}_x/\text{VAMoS}_2$  device exhibits a fast switching of  $t_{\text{on}} = 311 \text{ ns}$  and a spontaneous relaxation time of  $t_{\text{r}} = 233 \text{ ns}$  using a voltage pulse of 5 V/2 µs and a read pulse of 0.3 V/3 µs.  $t_{\text{on}}$  and  $t_{\text{r}}$  are critical parameters for operating memristive devices and can be adjusted by the voltage pulse parameters in our devices. The optimization of the operating conditions is required to ensure reliable endurance and accurate device performance. Their tunability can be used for versatile applications in electronics, ranging from selectors for memories to synaptic devices for neuromorphic computing<sup>3-6,8</sup>. Our device shows promise for selector applications, which require high on-state currents and short relaxation times<sup>4,67</sup>. However, there is a tradeoff, as increasing the on-state current tends to increase the relaxation time.

Table 1 compares the TS performance of the present SiO<sub>x</sub>/VAMoS<sub>2</sub> devices with data from previously reported studies in the literature<sup>3,4,17,68,69</sup>. Our devices demonstrate significantly lower switching voltages and faster switching speeds, particularly faster relaxation times, compared to pure SiO<sub>x</sub> or SiO<sub>2</sub>-based devices. Our SiO<sub>x</sub>/VAMoS<sub>2</sub> devices exhibit 10 times higher  $V_{\text{hold}}$  than the SiO<sub>2</sub> devices<sup>69</sup> although they have similar  $V_{\text{t,on}}$ , which implies that weaker Ag filaments are formed. We attribute this to the rapid formation and dissolution of conductive filaments within the switching stack, particularly in the VAMoS<sub>2</sub> layer, where the vdW nature of MoS<sub>2</sub> enables ionic transport but also limits the filament growth. The relaxation time is mainly governed by the material stack, due to spontaneous conductive path rupture driven by atomic and ionic mass transport<sup>29</sup>. The SiO<sub>x</sub> layer is known to promote the formation of strong conductive Ag filaments<sup>70,71</sup>. However, the presence of the VAMoS<sub>2</sub> layer in direct contact with the Au BE appears to suppress this strong filament growth in our SiO<sub>x</sub>/VAMoS<sub>2</sub> devices. When comparing the SiO<sub>x</sub>/VAMoS<sub>2</sub> and SiO<sub>x</sub>-only devices, we found that the incorporation of the VAMoS2 layer leads to more stable switching behavior by the confined formation of filaments. A detailed comparison of their pulsed voltage responses is provided in Supplementary Fig. 15, and the I-V characteristics of the SiO<sub>x</sub>-only device are presented in Supplementary Fig. 16. Our findings highlight the potential to achieve fast switching by integrating a SiO<sub>x</sub> layer with 2D TMDs and provide insight into switching dynamics for volatile RS devices.

Table 1 | Performance comparison of Ag-based threshold switches

| Device                                          | Material growth method                                                             | $V_{t,on}$   | Vhold                  | V <sub>hold</sub> I <sub>ON/OFF</sub> (DC) On-state current | On-state current                  |                 | Enduran<br>(cycles) | e                         | Switching speed |                                | Pulsed voltage (V <sub>pulse</sub> /duration) |

|-------------------------------------------------|------------------------------------------------------------------------------------|--------------|------------------------|-------------------------------------------------------------|-----------------------------------|-----------------|---------------------|---------------------------|-----------------|--------------------------------|-----------------------------------------------|

|                                                 |                                                                                    |              |                        | •                                                           | DC (Icc) AC                       | AC              | DC AC               |                           | Switching time  | Switching time Relaxation time |                                               |

| Ag/SiOx/VAMoS2/Au This work CVD (Sulfurization) | CVD (Sulfurization)                                                                | 0.63 V       | 0.5 V >10 <sup>3</sup> | >10³                                                        | 1 µA                              | 200 µA 384 >10⁴ | 384                 |                           | 311 ns          | 233 ns                         | 4.5 V/2 µs                                    |

| Ag/VAMoS <sub>2</sub> /Au <sup>17</sup>         | CVD (Sulfurization)                                                                | 0.35 V       | 0.1 V 10 <sup>6</sup>  | 10 <sup>6</sup>                                             | 100 µA N/A                        |                 | >30                 | >30 5×10 <sup>6</sup> N/A | N/A             | N/A                            | 1.2 V/50 µs                                   |

| Ag/MoS <sub>2</sub> /Ag <sup>68</sup>           | Aerosol-Jet Printer (Exfoliated flakes ink) $$ 0.18 V-0.3 V $$ 0.13 V $$ 10 $^{5}$ | 0.18 V-0.3 V | 0.13V                  | 10 <sup>5</sup>                                             | 10 µA 1 µA 100 N/A                | 1µA             | 100                 | N/A                       | N/A             | 20 hs                          | 1.0 V/100 µs                                  |

| Ag/DDG*/SiO <sub>2</sub> /Pt³                   | Magnetron sputtering                                                               | 0.6 V        | ı                      | 5 × 10 <sup>8</sup>                                         | 500 µA 500 µA 100 10 <sup>6</sup> | 500 µA          | 100                 |                           | 100 ns          | 1 µs                           | 2.0 V/2 µs                                    |

| Ag/SiO <sub>2</sub> /Au <sup>69</sup>           | N/A                                                                                | 0.7 V        | 0.05 V N/A             | N/A                                                         | 1 mA 40 mA N/A N/A                | 40 mA           | N/A                 |                           | N/A             | 100 µs                         | 1.3 V/1 ms                                    |

| Ag/SiO <sub>x</sub> /C** <sup>4</sup>           | Electron-beam evaporation                                                          | 1.75 V       | 1.5 V 10 <sup>7</sup>  | 107                                                         | 50 µA 15 µA N/A 10 µs             | 15 µА           | N/A                 | N/A                       | 10 µs           | 1 ms                           | 5.0 V/100 µs                                  |

|                                                 |                                                                                    |              |                        |                                                             |                                   |                 |                     |                           |                 |                                |                                               |

#### Discussion

We investigated Ag-based TS using a material stack comprising thin SiO<sub>x</sub> layers on VAMoS<sub>2</sub> in a Ag/SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au configuration. Our devices demonstrated highly repeatable volatile RS at low switching voltages of 0.63 V, with a high on-state current exceeding 200  $\mu$ A for  $V_{\text{pulse}} = 6 \text{ V}$  and robust pulsed endurance over 10<sup>4</sup> cycles. Furthermore, our devices showed fast switching filament formation and dissolution speeds with both switching and relaxation times in a few hundred nanoseconds for  $V_{\text{pulse}} = 5 \text{ V}$ . We analyzed the switching kinetics of the devices using the JART ECM model and identified the experimentally observed physical processes of electron-transfer-limited and electron-transfer/ion migrationlimited switching. The observed SiO<sub>x</sub> thickness and uniformity resulted from our solid source tube furnace setup, which was primarily designed for proof-of-concept studies rather than precise thickness control. While this method confirms the feasibility of growing SiO<sub>x</sub>/VAMoS<sub>2</sub> heterostructures, it lacks the precision achievable with gaseous precursors in industrial fabrication techniques. Nevertheless, these findings advance the understanding of SiO<sub>x</sub>/VAMoS<sub>2</sub>-based RS devices and pave the way for their practical use in emerging memories and neuromorphic computing systems.

#### Methods

# Device fabrication and material growth

The Ag/SiO<sub>x</sub>/VAMoS<sub>2</sub>/Au cross-point devices, with dimensions of  $4 \,\mu\text{m} \times 4 \,\mu\text{m}$ , were fabricated on 300 nm SiO<sub>2</sub>/Si substrates. First, the substrates were cleaned using acetone, isopropanol (IPA) and O2 plasma to remove surface contaminants. Bottom electrodes (BEs) were defined by photolithography (using a Mask aligner EVG420 from EV GROUP) and deposited with a 5 nm titanium (Ti) adhesion layer and a 50 nm Au layer by electron-beam evaporation (Pfeiffer Balzers PLS 500), followed by lift-off in dimethyl sulfoxide (DMSO) heated to 80 °C. Next, a 6 nm thick patterned molybdenum (Mo) film was formed on the BEs by photolithography, direct-current sputtering (CREAMET S2, CREAVAC GmbH), and lift-off. A Mo target with a purity of 99.95% from EVOCHEM was used for the sputtering process. The sputtering was conducted with a power of 100 W under an Ar flow and a chamber pressure of  $\sim 3 \times 10^{-3}$  mbar. The sulfurization process was performed in a chemical vapor deposition (CVD) tube furnace (RS 80/300, Nabertherm GmbH), where the patterned Mo film on Au/SiO<sub>2</sub>/Si substrate was heated in a sulfur atmosphere. This process was conducted at 800 °C for 30 min with an Ar flow rate of 20 sccm as the carrier gas at a pressure of  $9.6 \times 10^{-2}$  mbar to achieve a vertical orientation of the MoS<sub>2</sub> layers. Sulfur powder was placed upstream in the CVD furnace and heated to 150 °C. Sulfur diffused into the Mo film, creating ~20 nm thick MoS<sub>2</sub> layers. Finally, 30 nm Ag top electrodes (TEs) with a 30 nm Au capping layer were deposited using photolithography, electron-beam evaporation, and lift-off processes. The complete fabrication process flow and the sulfurization process are illustrated in Fig. 1c, d. Top-view optical microscopy images of the thick and thin SiO<sub>x</sub>/VAMoS<sub>2</sub> cross-point devices are shown in Supplementary Fig. 1a, b, respectively.

# Material characterization

Transmission electron microscopy (TEM) was employed to investigate the cross-sectional device structure, layer orientation, and chemical composition. TEM lamellae were prepared by focused ion beam (FIB) using an FEI Strata400 system. TEM imaging and energy-dispersive X-ray spectroscopy (EDXS) were conducted by JEOL JEM F200 at 200 kV. Raman spectroscopy was performed on the as-grown  $\rm MoS_2$  layer to analyze the phase formation. The Raman measurement was taken using a WITec alpha 300 R Raman system in mapping mode with a 532 nm excitation laser at 1 mW power and a 1800 g/mm grating.

#### Electrical characterization

Switching properties of the devices were measured at room temperature using a Lakeshore probe station connected to a semiconductor parameter analyzer (Keithley 4200S-SCS from a Tektronix company), equipped with two source measure unit cards (Keithley 4200-SMU) and preamplifiers

(Keithley 4200-PA). A voltage stimulus was applied to the Ag top electrode while the Au bottom electrode was grounded. Under an applied electric field, Ag ions migrate through the material stack, namely the  $\mathrm{SiO}_{x}$  layer and the  $\mathrm{VAMoS}_{2}$  layers, modulating the conductivity. The applied voltage was monitored in parallel on channel 2 from the Ag top electrode, and the output current was measured over time on channel 1 from the Au bottom electrode. For DC current-voltage (I-V) sweep measurements, the voltage was swept from 0 V to a positive maximum 3 V and back to 0 V, with the current limited by an external current limiter within the Keithley 4200-SCS. Pulsed voltage measurements were conducted using the pulse measure units (Keithley 4225-PMUs).

# Data availability

The datasets generated and/or analyzed during this study are available from the corresponding author upon reasonable request.

Received: 15 April 2025; Accepted: 25 September 2025; Published online: 14 October 2025

#### References

- Ielmini, D., Waser, R. & Akinaga, H. Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications. (John Wiley & Sons, Incorporated, 2016).

- Jiang, H. et al. A novel true random number generator based on a stochastic diffusive memristor. Nat. Commun. 8, 882 (2017).

- Zhao, X. et al. Breaking the Current-Retention Dilemma in Cation-Based Resistive Switching Devices Utilizing Graphene with Controlled Defects. Adv. Mater. 30, 1705193 (2018).

- Wang, W. et al. Volatile Resistive Switching Memory Based on Ag Ion Drift/Diffusion Part I: Numerical Modeling. *IEEE Trans. Electron Devices* 66, 3795–3801 (2019).

- Li, Y. et al. High-Uniformity Threshold Switching HfO<sub>2</sub>-Based Selectors with Patterned Ag Nanodots. Adv. Sci 7, 2002251 (2020).

- Nikam, R. D., Rajput, K. G. & Hwang, H. Single-Atom Quantum-Point Contact Switch Using Atomically Thin Hexagonal Boron Nitride. Small 17, 2006760 (2021).

- Zhuo, Y. et al. A Dynamical Compact Model of Diffusive and Drift Memristors for Neuromorphic Computing. Adv. Electron. Mater. 8, 2100696 (2022).

- Chekol, S. A., Menzel, S., Ahmad, R. W., Waser, R. & Hoffmann-Eifert, S. Effect of the Threshold Kinetics on the Filament Relaxation Behavior of Ag-Based Diffusive Memristors. *Adv. Funct. Mater.* 32, 2111242 (2022).

- Alharbi, O. et al. Integration of Ag-based threshold switching devices in silicon microchips. *Mater. Sci. Eng.: R: Rep.* 161, 100837 (2024).

- Zhou, H., Li, S., Ang, K.-W. & Zhang, Y.-W. Recent Advances in In-Memory Computing: Exploring Memristor and Memtransistor Arrays with 2D Materials. *Nano-Micro Lett* 16, 121 (2024).

- Lanza, M. et al. The growing memristor industry. Nature 640, 613–622 (2025).

- Aguirre, F. et al. Hardware implementation of memristor-based artificial neural networks. Nat. Commun. 15, 1974 (2024).

- 13. Zhu, K. et al. Hybrid 2D–CMOS microchips for memristive applications. *Nature* **618**, 57–62 (2023).

- Yuan, Y. et al. On-chip atomristors. *Mater. Sci. Eng.: R: Rep.* 165, 101006 (2025).

- Xu, R. et al. Vertical MoS<sub>2</sub> Double-Layer Memristor with Electrochemical Metallization as an Atomic-Scale Synapse with Switching Thresholds Approaching 100 mV. *Nano Lett.* 19, 2411–2417 (2019).

- Ranganathan, K., Fiegenbaum-Raz, M. & Ismach, A. Large-Scale and Robust Multifunctional Vertically Aligned MoS<sub>2</sub> Photo-Memristors. Adv. Funct. Mater. 30, 2005718 (2020).

- Dev, D. et al. 2D MoS<sub>2</sub>-Based Threshold Switching Memristor for Artificial Neuron. *IEEE Electron Device Lett.* 41, 936–939 (2020).

- Sangwan, V. K. et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS<sub>2</sub>. Nat. Nanotechnol. 10, 403–406 (2015).

- Kalita, H. et al. Artificial Neuron using Vertical MoS<sub>2</sub>/Graphene Threshold Switching Memristors. Sci. Rep. 9, 53 (2019).

- Belete, M. et al. Nonvolatile Resistive Switching in Nanocrystalline Molybdenum Disulfide with Ion-Based Plasticity. Adv. Electron. Mater. 6, 1900892 (2020).

- Dev, D., Shawkat, M. S., Krishnaprasad, A., Jung, Y. & Roy, T. Artificial Nociceptor Using 2D MoS2 Threshold Switching Memristor. *IEEE Electron Device Lett.* 41, 1440–1443 (2020).

- Naqi, M. et al. Multilevel artificial electronic synaptic device of direct grown robust MoS<sub>2</sub> based memristor array for in-memory deep neural network. npj 2D Mater. Appl. 6, 1–9 (2022).

- Nikam, R. D. & Hwang, H. Atomic Threshold Switch Based on All-2D Material Heterostructures with Excellent Control Over Filament Growth and Volatility. Adv. Funct. Mater. 32, 2201749 (2022).

- Ahn, W., Lee, S., Oh, J., Lee, H. & Choi, S.-Y. Crystallinity-Controlled Hexagonal Boron Nitride-Based Memristors for Fully Integrated Reservoir Computing Processors. Adv. Mater. 37, 2413640 (2025).

- 25. Li, Y. et al. Memristors with analogue switching and high on/off ratios using a van der Waals metallic cathode. *Nat. Electron* **8**, 36–45 (2025).

- Chen, S. et al. Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks. *Nat. Electron* 3, 638–645 (2020).

- Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. *Nat. Mater.* 16, 101–108 (2017).

- Wang, W. et al. Surface diffusion-limited lifetime of silver and copper nanofilaments in resistive switching devices. *Nat. Commun.* 10, 81 (2019).

- Wang, Z. et al. Threshold Switching of Ag or Cu in Dielectrics: Materials, Mechanism, and Applications. Adv. Funct. Mater. 28, 1704862 (2018).

- Bousoulas, P. et al. Investigating the origins of ultra-short relaxation times of silver filaments in forming-free SiO<sub>2</sub>-based conductive bridge memristors. *Nanotechnology* 31, 454002 (2020).

- Chekol, S. A., Menzel, S., Waser, R. & Hoffmann-Eifert, S. Strategies to Control the Relaxation Kinetics of Ag-Based Diffusive Memristors and Implications for Device Operation. *Adv. Electron. Mater.* 8, 2200549 (2022).

- Jiang, J., Yang, P., Liou, J. J., Liao, W. & Chai, Y. Defect engineering of two-dimensional materials towards next-generation electronics and optoelectronics. *Nano Res* 16, 3104–3124 (2023).

- Kang, Y. et al. Conductive dendrite engineering of single-crystalline two-dimensional dielectric memristors. *The Innovation* 6, 100885 (2025).

- Wang, M. et al. Robust memristors based on layered two-dimensional materials. *Nat. Electron.* 1, 130–136 (2018).

- Shi, Y. et al. Electronic synapses made of layered two-dimensional materials. *Nat. Electron.* 1, 458–465 (2018).

- Ge, R. et al. Atomristor: Nonvolatile Resistance Switching in Atomic Sheets of Transition Metal Dichalcogenides. *Nano Lett.* 18, 434–441 (2018).

- Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. *Nat. Commun.* 13, 1392 (2022).

- Kaniselvan, M., Jeon, Y.-R., Mladenović, M., Luisier, M. & Akinwande,

D. Mechanisms of resistive switching in two-dimensional monolayer and multilayer materials. *Nat. Mater.* 24, 1346–1358 (2025).

- Wells, R. A. & Robertson, A. W. Molybdenum Disulfide Memristors for Next Generation Memory and Neuromorphic Computing: Progress and Prospects. Adv. Electron. Mater. 10, 2400121 (2024).

- Yazyev, O. V. & Kis, A. MoS<sub>2</sub> and semiconductors in the flatland. Mater. Today 18, 20–30 (2015).

- Ryou, J., Kim, Y.-S., Kc, S. & Cho, K. Monolayer MoS<sub>2</sub> Bandgap Modulation by Dielectric Environments and Tunable Bandgap Transistors. Sci. Rep. 6, 29184 (2016).

- Belete, M. et al. Dielectric Properties and Ion Transport in Layered MoS<sub>2</sub> Grown by Vapor-Phase Sulfurization for Potential Applications in Nanoelectronics. ACS Appl. Nano Mater. 1, 6197–6204 (2018).

- Lehenkari, T., Huang, S.-D., Kordas, K. & Komsa, H.-P. Firstprinciples study of Ag, Au, Cu, and Li defects in MoS<sub>2</sub> and their application to memristors. *Phys. Rev. Mater.* 9, 014001 (2025).

- Ran, K. et al. Unraveling the dynamics of conductive filaments in MoS<sub>2</sub>-based memristors by operando transmission electron microscopy. *Nat Commun.* 16, 7433 (2025).

- Gu, Y. et al. Sulfurization Engineering of One-Step Low-Temperature MoS<sub>2</sub> and WS<sub>2</sub> Thin Films for Memristor Device Applications. Adv. Electron. Mater. 8, 2100515 (2022).

- Ganeriwala, M. D. et al. Effect of grain boundaries on metal atom migration and electronic transport in 2D TMD-based resistive switches. *Nanoscale* 17, 13797 (2025).

- Lan, S. et al. Advancing High-Performance Memristors Enabled by Position-Controlled Grain Boundaries in Controllably Grown Star-Shaped MoS<sub>2</sub>. Nano Lett. 24, 15388–15395 (2024).

- Choi, W. et al. Recent development of two-dimensional transition metal dichalcogenides and their applications. *Mater. Today* 20, 116–130 (2017).

- Krishnaprasad, A. et al. MoS<sub>2</sub> Synapses with Ultra-low Variability and Their Implementation in Boolean Logic. ACS Nano 16, 2866–2876 (2022).

- Franco, M. et al. Inkjet printed IGZO memristors with volatile and nonvolatile switching. Sci. Rep. 14, 7469 (2024).

- 51. Jeon, Y.-R., Akinwande, D. & Choi, C. Volatile threshold switching and synaptic properties controlled by Ag diffusion using Schottky defects. *Nanoscale Horiz* **9**, 853–862 (2024).

- Menzel, S., Tappertzhofen, S., Waser, R. & Valov, I. Switching kinetics of electrochemical metallization memory cells. *Phys. Chem. Chem. Phys.* 15, 6945–6952 (2013).

- Ahmad, R. W. et al. Variability-aware modeling of electrochemical metallization memory cells. *Neuromorph. Comput. Eng.* 4, 034007 (2024).

- Chen, W., Gui, X., Yang, L., Zhu, H. & Tang, Z. Wrinkling of twodimensional materials: methods, properties and applications. *Nanoscale Horiz* 4, 291–320 (2019).

- Ma, R. et al. Direct Integration of Few-Layer MoS<sub>2</sub> at Plasmonic Au Nanostructure by Substrate-Diffusion Delivered Mo. Adv. Mater. Interfaces 7, 1902093 (2020).

- Verble, J. L. & Wieting, T. J. Lattice Mode Degeneracy in MoS<sub>2</sub> and Other Layer Compounds. *Phys. Rev. Lett.* 25, 362–365 (1970).

- 57. Li, H. et al. From Bulk to Monolayer MoS<sub>2</sub>: Evolution of Raman Scattering. *Adv. Funct. Mater.* **22**, 1385–1390 (2012).

- Kong, D. et al. Synthesis of MoS<sub>2</sub> and MoSe<sub>2</sub> Films with Vertically Aligned Layers. Nano Lett. 13, 1341–1347 (2013).

- Jung, Y. et al. Metal Seed Layer Thickness-Induced Transition From Vertical to Horizontal Growth of MoS<sub>2</sub> and WS<sub>2</sub>. Nano Lett. 14, 6842–6849 (2014).

- Lee, Y. et al. Synthesis of wafer-scale uniform molybdenum disulfide films with control over the layer number using a gas phase sulfur precursor. *Nanoscale* 6, 2821–2826 (2014).

- 61. Shokhen, V. et al. On the impact of Vertical Alignment of MoS<sub>2</sub> for Efficient Lithium Storage. Sci. Rep. **7**, 3280 (2017).

- Stern, C. et al. Growth Mechanisms and Electronic Properties of Vertically Aligned MoS<sub>2</sub>. Sci. Rep. 8, 16480 (2018).

- Krishnaprasad, A. et al. Graphene/MoS<sub>2</sub>/SiO<sub>x</sub> memristive synapses for linear weight update. npj 2D Mater. Appl. 7, 1–8 (2023).

- Liu, H., Iskander, A., Yakovlev, N. L. & Chi, D. Anomalous SiO<sub>2</sub> layer formed on crystalline MoS<sub>2</sub> films grown on Si by thermal vapor sulfurization of molybdenum at elevated temperatures. *Mater. Lett.* 160, 491–495 (2015).

- Migliato Marega, G. et al. A large-scale integrated vector-matrix multiplication processor based on monolayer molybdenum disulfide memories. *Nat. Electron.* 6, 991–998 (2023).

- 66. Cruces, S. et al. Volatile MoS<sub>2</sub> Memristors with Lateral Silver Ion Migration for Artificial Neuron Applications. *Small Sci.* **5**, 2400523 (2025).

- 67. Zuo, W. et al. Volatile threshold switching memristor: An emerging enabler in the AloT era. *J. Semicond.* **44**, 053102 (2023).

- Feng, X. et al. A Fully Printed Flexible MoS<sub>2</sub> Memristive Artificial Synapse with Femtojoule Switching Energy. Adv. Electron. Mater. 5, 1900740 (2019).

- Zhao, Y. et al. A Compact Model for Drift and Diffusion Memristor Applied in Neuron Circuits Design. *IEEE Trans. Electron Devices* 65, 4290–4296 (2018).

- Yu, D. et al. Multilevel resistive switching characteristics in Ag/SiO<sub>2</sub>/Pt RRAM devices. in 2011 IEEE International Conference of Electron Devices and Solid-State Circuits 1–2 (2011).

- Sun, H. et al. Direct Observation of Conversion Between Threshold Switching and Memory Switching Induced by Conductive Filament Morphology. Adv. Funct. Mater. 24, 5679–5686 (2014).

# **Acknowledgements**

This research was supported by the German Federal Ministry of Education and Research (BMBF) through NEUROTEC2 (16ME0398K, 16ME0399 and 16ME0400) and NeuroSys as part of the initiative "Clusters4Future" (03ZU1106AA, 03ZU1106AB) projects, by the European Union's Horizon Europe research and innovation program via CHIPS-JU under the ENERGIZE project (101194458), and by the Deutsche Forschungsgemeinschaft (DFG) within the project MEMMEA in SPP 2262 MemrisTec (441918103) and the Emmy Noether Programme (506140715).

#### **Author contributions**

M.C.L. and A.D. conceived and designed the concept and supervised the project. J.L. carried out the material growth, characterization, device fabrication, and electrical measurements. J.L., S.C., D.B., and L.V. analyzed the electrical data and characteristics. R.W.A. performed the JART ECM simulations, and R.W.A. and S.M. supported the analysis of the electrical data. K.R. and V.M.A. conducted the TEM and EDSX analyses under the supervision of J.M.; J.L. prepared the initial

manuscript draft, and all authors contributed to its revision and finalization. All authors have read and approved the final version of the manuscript.

# **Funding**

Open Access funding enabled and organized by Projekt DEAL.

# **Competing interests**

The authors declare no competing interests.

# **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41699-025-00614-9.

**Correspondence** and requests for materials should be addressed to Alwin Daus or Max C. Lemme.

Reprints and permissions information is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2025