© © 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

## All CVD Boron Nitride Encapsulated Graphene FETs

H. Pandey<sup>1</sup>, M. Shaygan<sup>2</sup>, S. Sawallich<sup>3</sup>, S. Kataria<sup>1</sup>, M. Otto<sup>2</sup>, Z. Wang<sup>2</sup>, M. Nagel<sup>3</sup>, D. Neumaier<sup>2</sup>, M.C. Lemme<sup>1,2</sup>

<sup>1</sup>Chair of Electronic Devices, RWTH Aachen University, Otto-Blumenthal-Str. 2, 52074 Aachen, Germany <sup>2</sup>AMO GmbH, Advanced Microelectronics Center Aachen, Otto-Blumenthal-Str. 25, 52074 Aachen, Germany <sup>3</sup>Protemics GmbH, Otto-Blumenthal-Str. 25, 52074 Aachen, Germany Email: <a href="mailto:lemme@amo.de">lemme@amo.de</a> / Phone: +49 (241) 8867-200

Graphene is at the forefront of 2D material research, with many reports demonstrating the possibility of large area growth by means of chemical vapor deposition (CVD) [1]–[3]. Boron Nitride (BN) has been suggested to be the favorable substrate and encapsulation material for graphene devices as it preserves the intrinsic mobility performance [4]–[6]. However, the demonstration of BN-encapsulated graphene field effect transistors (GFETs) is so far limited to devices made from manually exfoliated flakes. Here, we report on CVD grown GFETs encapsulated by CVD grown BN with CMOS compatible nickel (Ni) edge contacts to the channel and discuss their performance.

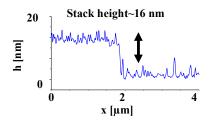

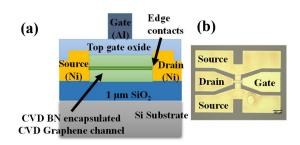

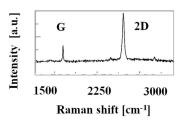

CVD graphene grown on copper (Cu) foils was obtained from Graphenea while CVD BN on Cu foils was obtained from Graphene Supermarket. The CVD BN/graphene/BN (BN/G/BN) stack was fabricated using successive transfer and fishing steps after etching Cu with FeCl<sub>3</sub>. AFM and Raman scans were performed to assess the thickness and quality of the stack. The total stack was ~16 nm thick (Fig. 1) and the encapsulated graphene showed typical G and 2D band signatures (Fig. 2). No characteristic Raman peak for hBN was found, suggesting an amorphous-like nature of the CVD grown BN. The BN was patterned with CHF<sub>3</sub> plasma while the graphene channel was etched in O<sub>2</sub> plasma by reactive ion etching (RIE). Edge contacts with sputtered Ni were deposited as described in [7]. 20 nm atomic layer deposited Al<sub>2</sub>O<sub>3</sub> dielectric and 100 nm evaporated Al formed the top-gate stack (Fig. 3 (a)). An optical micrograph of a fabricated GFET in coplanar waveguide layout is shown in Fig. 3 (b).

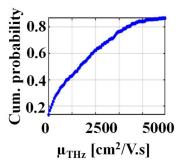

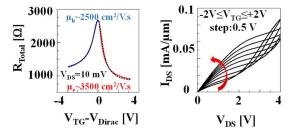

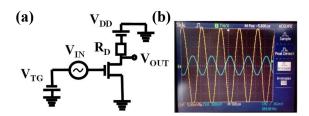

Devices were electrically characterized in a Cascade probe station connected to an HP 4155B semiconductor parameter analyzer under ambient conditions. **Fig. 4** (a) shows the gate voltage dependent device resistance of a GFET with gate length ( $L_G$ ) = 10  $\mu$ m and channel width (W) = 20  $\mu$ m. To extract field effect mobility ( $\mu_{FE}$ ) and contact resistance ( $R_C$ ), the curve was fitted using the model described in [8]. Electron and hole mobilities of  $\mu_{FE}$  = 3500 and 2500 cm<sup>2</sup>/Vs and  $R_C$  value of ~2 k $\Omega$ µm were observed. **Fig. 4** (b) shows the quasi-saturating output characteristics of the same device. The entire BN/G/BN stack was also characterized prior to patterning using non-contact near field terahertz (THz) spectroscopy for measuring the sheet resistance ( $R_{SH}$ ) and mobility values of the graphene [9]. **Fig. 5** shows the cumulative probability distribution of the extracted THz mobility ( $\mu_{THz}$ ) extracted from the spectral THz transient response of the sample. The median of  $\mu_{THz}$  was ~1500 cm<sup>2</sup>/Vs, while the average  $\mu_{THz}$  was ~2500 cm<sup>2</sup>/Vs, which is in very good agreement with the electrical measurements. The average  $R_{SH}$  was ~500  $\Omega$ /sq. The devices were further characterized as voltage amplifiers in a resistive load scheme amplifier circuit (**Fig. 6** (a)). A 1 kHz input voltage signal was applied to the gate and the output voltage was monitored with a high impedance oscilloscope. Several devices were characterized in this configuration and the best voltage gain was measured to be approximately 6 dB for an applied offset gate-voltage of 3V at device dimensions of  $L_G$  = 10  $\mu$ m and W = 10  $\mu$ m (**Fig. 6** (b)).

In conclusion, we present all CVD BN/G/BN FETs which yield average mobility values of 2500 cm²/Vs,  $R_{SH}$  in the range of ~500  $\Omega$ /sq and  $R_{C}$  ~ 2 k $\Omega$ µm. Voltage gain of 6 dB is measured for these devices when configured in a low frequency signal amplifier circuit. These devices are the first demonstrations of such "all CVD" GFETs, with good mobility and voltage gain performance under ambient conditions. These results also demonstrate the graphene encapsulation properties of CVD BN, as the mobility does not degrade during device fabrication compared to conventional  $SiO_2$  and device operation was possible under ambient condition. These results indicate the potential for future scalable and CMOS compatible all-2D devices and circuit architectures.

Acknowledgements: Finding by EU Graphene Flagship (696656) and DFG (LE 2440/2-1, LE 2440/3-1) and RF measurement support by R. Negra and A. Noculak are greatly appreciated.

[1] K. S. Kim et al., Nature, vol. 457, pp. 706–710 (2009) [2] A. Reina et al., Nano Res, vol. 2, pp. 509–516, (2009) [3] S. Kataria et al., phys. stat. sol. (a), vol. 211, pp. 2439–2449, (2014) [4] C. Oshima et al., J. Phys.: Condens. Mat., vol. 9, p. 1, (1997). [5] I. Meric et al., in IEEE IEDM, p. 23.2.1-23.2.4 (2010) [6] C. R. Dean et al., Nat Nano, vol. 5, pp. 722–726, (2010) [7] M. Shaygan et al., Ann. der Phys., vol. 529, p. 1600410, (2017) [8] S. Kim et al., App. Phys. Lett., vol. 94, p. 062107, (2009) [9] M. Nagel et al., Advanced Photonics 2015 paper SeM2D.5, (2015).

© © 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

**Fig. 1:** AFM scan showing the total stack height observed to be around 16 nm (7-8 nm thick CVD BN on each side of the encapsulated CVD graphene)

Fig. 3: (a) Cross sectional schematic of the device showing CMOS compatible edge contacts to graphene in this work. (b) Optical micrograph of typical final device in coplanar waveguide layout indicating source, drain and gate terminals.

**Fig. 5:** Cumulated probability distribution of extracted THz mobility calculated based on noncontact THz mapping carried out on the CVD BN/G/BN stack prior to device fabrication. Median of mobility values is  $\sim 1500$  cm<sup>2</sup>/V.s while average mobility is  $\sim 2500$  cm<sup>2</sup>/V.s.

**Fig. 2:** Raman data showing that the stack formation does not deteriorate the quality of graphene (clear G & 2D peaks present), nonetheless, no sharp peak for BN was observed around 1370 cm<sup>-1</sup> suggesting amorphous-like nature of BN films.

**Fig. 4:** (a) Low bias resistance of one GFET ( $L_G$ =10 μm, W=20 μm) as a function of top-gate voltage. Best fit to a model described in [8] gave electron and hole mobility values of 3500 cm<sup>2</sup>/V.s and 2500 cm<sup>2</sup>/V.s respectively. Dirac voltage  $V_D$ =0.12 V for this device. (b) Quasi-saturating output characteristics of the all-CVD BN encapsulated GFET ( $L_G$ =10 μm, W=20 μm).

Fig. 6: (a) Simple schematic of a low frequency voltage signal amplifier circuit with resistive load scheme, used to assess the voltage gain performance of these devices; a load resistance ( $R_{\rm D}$ ) of 10  $k\Omega$  was mounted on the drain end. (b) Screen shot of Oscilloscope showing the highest measured voltage gain of ~6 dB at 1 kHz for a device with  $L_{\rm G}{=}10~\mu m$  and W=10  $\mu m$  respectively; applied signal is shown in blue while amplified output signal is shown in yellow on the screen. The applied AC input voltage was 20  $mV_{PP}$  and the measured output voltage was 40  $mV_{PP}$ .